Fターム[5J030CC00]の内容

音質制御、圧縮伸張、振幅制限 (2,281) | 振幅制限回路要素 (264)

Fターム[5J030CC00]の下位に属するFターム

増幅器 (83)

ダイオード (60)

トランジスタ (38)

ハイパスフィルタ (1)

スイッチ回路 (17)

導波管、マイクロ波線路 (15)

サーキュレータ (3)

デジタル演算回路、デジタル比較器 (35)

Fターム[5J030CC00]に分類される特許

1 - 12 / 12

振幅制限増幅回路

【課題】差動出力信号間のオフセット電圧を充分に抑圧し、出力信号のデューティ比の悪化を防ぐこと。

【解決手段】差動振幅制限増幅器30と、該差動振幅制限増幅器の出力差動信号をオフセット電圧抑制のために前記差動振幅制限幅器の入力側にフィードバックする差動アクティブ・ローパスフィルタ回路40とを備える。

(もっと読む)

電力制限回路

【課題】希望周波数帯域外の放射レベルを許容範囲内に抑え、平均電力とバックオフの損失を可能な限り抑制する電力制限回路を提供する。

【解決手段】入力信号の電力値を算出する電力計算部11と、算出された電力値と、予め設定された閾値とを比較する閾値比較部12と、算出した電力の包絡線から極大点と極大値を検出するピーク検出部13と、閾値と前記極大値から求めたスケーリング係数を備え、形状パラメータ計算部18によって算出された形状パラメータと併せてカイザー窓を生成する窓関数生成部14と、入力信号を所定時間遅延させる遅延部15と、遅延させた入力信号と窓関数とを乗算する乗算部16と、乗算結果から希望の周波数帯域外の放射レベルを測定する帯域外レベル計測部17と、測定された帯域外放射レベルから窓関数の形状パラメータを算出する形状パラメータ計算部とを備える電力制限回路。

(もっと読む)

瞬時応答振幅制限増幅回路

【課題】入力信号にノイズがのった場合でも、ダイナミックレンジが取れる瞬時応答振幅制限増幅回路の提供する。

【解決手段】入力信号と該入力信号をデータの1ビット以下だけ遅延した遅延信号との差信号を差動増幅回路2A,2B,2Cで増幅し、該差動増幅回路2A,2B,2Cの出力をそれぞれヒステリシス比較回路3A,3B,3Cに入力し、しきい値と比較する。該ヒステリシス比較回路3A,3B,3Cの出力の内の1つを選択回路5で選択する。振幅検出回路4は、ヒステリシス比較回路3A,3B,3Cの信号有りを示す出力の内から、最も利得が小さい経路で増幅された出力が選択回路5で選択されるような選択信号を出力する。

(もっと読む)

音量調整装置、音量調整方法及びプログラム

【課題】 音声データの音量を適切に自動調整することができる音量調整装置を提供すること。

【解決手段】 区間データ取得部14は、音声を示す音声データから前記音声の一部区間を示す区間データを取得し、FFT部16、補正部18、基準スペクトル記憶部20及び逆FFT部22は、取得される前記区間データに対して聴感補正処理を施し、聴感補正済み区間データを生成する。振幅最大倍率算出部24及び増幅率決定部24は、聴感補正済み区間データが示す音声の振幅に基づいて、区間データに適用する増幅率を決定する。その後、増幅部28は、決定される前記増幅率により区間データに対して増幅処理を施す。

(もっと読む)

電流コンバート回路

【課題】オペアンプ構成の電流コンバート回路において、使用温度が高くても小さな電流信号を大きな電圧信号に変換できるようにする。

【解決手段】電流を電圧に変換するオペアンプ構成の電流コンバート回路において、オペアンプに接続される帰還回路を、少なくとも、帰還抵抗と、発光ダイオードとで構成する。

(もっと読む)

送信機の振幅リミッタ回路

【課題】電波形式ごとの切替が可能で、且つリミッタの制限値及び応答速度が調整可能な送信機の振幅リミッタ回路を提供する。

【解決手段】FPGAによるIF段でのデジタル信号処理の中にIFリミッタ23を設ける。上記IFリミッタ23は、IF信号が入力されると、乗算器33でリミッタゲインGを乗じて入力信号の振幅を制御する。乗算器33の出力信号の絶対値を絶対値回路35により取り出し、比較器36に入力して振幅制限値保持部37に保持されている振幅制限値と比較する。比較器36の比較結果を乗算器38に入力し、係数設定回路39にて選択された係数μatt又はμrecと乗算し、リミッタゲインGとしてピーク制限回路40を介して乗算器33に与える。係数設定回路39は、入力の絶対値が振幅制限値を上回っているかどうかを判断し、上回っていれば係数μattを選択し、下回っていれば係数μrecを選択する。

(もっと読む)

デジタルオーディオ信号処理用記録媒体及びデジタルオーディオ信号用の通信方法並びにデジタルオーディオ記録媒体

【課題】 入力信号の遅延時間を短くしてエコーを防止し、アタック時間を長くする。

【解決手段】 デジタルオーディオ信号のレベルに基づきコンプレス/リミット用のゲインを生成するゲイン生成処理4とゲイン生成処理4により出力されたコンプレス/リミット用のゲインに時定数を付与するスムーズフィルタ処理5を設けている。スムーズフィルタ処理5は付与された時定数でゲインを従来例より比較的急峻に下げ、スムーズフィルタ処理5により付与されるゲインの時定数が時定数延長処理6により延長され、ゲイン調整処理2に設定される。また、コンプレス/リミット処理プログラムや、このプログラムにより処理されたオーディオ信号がネットワークNWを介して伝送される。

(もっと読む)

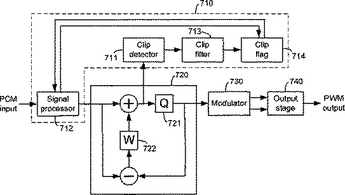

クリップ検出と信号変調システム及び方法

音響信号のクリッピング状態を検出し、その信号をクリッピング状態を低減するように処理するシステム及び方法。一実施例では、システムは、ノイズ波形器、変調器、出力ステージ、及びその他の部品を具える。検出器は、ノイズ波形器のクリッピングを検出し、信号プロセッサは、検出器から受信したフィードバックに基づいてノイズ波形器への音響信号入力を処理する。信号プロセッサは、検出器で検出した様々な状態に応じて様々な方法で入力音響信号を変形するように機能する。フィルタが、信号プロセッサに提供される前に検出器の出力につながるフィルタに含まれていてもよい。フラグ回路がフィルタと信号プロセッサに接続されていてもよく、信号プロセッサがフラグ回路をリセットする前に出力信号を表明する。  (もっと読む)

(もっと読む)

振幅制限回路

【課題】音声信号の振幅が大幅に制限されても、歪み感の少ない再生音が得られる音声信号をつくり出すことによって音響機器のみかけ性能を高め、音声信号を扱うあらゆる機器の能力向上を計る。また、同様の手法で人の耳が聞き易い形の音声信号をつくり出し、補聴器や録音機等の音質向上を計る。

【解決手段】 音声信号の特定周波数以上の信号を除き、振幅が特定レベルを越えようとすると、そのレベルを越えないようにバイアスを変化させて振幅制限を行う。特定周波数以上を振幅制限の範囲に含めないのは耳障りな高調波の発生を少なくするためである。

(もっと読む)

クランプ回路及びこれを備えた半導体装置

【課題】 トランジスタのベース・エミッタ間の電圧に温度特性の差などによる変動が生じた場合でも適正なクランプ動作が可能なクランプ回路を提供する。

【解決手段】 入力端子Tiからの信号ラインにエミッタが接続されたNPNトランジスタQ1と、このNPNトランジスタQ1のベースに供給されるバイアス電流Ibをオン/オフするMOSFETMP1を備える。そして、信号ラインの電圧がコンパレータQ3により閾値より高いと判定されたときはMOSFETMP1を遮断してNPNトランジスタQ1をオフにし、クランプ機能を停止する。また、信号ラインの電圧がコンパレータQ3により閾値より低いと判定されたときはMOSFETMP1をオンにし、NPNトランジスタQ1をオンさせてクランプ電流を供給する。

(もっと読む)

電流電圧変換回路およびそれを用いた光ピックアップ装置

【課題】高出力の光を受光した場合のオペアンプの飽和を防止し、かつリミットを任意に設定できる電流電圧変換回路を提供する。

【解決手段】本発明の回路では、フォトダイオード2に光が入射し、光電流Iが発生すると、カレントミラー回路9を介し、抵抗4、5で決まるミラー比倍の電流がオペアンプ1に入力される。この際、抵抗4では光電流Iによって電圧降下が発生するが、この値がリミット用トランジスタ8の動作し始める電圧、例えば0.7V以下ならばリミッタ機能は働かない。しかし、光電流Iが大きくなり、抵抗4での電圧降下が、トランジスタ8の動作し始める電圧に達すると、トランジスタ8がオンしてコレクタに電流が流れ始め、フォトダイオード2で発生した光電流IをGNDに流すことにより、アンプ1への入力電流にリミットがかかる。

(もっと読む)

リミッタ回路

【課題】 回路規模が小さく、クリップ精度が高く、しかも、大きな容量のコンデンサを必要としないリミッタ回路を提供する。

【解決手段】 制御端子30にクリップ電圧として例えば+2Vを加えると、この電圧+2VはFET28のソースに加えられると共に、オペアンプ31の−入力端へ加えられ、オペアンプ31から電圧−2Vが出力され、FET23のソースへ加えられる。この状態において、入力端子21の入力信号が−2V〜+2Vの範囲にある場合は、FET25、26が共にオフとなり、回路が入力信号に影響を与えることはない。入力信号が+2V以上になると、FET26のソース電圧がゲート電圧より高くなり、FET26がオン状態となり、入力信号が+2Vでクリップされる。また、入力信号が−2V以下になると、FET25のソース電圧がゲート電圧より低くなり、FET25がオン状態となり、入力信号が−2Vでクリップされる。

(もっと読む)

1 - 12 / 12

[ Back to top ]