Fターム[5J030CC02]の内容

音質制御、圧縮伸張、振幅制限 (2,281) | 振幅制限回路要素 (264) | 増幅器 (83) | 差動増幅器 (28)

Fターム[5J030CC02]に分類される特許

1 - 20 / 28

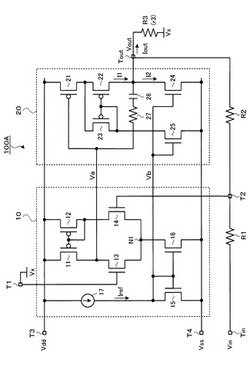

増幅回路

【課題】構成を簡素化し温度特性を向上し消費電流を低減する。

【解決手段】増幅回路100Aにおいて、差動増幅部10は正入力端子T1と負入力端子T2とに供給される電圧の差分を増幅して得た差分電圧Vaと基準電圧Vbとクランプ出力部20に出力する。クランプ出力部20において、PMOS22のソースはPMOS21のドレインと接続され、そのドレインは出力端子Toutと接続される。また、NMOS24において、そのソースには第2電源電圧Vssが供給され、そのゲートには基準電圧Vbが供給され、そのドレインは出力端子Toutに接続される。PMOS22の駆動能力はNMOS24の駆動能力の2倍である。

(もっと読む)

高線形性信号処理増幅器

【課題】高線形性信号処理増幅器を提供する。

【解決手段】クランプポイント能動回路が提供される。クランプポイント能動回路は、少なくとも2つのレベル間で遷移する装置から出力を受信するように構成されたレート増幅器を含む。クランプポイント能動回路は、レート増幅器から出力を受信するように構成された少なくとも1つのスイッチ素子を有する。少なくとも1つのスイッチ素子は、レート増幅器の少なくとも1つのそれぞれのフィードバックループにある。少なくとも1つのスイッチ素子のスイッチングは、レート増幅器に、所望の動作範囲で高い線形性をもって増幅させ、所望の動作範囲の外にある遷移装置から受信された出力を一定レベルに固定させる。

(もっと読む)

アナログ入力モジュール保護装置

【課題】アナログ入力モジュールを過電圧から保護すること。

【達成手段】本発明の保護装置は、複数のプラス/マイナスアナログ信号の電圧レベルがアナログ入力モジュールのプラス/マイナス動作電圧よりも大きい場合、前記複数のプラス/マイナスアナログ信号の電圧を前記アナログ入力モジュールに供給する安定化部を含む。

(もっと読む)

振幅制限増幅回路および光受信器

【課題】少ない消費電力で振幅制限増幅回路を動作させる。

【解決手段】振幅制限増幅回路LAにおいて、主増幅回路12で、光信号Pinを光電変換して得られた電気信号Poutに含まれる各パルスを一定振幅に増幅し、光信号断検出回路14で、電気信号Poutに基づいて光信号Pinの信号断を示す光信号断検出信号LOSを生成し、主電流源回路22で、主増幅回路12の動作に用いる電流Is2を当該主増幅回路12へ供給するとともに、光信号断検出信号LOSに基づいて当該電流Is2の供給制御を行う。

(もっと読む)

デュアルレート振幅制限増幅回路

【課題】高感度、低消費電力、低コストのデュアルレート振幅制限増幅回路を提供する。

【解決手段】入力バッファ120と10Gbps用のアンプブロック200と1Gbps用のアンプブロック210とを同一のチップ(LAIC)101に搭載する。入力バッファ120は、差動入力端子P1から入力される差動信号の正相を正相信号、差動入力端子P2から入力される差動信号の逆相を逆相信号として出力する。この正相信号および逆相信号をLAIC101上で分岐してともに10Gbps用のアンプブロック200と1Gbps用のアンプブロック210へ与える。10Gbps用のアンプブロック200を直列に接続された複数のアンプ(10Gbps用のアンプ)150で構成し、1Gbps用のアンプブロック210を直列に接続された複数のアンプ(1Gbps用のアンプ)160で構成する。1Gbps用のアンプ160では、10Gbps用のアンプ150に比べ回路電流I0,I1を小さく設定する。

(もっと読む)

振幅制限増幅回路

【課題】差動出力信号間のオフセット電圧を充分に抑圧し、出力信号のデューティ比の悪化を防ぐこと。

【解決手段】差動振幅制限増幅器30と、該差動振幅制限増幅器の出力差動信号をオフセット電圧抑制のために前記差動振幅制限幅器の入力側にフィードバックする差動アクティブ・ローパスフィルタ回路40と、からなる回路を、2段以上に亘って縦続接続したて構成する。

(もっと読む)

電圧印加回路およびそれを用いた半導体検査装置

【課題】帰還ループを有する出力アンプを用いて対象物に電圧を供給する電圧印加回路では、出力アンプの出力電流をクランプする電流クランプ部とは独立に動作する出力制御部を用いて電流がクランプされたことを検出し、帰還ループを無効にしていた。このため、電流クランプ部と出力制御部の動作点がずれて、クランプの切り替え点で動作が不安定になるという課題があった。本発明はこの課題を解決することを目的にする。

【解決手段】電流クランプ部で出力アンプの出力電流をクランプ電流以下にクランプすると共に、帰還ループを無効にする信号を出力するようにした。また、電流クランプ部内の増幅器の帰還経路に配置されているダイオードとしてフォトカプラあるいはフォトMOSリレーを用い、帰還ループを無効にする信号を生成するようにした。電流クランプと帰還ループの無効を1つの回路で行うので、切り替え点がずれて動作が不安定になることがなくなる。

(もっと読む)

振幅制限増幅回路

【課題】差動入力を可能とし、入力される信号電力の損失を低減させる。

【解決手段】外部入力端子1に入力側が接続された平均値検出回路5Aと、非反転入力端子が外部入力端子1に接続され、反転入力端子が平均値検出回路5Aの出力側に接続された差動型振幅制限増幅回路4Aと、外部入力端子2に入力側が接続された平均値検出回路5Bと、非反転入力端子が外部入力端子2に接続され、反転入力端子が平均値検出回路5Bの出力側に接続され、差動出力端子対が差動型振幅制限増幅回路4Aの差動出力端子対に対して同相の組合せで並列接続された差動型振幅制限増幅回路4Bとを備える1段目差動増幅回路3A、および1段目差動増幅回路3Aの差動出力端子対の一方の端子に入力側が接続された平均値検出回路5Cと、非反転入力端子が平均値検出回路5Cの出力側に接続され、反転入力端子が1段目差動増幅回路3Aの差動出力端子対の他方の端子に接続された差動型振幅制限増幅回路7とを備える2段目差動増幅回路6を有する。

(もっと読む)

出力電圧制限機能を具備した増幅器

【課題】 増幅器の帰還路にツェナダイオードを挿入し、この増幅器の出力に電圧制限をかけていたので、ツェナダイオードのツェナ電圧の誤差によって制限電圧がばらつき、かつシャープな特性が得られなかったという課題を解決する。

【解決手段】 差動回路の一方に増幅器の出力を入力し、他方に定電圧を入力して、この差動回路の出力電流を増幅器に帰還するようにした。また、増幅器の出力を分圧して差動回路に入力するようにした。増幅器の出力電圧を、差動回路に入力する所定の定電圧で正確に制限することができ、かつシャープな肩特性を得ることができるという効果がある。また、増幅器の出力を分圧して差動回路に入力することにより、電源電圧の極近くの電圧で電圧制限をかけることができるという効果もある。

(もっと読む)

振幅制限増幅回路

【課題】同符号連続耐性と応答時間の短縮と残留オフセット電圧の抑圧とを同時に実現する。

【解決手段】バースト先頭においてはフィードフォワード型オフセット補償回路により瞬時にオフセットを補償し、その後フィードバック型オフセット補償回路によりフィードフォワード型オフセット補償回路で生じる長期的なオフセット変動を補償する。フィードフォワード型オフセット補償回路によるバースト先頭でのオフセット補償時には、フィードバック型オフセット補償回路のアナログスイッチ41をオフ、アナログスイッチ42をオンしておき、時定数の小さいローパスフィルタ22を必要な電圧に急速充電させる。この後オフセット補償回路のキャパシタへの瞬時的な充電が完了するタイミングで、アナログスイッチ41をオンしてローパスフィルタ22の出力電圧を差動増幅器13に入力させるとともに、時定数の大きなローパスフィルタ21を帰還ループに加える。

(もっと読む)

振幅制限増幅回路

【課題】差動出力信号間のオフセット電圧を充分に抑圧し、出力信号のデューティ比の悪化を防ぐこと。

【解決手段】差動振幅制限増幅器30と、該差動振幅制限増幅器の出力差動信号をオフセット電圧抑制のために前記差動振幅制限幅器の入力側にフィードバックする差動アクティブ・ローパスフィルタ回路40とを備える。

(もっと読む)

エネルギー検出受信器の入力信号の圧伸のシステム及び方法

【解決手段】装置は、入力信号に応じて、出力信号についての定義されたダイナミック・レンジを得るための圧伸器として構成される。特に、装置は、入力信号から、第1のダイナミック・レンジ(例えば、第1の感度及び第1の圧密点)を有する第1の信号を生成するように適合された第1の回路、及び入力信号から、第1の信号の第1のダイナミック・レンジとは異なる第2のダイナミック・レンジ(例えば、第2の感度及び第2の圧密点)を有する第2の信号を生成するように適合された第2の回路を有する。装置は、第1及び第2の信号の合計に関する出力信号を生成するように適合された第3の回路を更に含み得る。第1及び第2のダイナミック・レンジを調整することで、圧伸装置の出力信号についての全てのダイナミック・レンジは、得られ得る。 (もっと読む)

信号電圧を制限する回路装置及び方法

【課題】信号処理装置の処理ステージの上流側において信号電圧を制限する回路装置及び方法を提供することであり、その回路装置及び方法により信号干渉を減少させる。

【解決手段】出力信号(Vin′)の閉ループ制御内に電圧比較(OPAMP2)が設けられており、その閉ループ制御によって、前記出力信号(Vin′)の値は最大値(Vmax/2)へ制限される。従って、信号処理期間中において信号干渉の発生を防止することが可能となる。電圧制限方法は、基準量として、閉ループ制御の文脈において出力信号(Vin′)が比較される基準電圧(Vmax/2)を使用する。この閉ループ制御の閉ループ制御逸脱信号が可変抵抗分圧器コンポーネント(T1)を制御し、該コンポーネントにおいて、例えば、直接的にピックアップすることにより電圧降下として出力信号(Vin′)が形成される。

(もっと読む)

バッファ回路、増幅回路、および、試験装置

【課題】出力信号の信号レベルを、設定されるクランプ電圧に応じて精度よく制御するバッファ回路を実現する。

【解決手段】入力信号に応じた信号を出力するバッファ回路であって、入力信号をベース端子に受け取る第1受信トランジスタと、エミッタ端子およびコレクタ端子が第1受信トランジスタの対応する端子に接続され、バッファ回路が出力する信号レベルを制限する第1クランプ電圧をベース端子に受け取る、第1受信トランジスタと同一極性の第1クランプトランジスタと、第1受信トランジスタおよび第1クランプトランジスタに対して共通に設けられ、第1受信トランジスタおよび第1クランプトランジスタに流れるエミッタ電流の総量を規定する第1電流規定部とを備え、第1受信トランジスタのエミッタ電圧に応じた出力信号を出力するバッファ回路を提供する。

(もっと読む)

振幅制限増幅回路

【課題】前段の基本増幅段への入力信号波形が充分に急峻でない場合にも、デューティ変動補正効果が得られるようにする。

【解決手段】入力データ信号の平均値を生成する平均値検出回路と、該平均値検出回路の出力を一方の入力端子に接続した差動型振幅制限増幅器とを有する基本増幅段を前後2段縦続接続した振幅制限増幅回路において、前段の基本増幅段10の出力データ信号の立上り時間と立下り時間を鈍らせるための波形調整回路30,40を前記前段の基本増幅段10と後段の基本増幅段20との間に接続する。

(もっと読む)

パワー検出回路および振幅制限回路

【課題】入力信号のオフセットレベルによらず、振幅に比例したパワーを検出する。

【解決手段】入力信号の振幅を予め決まった所定の範囲内の振幅に変換し、前記入力信号の振幅に比例した振幅の信号を出力するレベル安定化回路20と、該レベル安定化回路20の出力信号を基準値とを比較するパワー検知回路30とを備える。レベル安定化回路20は、容量結合により前記入力信号を取り込み振幅を予め決まった所定の範囲内の振幅に変換する入力レベル変換回路と、該入力レベル変換回路の出力信号を取り込みその平均値を検出する平均値検出回路と、前記入力レベル変換回路の出力信号と前記平均値検出回路の出力信号の差分を増幅する差動増幅回路とからなる。

(もっと読む)

インタフェース回路および信号出力調整方法

【課題】伝送路の減衰量を考慮して送信側の信号の振幅を調整することのできるインタフェース回路および信号出力調整方法を得ること。

【解決手段】インタフェース回路100の送信側回路部分では、テスト時に一定振幅の繰り返し信号111をCML回路で構成される出力バッファ回路117を経て伝送路123に送出する。受信側回路部分102では、これによる入力信号131の振幅を判定回路135が複数の基準電圧Vref1〜Vrefnとコンパレータ1321〜132nで比較することにより求める。そして送信側回路部分101側の電圧制御回路119で、CML回路の定電流値を適切に制御することで振幅の設定を行って低消費電力化を実現する。

(もっと読む)

レファレンス電圧発生回路とそれを用いた電圧増幅器

【課題】高速応答性に優れたレファレンス電圧回路を用いて、種々の信号振幅を持つ入力信号を一定の振幅まで増幅できる電圧増幅器を提供する。

【解決手段】レファレンス電圧発生回路7において、第1の期間ではスイッチSW1のみをOFFにして、入力信号Inの最大ピーク値Vmaxが第1の容量1のノードAに保持される。次の第2の期間では、スイッチSW2、SW3も開放されて、前記最大ピーク値Vmaxと最小ピーク値Vminとの差電圧が容量列4のノードCに保持される。この時、第1の容量1の保持電圧に容量列4の第2の容量2の保持電圧が加算されて、ノードBの電圧がレファレンス電圧Vrefとして出力される。差動増幅回路6の一方の入力端子には入力信号Inが与えられ、他方の入力端子には前記レファレンス電圧Vrefが与えられる。前記ノードA、Cの保持電圧が安定した時点でレファレンス電圧Vrefが発生する。

(もっと読む)

受光回路

【課題】従来の受光回路は、増幅率を変更すると回路の各種特性が変動する問題があった。

【解決手段】本発明にかかる受光回路は、制御電圧Vcont1、Vcont2を出力する電流コントロール電圧生成回路10と、第1の基準電流Ia1と入力電流Ipdとを加算した第1の入力電流Ii1を制御電圧Vcont1、Vcont2の電圧差に応じて調整して第1の出力電流Io1を生成する第1の電流調整回路11と、第2の基準電流Ia2を第1の制御電圧Vcont1、Vcont2の電圧差に応じて調整した第2の出力電流Io2を生成する第2の電流調整回路12と、第1の出力電流Io1を第1の抵抗Rf1に基づき電圧に変換して第1の出力電圧Vo1を生成し、第2の出力電流Io2を第2の抵抗Rf2に基づき電圧に変換して第2の出力電圧Vo2を生成する電流電圧変換回路13とを有するものである。

(もっと読む)

オペアンプのリミッタ回路

【課題】オペアンプに内蔵されるリミッタ回路において、オペアンプの出力電圧を任意の電圧に制限できるようにすることである。

【解決手段】PNPトランジスタQ6のベースには、直列接続されたトランジスタQ8、Q9が接続され、トランジスタQ8のエミッタには上限値Vupと等しい電圧が印加されている。出力段のPNPトランジスタQ7のベース電圧が上昇して、上限値VupからPNPトランジスタのエミッタ・ベース間の電圧降下を引いた電圧より大きくなると、トランジスタQ6がオンし、トランジスタQ7のベース電圧がそれ以上大きくならないように制限される。これにより、トランジスタQ7の出力電圧Voutが上限値Vupに制限される。

(もっと読む)

1 - 20 / 28

[ Back to top ]