Fターム[5J039BC04]の内容

Fターム[5J039BC04]の下位に属するFターム

ヒステリシスを持つもの

Fターム[5J039BC04]に分類される特許

1 - 4 / 4

クロック生成回路および撮像装置

【課題】シュミットトリガー回路と同様な機能を有し、シュミットトリガー回路と比較して貫通電流を低減する。

【解決手段】インバータ回路INV1は、前段回路の回路閾値よりも低い第1の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第1の回路閾値に応じた第1の出力信号を出力する。インバータ回路INV2は、前段回路の回路閾値よりも高い第2の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第2の回路閾値に応じた第2の出力信号を出力する。スイッチ回路SWは、第1の出力信号および第2の出力信号が入力され、第1の出力信号および第2の出力信号の論理状態が、異なる状態から同じ状態に変化したときに、異なる論理状態に対応した第1の電圧および第2の電圧のいずれか一方を出力クロックとして出力する。

(もっと読む)

デジタル信号入力装置

【課題】動作が安定するとともに、後段に接続されるCMOSのLSIの安定な動作を実現するデジタル信号入力装置を提供する。

【解決手段】外部から入力された信号を増幅する増幅部と、前記増幅部で増幅された信号を波形整形する波形整形部と、オフセット電圧を保持するコンデンサと、前記波形整形部の出力をハイレベル状態に固定するように、前記コンデンサの充電と放電を制御して前記オフセット電圧を決定する制御部とを備える。

(もっと読む)

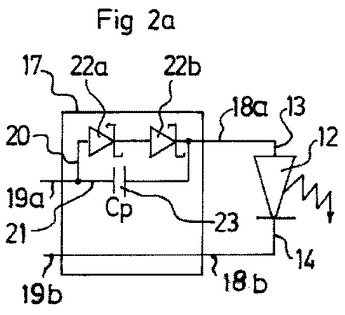

光電素子の超高速駆動用受動素子回路

本発明は、光電素子の超高速駆動回路において、時間400ps以下のエッジを有する電圧矩形波の発生器、ならびに、光電素子の電源端子(13)に直列に接続するように適合された出力、および、電圧矩形波発生器に接続され、そこで形成される電圧矩形波を受け取る入力を備える制御パルス成形回路(17)を含み、前記入力端子と前記出力端子の間に、ゼロでない閾値電圧を有する受動整流回路(22a、22b)からなる第1の分岐(20)であって、その受動整流回路(22a、22b)が第1の分岐内において直列をなし、光電素子の前記電源端子(13)に対して順方向をなす第1の分岐(20)と、第2の容量性分岐(21)とが互いに並列につながれていることを特徴とする駆動回路に関する。  (もっと読む)

(もっと読む)

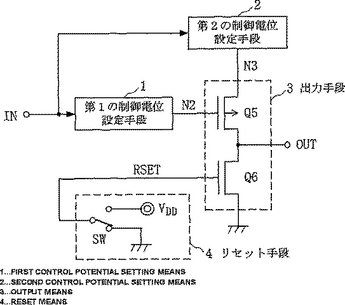

波形整形回路

第1の制御電位設定手段(1)は入力信号(IN)が論理閾値の近傍に達したときに第2の制御電位(N3)との大小関係が逆転する第1の制御電位(N2)を生成する。第2の制御電位設定手段(2)は、入力信号(IN)の変化に応じて入力信号(IN)と同方向に変化する第2の制御電位(N3)を生成する。出力手段(3)は、トランジスタ(Q5,Q6)からなり、第1の制御電位(N2)と第2の制御電位(N3)とリセット信号(RSET)とに基づいて所定の電位の出力信号(OUT)を生成する。リセット手段(4)は、波形整形回路の動作時にトランジスタ(Q6)をオフにする。  (もっと読む)

(もっと読む)

1 - 4 / 4

[ Back to top ]