Fターム[5J039JJ03]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 入力信号特性 (318) | 幅 (8)

Fターム[5J039JJ03]に分類される特許

1 - 8 / 8

半導体集積回路

【課題】分周信号を検査するにあたって、その周波数のみならず第1区間長および第2区間長をも検査し、比較対象に用いる信号を生成する高価な検査装置を必要としない自己診断回路を有する半導体集積回路およびその検査方法を提供する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

(もっと読む)

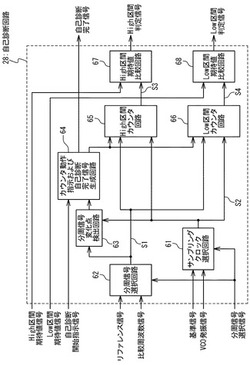

クロック異常検出回路

【課題】クロック異常を検出する精度を向上させる技術を提供する。

【解決手段】被検査クロックを遅延させる第1の遅延回路の出力と第2の遅延回路の出力よりLow期間を決める。定められたLow期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。第1の遅延回路の出力と第2の遅延回路の出力よりHigh期間を決める。定められたHigh期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。Low期間の異常とHigh期間の異常を統合する。

(もっと読む)

デューティ比補正回路及びデューティ比補正方法

【課題】非同期信号のデューティ比を補正可能なデューティ比補正回路を提供すること。

【解決手段】本発明に係るデューティ比補正回路は、第1クロック信号が入力されるクロック用入力バッファと、補正信号に基づいて、前記クロック用入力バッファから出力される第2クロック信号のデューティ比を調整して第3クロック信号を生成するクロック用デューティ調整回路と、第1データ信号が入力されるデータ用入力バッファと、前記補正信号に基づいて、前記データ用入力バッファから出力される第2データ信号のデューティ比を調整して第3データ信号を生成するデータ用デューティ調整回路と、前記第3クロック信号に基づいて、前記補正信号を生成するデューティ比較回路と、を備えるものである。

(もっと読む)

パルス幅測定方法および回路

【課題】入力パルスのデューティが測定可能となり、回路構成が簡素化できるようにする。

【解決手段】HレベルとLレベルとを繰り返す入力パルスを同一遅延時間でn+1段に亘って遅延させてn+1相の遅延パルスを生成し、該n+1相の各遅延パルスのそれぞれがHレベルであるかLレベルであるかに応じて変化し、且つ所定のタイミングにおいて、前記入力パルスのHレベル側又はLレベル側のパルス幅を示すエンコード信号を生成し、前記所定のタイミングにおける前記エンコード信号を、前記Hレベル側又はLレベル側のパルス幅信号として保持する。

(もっと読む)

半導体装置

【課題】テスト中に所望の位相に対して追随できるテスト回路を備え、安価にDDRifのテストを行うことを目的としている。

【解決手段】本発明における半導体装置は、位相シフト量を決定するDLL200と、テストモード時に所定位相ずらす演算回路300と、位相シフト量を設定するレジスタ11〜16と、設定した位相にシフトして信号の送受信を行う伝送回路10とを備える。伝送回路10は、第1の信号を設定した位相にシフトする位相シフタ1と、テストモード時に第1の信号をループバックする双方向バッファ21と、双方向バッファ21から出力された信号の位相をシフトする位相シフタ2と、第3の信号の位相をシフトする位相シフタ3と、テストモード時に第3の信号をループバックする双方向バッファ22と、双方向バッファ22から出力された信号の位相をシフトする位相シフタ4と、位相シフタ2,4の出力信号を取り出すFIFO30とを備える。

(もっと読む)

デジタル型ヘリウム−ネオン安定化レーザ

【目的】 安定化のために、デジタル量を用いる安定化ヘリウム−ネオンレーザの高度の安定度をうるため、デジタルのパルスの形状を正確に揃える手段の提供を行なうと共に、前記安定化のためのデジタル量のパルスの周波数を正確に一定にする手段の提供を行なうことを目的とする。

【構成】

レーザから安定化のために使用出来るデジタル量のパルス周波数を、基準周波数を完全に、しかも安定に一致させるため、ダイオードの順方向の電圧を利用して、正負のパルスの基線を零ボルトにし、さらに、このデジタル量をアナログ量に変換する際、F/V変換回路と正負のパルスの電荷をゆっくり積分する回路を並列にして誤差信号の値を完全に零にしている。

(もっと読む)

パルス信号測定装置及び方法

【課題】パルス信号の入力及びオーバーフローの双方について割り込み信号を発生するタイマを用いてパルス信号の幅や周期を正確に測定可能なパルス信号測定方法を提供する。

【解決手段】リロードレジスタへリロードすると共に割り込み信号を出力し、カウント値がオーバーフローした場合にはリロードレジスタへリロードせずに割り込み信号を出力すると共にオーバーフローフラグをオン状態にするタイマを用いてパルス幅又は周期を測定する際に、割り込み信号を受けてリロードレジスタのカウント値を読み出し(ステップST1)、タイマのオーバーフローフラグの状態を判別し(ステップST2)、オーバーフローフラグがオンしている場合に、リロードレジスタから読み出した今回値と前回値との比較に基づいてパルス信号の入力の有無を判断する(ステップST6)。

(もっと読む)

対称性時間/電圧変換回路

本発明は、時間/電圧変換回路に関し、前記時間/電圧変換回路は、構造的に互いに同一であり、その各々がそれぞれの論理制御信号UpおよびDwnを受ける入力部、ならびに論理制御信号VupおよびVdwnの継続時間を表す対応する電圧を与える出力部を有する2つの単純な時間/電圧変換器CTT1およびCTT2と、各々が当該単純な変換器CTT1およびCTT2に接続されている正302および負304の入力部ならびに2つの制御信号UpおよびDwnの間の電圧の差を表す信号Vdiffを与える出力部をもつ微分器ブロックBE2とを備える。微分器ブロックBE2からの出力Vdiffは、積分器ブロックBE3に接続されている。  (もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]