Fターム[5J039JJ11]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 主たる比較部 (286) | 二安定素子によるもの (109)

Fターム[5J039JJ11]の下位に属するFターム

Fターム[5J039JJ11]に分類される特許

1 - 16 / 16

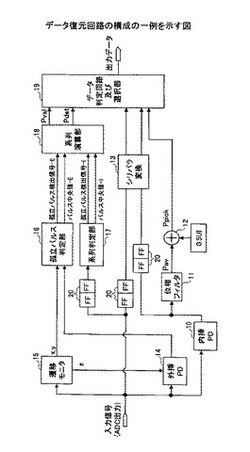

データ復元回路及びデータ復元方法

【課題】孤立パルスを確実に検出してデータ判定を実行できるデータ復元回路を提供する。

【解決手段】データ復元回路は、デジタルデータの列のうち2つの連続するデジタルデータを用いて、内挿により第1のデータ切り替わり点の位置を算出すると共に、外挿により第2のデータ切り替わり点の位置を算出する位相検出器と、第1のデータ切り替わり点の平均位置と瞬時位置とに基づいてデジタルデータの列からデータ判定値の列を抽出するデータ判定部と、2つの連続するデジタルデータに挟まれた時間軸上の区間の内に、直前の2つの連続するデジタルデータの外挿直線及び直後の2つの連続するデジタルデータの外挿直線からそれぞれ求めた2つの第2のデータ切り替わり点が位置し且つ2つの外挿直線の傾きの符号が互いに異なる場合、データ判定値の列の当該区間に対応するデータ判定値を、外挿により推定されるデータ値で置き換えるデータ選択部を含むことを特徴とする。

(もっと読む)

時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システム

【課題】測定精度および分解能を向上させることができる時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システムを提供すること。

【解決手段】時間デジタル変換器は、開始信号と停止信号との間の遅延時間に対応する第1の値を生成する第1遅延列回路を備える。時間デジタル変換器は、また、遅延開始信号と停止信号との間の遅延時間に対応する第2の値を生成する少なくとも一つの第2遅延列回路を備える。少なくとも一つの遅延素子は開始信号に所定の遅延を与えることにより遅延開始信号を生成し、合成回路は、第1の値および第2の値に基づく出力値を生成する。実施形態に係る時間デジタル変換器では、出力値は開始信号と停止信号との間の遅延時間に対応する。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

集積回路及び位相制御方法

【課題】分周クロック信号とクロック信号との位相関係を適応的に制御可能な集積回路を提供する。

【解決手段】集積回路は、第1のクロック信号を分周して第2のクロック信号を生成する分周回路と、第1のクロック信号が伝搬する第1の信号伝搬経路と、第2のクロック信号が伝搬する第2の信号伝搬経路と、第1の信号伝搬経路を伝搬後の第1のクロック信号に第2の信号伝搬経路を伝搬後の第2のクロック信号を少なくとも2回掛け合わせることにより出力信号を生成するミキサ回路と、ミキサ回路の出力信号の直流成分を検出する直流検出回路と、直流検出回路が検出した直流成分に応じて第1の信号伝搬経路及び第2の信号伝搬経路の少なくとも一方の伝搬遅延量を制御する制御回路とを含む。

(もっと読む)

信号多重化回路

【課題】データ信号とクロック信号との位相関係を適応的に制御できる信号多重化回路を提供する。

【解決手段】信号多重化回路は、第1のクロック信号の第1の位相位置に同期したデータ遷移をする第1のデータ信号と第1のクロック信号の第1の位相位置から180度位相がずれた第2の位相位置に同期したデータ遷移をする第2のデータ信号とを受け取り、第2のクロック信号に応じて第1及び第2のデータ信号を順次選択して出力するセレクタ回路と、第1及び第2のデータ信号と第1及び第2のクロック信号とに基づいて、第2のクロック信号とデータ遷移との位相関係を示す位相制御信号を出力する位相検出器と、位相制御信号に応じて位相関係を制御する位相制御器とを含む

(もっと読む)

半導体装置

【課題】高速の半導体装置で要求されるクロック整列トレーニング動作を提供すること。

【解決手段】システムクロック及びデータクロックを入力されるクロック入力部(200)と、データクロックの周波数を分周して所定の位相差を有する複数の多重位相データ分周クロックを生成し、分周制御信号に応答して多重位相データ分周クロックの位相の反転可否を決定するクロック分周部(220)と、多重位相データ分周クロックのうち所定の第1選択クロックの位相を基準としてシステムクロックの位相を検出し、その結果に対応して分周制御信号のレベルを決定する第1位相検出部(240)と、多重位相データ分周クロックのうち所定の第2選択クロックの位相を基準としてシステムクロックの位相を検出し、その結果に対応してトレーニング情報信号を生成する第2位相検出部(260)と、トレーニング情報信号を外部に伝送するための信号伝送部(270)とを具備する。

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

半導体集積回路装置

【課題】DLL回路においてロックはずれが発生しても、短時間で確実に正常ロック状態に復帰させる。

【解決手段】遅延回路13の遅延時間が1周期より小さくなると、遅延検出回路15から最小遅延時間検出信号K2が出力される。さらに位相周波数比較器11がUPパルスを出力していると、最小遅延時間検出信号K2とUPパルスとの2NOR論理(否定論理和回路21)によりクロックがUPパルスカウンタ19に伝達し、Hレベルのロックはずれ検出信号K3が出力され、リセット期間保持カウンタ17にLレベルが入力される。これにより、リセット期間保持カウンタ17がカウンタ動作を開始し、所定の期間、リセット信号をLレベルにして制御電圧CNTLを電源電圧にショートし、かつ位相周波数比較器11をリセットする。

(もっと読む)

フリップフロップ回路

【課題】不感帯が少なく高速安定動作が可能なフリップフロップ回路を提供すること。

【解決手段】本発明は、データ信号Dと、立ち上がり遅延クロック信号CKdとを入力し、データ信号Dの立ち下がりと立ち上がり遅延クロック信号CKdの立ち下がりとによって内部ノードNCの信号を立ち上げる第1のラッチ回路L1と、内部ノードNCの信号とクロック信号CKとを入力し、内部ノードNCの信号が立ち上がっている状態でクロック信号CKが立ち下がるタイミングにより内部ノードXの信号を立ち下げる第2のラッチ回路L2と、内部ノードXの信号とクロック信号CKとを入力し、クロック信号CKが立ち上がっている状態でのデータ信号Dを保持する出力信号を生成するための第3のラッチ回路L3と、内部ノードNCの信号を立ち上がり遅延クロック信号CKdによってプルダウンさせるプルダウン回路PDとを備えるフリップフロップ回路である。

(もっと読む)

位相検出回路及びデータ処理装置

【課題】回路構成が簡素化され、低消費電力化され集積回路化する上で有利な構成の回路を得る。

【解決手段】第1クロックが各クロック入力端に与えられる複数段のフリップフロップ回路(Q1−Q7)と、第2クロックが入力される直列接続された複数段の遅延素子(D1−D6)と、前記複数段の遅延素子の出力をそれぞれ、前記複数段のフリップフロップ回路の各データ入力端に与える接続部(L1−L7)と、前記複数段のフリップフロップ回路の出力データが入力され、この出力データ内容に応じて変化する制御信号を得る信号生成回路(163)と、前記信号生成回路からの制御信号に応じて、前記第1若しくは第2クロックを相調整する位相調整信号を出力する位相調整信号出力部(164)を有する。

(もっと読む)

電圧制御発振回路

【課題】動作が誤発振状態または準安定状態となったことを検出し、誤発振状態または準安定状態から抜け出して正常な発振状態にとすることができるVCOをを提供する。

【解決手段】本発明の電圧制御発振回路は、互いに逆相の差動のクロック信号が入力される差動遅延素子を縦続接続し、バイアス電圧によって差動遅延素子に流れる電流の量を制御することで、該差動のクロック信号の遅延量を制御する差動リングオシレータ型の電圧制御発振回路であり、いずれかの差動遅延素子の差動出力の出力電圧と、異常動作を検出する電圧に設定されたリファレンス電圧とを比較することにより異常発振を検出して検出信号を出力する位相検出部と、差動遅延素子毎に設けられ、検出信号が入力されると、差動出力対間の電位差を増幅するクロスカップル回路とを有している。

(もっと読む)

時間計測回路

【課題】短い時間幅の高分解能な計測と長い時間幅の低分解能な計測とを、回路規模を大幅に増大させることなく、いずれも実現させることが可能な時間計測回路を提供する。

【解決手段】駆動電圧VDDLに応じた遅延時間で信号を遅延させる遅延ユニットDUをM(Mは正整数)段直列接続してなり、起動用パルスPAの入力により起動され、各遅延ユニットDUにてパルス信号を順次遅延させながら伝送するパルス遅延回路10と、計測用パルスPBが入力されると、パルス遅延回路10内でのパルス信号の位置を検出(ラッチ)し、その検出結果を、起動用パルスPAの入力から計測用パルスPBの入力までの時間Tm内にパルス信号が通過した遅延ユニットDUの段数を表す所定ビットのデジタルデータDTに変換して出力するラッチ&エンコーダ12と、電圧設定データDVに従った大きさの駆動電圧VDDLを発生させる駆動電圧設定回路14とを備える。

(もっと読む)

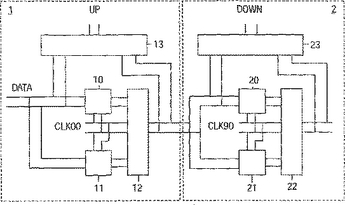

多重送信用ラッチ付き線形位相検出器

線形位相検出器は、クロック抽出器およびデータ再生器内で使用するために、第1および第2クロック信号(CLKOO,CLK90)を受信して第1および第2制御信号(UP,DOWN)を生成する回路(1,2)を備え、これらの回路は、入力および出力との間の長い経路の長さと多くの動作により大きな遅延を有する(洞察)。これらは、それぞれの回路(1,2)に2つの並列のラッチ(10,11,20,21)と、これらのラッチの出力信号を多重送信するマルチプレクサ(12,22)を与えることにより、より速くさせることが可能である(基本概念)。データ信号は第1回路(1)に供給され、第1回路出力信号は第2回路(2)に供給される。それぞれがまた2つのラッチとマルチプレクサを備える第3および第4回路(3,4)を導入することにより、高速線形位相検出器は、多数のトランジスタから独立した、データ信号におけるゲインを有するように構成されており、これは長所である。それぞれの回路(1,2,3,4)の論理回路(13,23)は、加算器/減算器(5)に結合される。  (もっと読む)

(もっと読む)

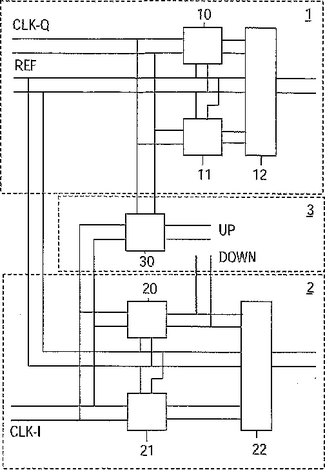

高速線形位相検出器

第1および第2(位相)制御信号(UP、DOWN)を生成するために基準信号(REF)および第1および第2クロック信号(CLK−Q、CLK−I)を受信する回路を備える乗算器回路、復調器および受信機用の線形位相検出器は、長い経路長および入力と出力との間の多くの動作のために大きな遅延を有する(洞察)。各回路(1、2)に2個の並列ラッチ(10、11、20、21)およびラッチ出力信号を多重化するための多重化装置(12、22)を備えることによって、線形位相検出器をより高速にすることができる(基本概念)。前記多重化装置は、周波数検出器に供給されるべき(周波数制御)信号を生成し、第3回路(3)が前記(位相)制御信号(UP、DOWN)のうちの少なくとも1つを生成している。前記第3回路(3)は、前記第1(位相)制御信号(UP)を生成するラッチ(30)を備え、第2回路(2)のラッチの1つ(20)が第2(位相)制御信号(DOWN)を生成している。または、前記第3回路(3)は、4個のEXORゲート(31〜34)を備える論理回路(31〜34)を備える。第5EXORゲート(35)が、第3回路(3)を平衡させるために使用される。  (もっと読む)

(もっと読む)

可変遅延回路及び半導体集積回路装置

【課題】 高い精度で遅延時間を制御できる可変遅延回路を用いた半導体集積回路装置を提供することを目的とする。

【解決手段】入力クロック信号を遅延させる第1のDLL回路3と、第1のDLL回路よりも高い精度で遅延を制御できる第2のDLL回路10とを有し、第1及び第2のDLL回路の位相比較(31、14)を独立に動作させ、かつ第2のDLL回路の遅延量制御を第1のDLL回路の動作に従属させることで、入力クロック信号に対し所定の位相関係を有する出力クロック信号を出力するように第1及び第2のDLL回路で遅延を与える半導体集積回路装置。

(もっと読む)

半導体集積回路装置のタイミング制御回路

【課題】半導体集積回路装置の制御対象回路に与える制御信号が製造プロセスや電源電圧、周囲温度などの変動によって変動するのを抑制すること。

【解決手段】外部クロックextCLKに基づき基準信号actCLKを生成する中央制御回路2側に、遅延値を制御するディジタル値DCTRL[n:0]からなる遅延制御信号を生成する遅延制御回路6を設け、中央制御回路2からローカル制御回路3に対して基準信号と遅延制御信号とを供給する。ローカル制御回路3に設けた可変遅延回路7は、遅延値がディジタル値で制御される単位遅延回路を多段に接続して構成され、メモリセルアレイ1に供給する各種の制御信号を、前記基準信号を前記遅延制御信号のディジタル値が示す所定の遅延値だけ遅延したタイミングで生成する。

(もっと読む)

1 - 16 / 16

[ Back to top ]