Fターム[5J039JJ13]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 主たる比較部 (286) | 二安定素子によるもの (109) | D−FF (82)

Fターム[5J039JJ13]に分類される特許

41 - 60 / 82

DLL回路及びその制御方法

【課題】本発明は、短いロッキングタイムを有する多相DLL回路及びその制御方法を提供する。

【解決手段】本発明のDLL回路は、 基準クロックを遅延させてDLLクロックを生成するが、制御電圧のレベルに応じて遅延量を調整する遅延手段;制御電圧の初期レベルを制御し、検出イネーブル信号を生成する初期動作制御手段;及び、検出イネーブル信号に応じて前記基準クロック及びDLLクロックの位相を比較して、制御電圧を生成する遅延制御手段を含むことを特徴とする。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

半導体装置

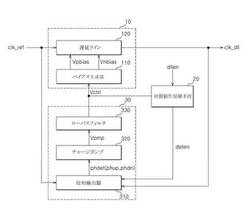

【課題】PVT変動による遅延制御回路の遅延量変動を正しく補正する。

【解決手段】互いに動作条件が異なる第1及び第2の遅延素子列121,122と、第1及び第2の遅延素子列121,122に同時に入力されたパルス信号Pの伝搬速度差を検出する検出回路123と、検出回路123による検出結果に基づいて選択信号SELを生成する設定回路124とを備える。選択信号SELは、基準信号を遅延させることによって動作タイミング信号を生成する遅延制御回路130に供給され、その遅延量は選択信号SELによって調整される。これにより、PVT変動を見越して遅延制御回路の遅延量を大きく設計しておく必要がなくなるため、パフォーマンスの低下を防止することが可能となる。

(もっと読む)

同期信号検出回路および半導体集積回路

【課題】水平方向の描画開始位置を決定する同期信号の検出精度を向上させることができる同期信号検出回路および半導体集積回路を提供する。

【解決手段】同期信号検出回路は、単位検出回路のうちの偶数番目の単位検出回路からなり、偶数番目の単位検出回路による単位検出結果にもとづいた偶数側検出結果を出力する偶数側検出回路と、奇数番目の単位検出回路からなり、奇数番目の単位検出回路による単位検出結果にもとづいて奇数側検出結果を出力する奇数側検出回路と、偶数側検出結果と奇数側検出結果とを比較し、比較の結果に応じて、偶数側検出結果と奇数側検出結果とのいずれかにもとづいて、有効エッジのタイミングを判定する判定回路とを有し、同期信号の有効エッジの多相クロック信号のクロックエッジに対するタイミングを判定する。

(もっと読む)

2値化回路と位相差判別装置

【課題】 入力電圧を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と第1出力端子26と第2出力端子28とピークホールド回路30とボトムホールド回路40と閾値演算回路50と第1比較回路60と第2比較回路70と第1選択回路80と第2選択回路90と第3選択回路100と第4選択回路110を備えている。第1選択回路80は2値化信号を出力し、第2選択回路90は遅れ2値化信号を出力する。ピークホールド回路30は遅れ2値化信号に基づいてピーク電圧を減少させ、ボトムホールド回路40は遅れ2値化信号に基づいてボトム電圧を増加させる。そのため、遅れ2値化信号を2値化信号に対して確実に遅延させることが可能となる。

(もっと読む)

信号再生回路向け位相比較回路及び信号再生回路向け位相比較回路を備える光通信装置

【課題】 1/Nレート構成に対応可能な高精度な位相比較回路を得る。

【解決手段】それぞれ、N相クロック信号CLKの各クロック信号を、受信データ信号DINの立ち上がりに同期してトラックホールドするN個のトラックホールド回路を備える。これらのN個のトラックホールド回路の出力から、受信データ信号DINの立ち上がりエッジが、クロック信号CLKの立ち上がりエッジに位置しているクロック信号をトラックホールドしているもののみをセレクタで選択して、位相差信号として出力する。

(もっと読む)

位相比較回路

【課題】D−FFの内部遅延が無視できない高速動作時において位相比較回路の低消費電力化を実現する。

【解決手段】マスタースレーブマスター型D−FF11は、第1のM−FF11−1,S−FF11−2および第2のM−FF11−3が縦続接続され、入力NRZデータ信号をクロック信号に応答して識別し、S−FFおよび第2のM−FFから出力する。遅延回路4は、入力NRZデータ信号をS−FFと同じ時間だけ遅延させる。第1のEXOR回路7は遅延回路の出力とS−FFの出力の排他的論理和演算を行ない、第2のEXOR8はS−FFの出力と第2のM−FFの出力の排他的論理和演算を行なう。加算器9は第1のEXOR回路の出力と第2のEXORの反転出力を加算する。

(もっと読む)

タイミングリカバリー回路

【課題】 構成を簡易にしたタイミングリカバリー回路を提供する。

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号が入力される端子とVCXO109の入力端子との接続を制御し、異常信号によって接続をオンにするスイッチとを有するタイミングリカバリー回路である。

(もっと読む)

位相制御回路

【課題】 データ信号とクロック信号がどのような位相差であっても位相差に応じたパルス幅の位相差信号を出力する。

【解決手段】 データ信号および反転した信号Yを入力し、反転した信号Yをデータ信号の遷移タイミングで保持して信号Xを出力する第1の保持手段と、クロック信号および信号Xを入力し、信号Xをクロック信号の遷移タイミングで保持して信号Yを出力する第2の保持手段と、信号Xおよび信号Yを入力し、その位相差に応じたパルス幅を有する位相差信号を生成し、データ信号とクロック信号の位相差に応じたパルス幅を有する位相差信号として出力する比較手段とを備える。

(もっと読む)

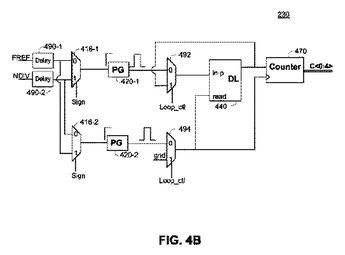

完全デジタル位相ロックループにおける位相デジタル変換器

位相デジタル変換器と、完全デジタル位相ロックループと、完全デジタル位相ロックループを有する装置とについて、本明細書で説明する。位相デジタル変換器は、時間デジタル変換器を駆動する位相周波数変換器を含む。時間デジタル変換器は、位相周波数変換器によって出力された位相差の絶対値と符号とを判断する。時間デジタル変換器は、タップ付き遅延線とループフィードバックカウンタとを利用して、ループ追跡プロセスによくある小さいタイミング差およびループ収集プロセスによくある大きいタイミング差の測定を可能にする。タップ付き遅延線は、基準期間の部分の測定を可能にし、基準クロックの速度に関する要件を低減することによって位相デジタル変換器のより低電力の動作を可能にする。  (もっと読む)

(もっと読む)

位相調整回路

【課題】大きな位相ずれにも対応可能な位相調整回路を提供する。

【解決手段】基準となるクロック信号CLKeに同期して与えられる画像データDATAeとデータイネーブル信号DEeは、このクロック信号CLKeで動作するFF31,33,38,40で2クロック分遅延され、画像データDTeと共通のデータイネーブル信号DEとして出力される。位相調整の対象となるクロック信号CLKoに同期して与えられる連続する2つの画像データDATAoは、それぞれFF34,35によって2クロック周期の間保持される。FF34,35の保持データは、セレクタ37によっていずれか一方が選択出力され、基準となるクロック信号CLKeのタイミングでFF39に保持されて画像データDToとして出力される。これにより、位相のずれがクロック周期よりも小さければ、2系統の画像データは同位相になるように位相調整ができる。

(もっと読む)

高速時間ディジタル・コンバータ

【解決手段】 時間ディジタル・コンバータ(TDC)がサブ・インバータ遅延分解能でサンプリングすることを可能にするための手法が開示されている。一実施形態では、TDC中の差動型D−Qフリップフロップへの入力は、シングルエンド型信号、およびこの信号の遅延された形態および反転された形態に接続されてこの信号の時間補間を可能にする。さらに、TDC中の第1遅延ラインおよび相補な遅延ラインの負荷の平衡を保つための手法が開示されている。 (もっと読む)

位相検出装置、位相比較装置およびクロック同期装置

【課題】クロック同期システムに用いる位相比較器として、次段のカウンタに影響を与えることなく、クロックの同期がとれた際に確実にロックをかけること。

【解決手段】本発明は、基準クロックの位相に対する比較クロックの位相のずれを検出する第1の位相比較部K1aと、基準クロックおよび比較クロックのいずれか一方について所定時間遅延または進んだ状態での両クロックの位相のずれを検出する第2の位相比較部K1bと、第1の位相比較部K1aの出力と第2の位相比較部K1bの出力との論理積を位相ずれの検出結果として出力する論理積部AND1とを備える

(もっと読む)

半導体集積回路

【課題】低消費電力化に適したAVS技術又はDVS技術を実現した半導体集積回路を提供すること。

【解決手段】半導体集積回路は、クリティカル・パスを形成する第1のフリップ・フロップ、組み合わせ回路及び第2のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第1の遅延回路及び第3のフリップ・フロップと、前記組み合わせ回路の後段に設けられる第2の遅延回路及び第4のフリップ・フロップと、第2のフリップ・フロップの出力と第3のフリップ・フロップの出力とを比較する第1の比較回路と、第2のフリップ・フロップの出力と第4のフリップ・フロップの出力とを比較する第2の比較回路と、これら比較回路の出力に応じて、前記組み合わせ回路に供給される電源電圧を制御する制御回路とを備える。なお、第1の遅延回路による遅延時間と第2の遅延回路による遅延時間は異なる。

(もっと読む)

PLL回路

【課題】ハイブリッド制御方式PLL回路の定常状態における位相ジッタを低減する。

【解決手段】ハイブリッド制御方式PLL回路内の位相比較回路PHASE_COMPの出力S_PHが頻繁に変化しているか否かを判定する定常状態検出回路CONV_DETを設け、位相比較回路の出力S_PHが暫く変化していない時は定常状態に達していないと判定し、頻繁に変化している時は定常状態に達したと判定し、その判定結果に基づいて、電圧制御発振回路VCOの発振周波数をデジタル制御信号S_DGによって制御する制御幅を変更し、もしくは(および)、アナログ制御信号S_AGを変化させる頻度を変更する。これにより、定常状態に達する前の収束性を損なうことなく、定常状態に達した後のデジタル制御信号による発振周波数の制御幅を小さくできる。よって、定常状態における位相ジッタを低減できる。

(もっと読む)

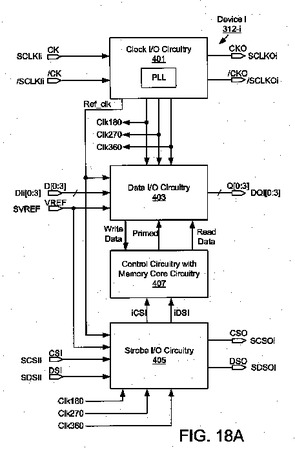

複数のデバイスおよび柔軟なデータ整列を用いるメモリコントローラを有するシステムにおけるクロック再生およびタイミング方法

システムは、メモリコントローラおよび直列接続されている複数の半導体デバイスを備える。各デバイスはデータを格納する。コントローラは、デバイスの動作を同期させるクロックを供給する。各デバイスは、イネーブル信号によって選択的にイネーブルまたはディセーブルされるPLLを備える。選択デバイスのPLLはイネーブル信号によってイネーブルされ、他のデバイスはディセーブルされる。イネーブルされたPLLは、90°の倍数の位相シフトで複数の再生クロックを供給する。データ転送は、再生クロックのうちの1つのクロックと同期する。ディセーブルされたPLLのデバイス内で、データ転送は入力クロックと同期する。イネーブルおよびディセーブルされたPLLにより、各デバイスはソース同期クロッキングおよび共通同期クロッキングを行う。最後のデバイスのデバイス識別子の最下位ビットがクロック整列を決定する。  (もっと読む)

(もっと読む)

PLL発振回路

【課題】分数分周型のPLL発振回路における抵抗やキャパシタの定数を小さくすると共に、雑音を低減する。

【解決手段】入力信号INと帰還信号FBaの周波数の差に応じた電流を共通のノードNcに出力する周波数比較器10aと、入力信号INと帰還信号FBbの周波数の差に応じた電流を共通のノードNcに出力する周波数比較器10bと、このノードNcに出力される信号の高周波成分を除去して制御電圧VCを生成するループフィルタ20と、制御電圧VCに応じた周波数foの出力信号OUTを生成するVCO30と、出力信号OUTの周波数をそれぞれ1/Mと1/Nに分周して帰還信号FBa,FBbを出力する分周器40a,40bを設ける。

(もっと読む)

クロック信号出力回路

【課題】逓倍クロック信号の基準クロック信号に対する同期ずれを補正することができるクロック信号出力回路を提供する。

【解決手段】位相誤差補正回路12は、基準クロック信号PREFと逓倍クロック信号POUTとの位相差を検出し、その位相差に応じて、逓倍クロック信号POURの出力位相を基準クロック信号PREFに同期させる補正を、1制御周期の間に複数回実行する。

(もっと読む)

パルス幅測定方法および回路

【課題】入力パルスのデューティが測定可能となり、回路構成が簡素化できるようにする。

【解決手段】HレベルとLレベルとを繰り返す入力パルスを同一遅延時間でn+1段に亘って遅延させてn+1相の遅延パルスを生成し、該n+1相の各遅延パルスのそれぞれがHレベルであるかLレベルであるかに応じて変化し、且つ所定のタイミングにおいて、前記入力パルスのHレベル側又はLレベル側のパルス幅を示すエンコード信号を生成し、前記所定のタイミングにおける前記エンコード信号を、前記Hレベル側又はLレベル側のパルス幅信号として保持する。

(もっと読む)

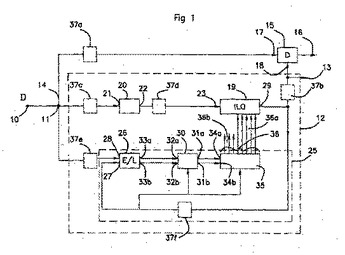

外部制御を必要としないデジタル位相ロックによるクロック抽出装置

本発明は、注入ロック発振器(19)と、デジタル位相検出器(26)を有する位相制御ループ(25)とを備えた、ベースバンドシリアル信号からクロックを抽出する装置に関する。発振器(19)はその周波数の値を制御するデジタル制御入力部(24)を備え、位相制御ループ(25)は、デジタル位相検出器(26)から供給されるデジタル信号の相対値を累算し、発振器(19)用のデジタル形態の制御信号を渡す、カウント回路(30、35)を備える。  (もっと読む)

(もっと読む)

41 - 60 / 82

[ Back to top ]