Fターム[5J039JJ13]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 主たる比較部 (286) | 二安定素子によるもの (109) | D−FF (82)

Fターム[5J039JJ13]に分類される特許

61 - 80 / 82

半導体集積回路およびイコライザの制御方法

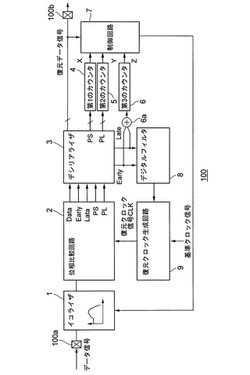

【課題】回路規模の増大を抑制しつつ、受信したデータ信号の等化量を調整することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路100は、イコライザと、イコライザにより等化されたデータ信号の位相を検出しこのデータ信号の位相と復元クロック信号の位相とを比較し、等化されたデータ信号のビット幅が復元クロック信号の周期よりも小さいときは第1の比較信号を出力し、一方、大きいときは第2の比較信号を出力し、復元クロック信号の位相がデータ信号の位相よりも進んでいる場合には第3の比較信号を出力し、遅れている場合には第4の比較信号を出力する位相比較回路と、第3、第4の比較信号および基準クロック信号に基づいて、復元クロック信号を生成する復元クロック生成回路と、少なくとも第1、第2の比較信号に基づいて、イコライザのピーキング量を制御する制御回路と、を備える。

(もっと読む)

クロックスキューコントローラ及びそれを備える集積回路

【課題】クロックスキューを補償することができるコントローラを備える集積回路を提供する。

【解決手段】第1クロックマッシュに入力される第1クロックと第2クロックマッシュに入力される第2クロックとの間のスキューを調節するためのクロックスキューコントローラを備える。クロックスキューコントローラは、第1出力クロックと第2出力クロックとの間の遅延時間に対応するパルス信号を発生するパルス発生器と、パルス信号のパルス幅に対応するデジタル信号を出力するパルス幅検出器と、デジタル信号に対応する時間だけ、第1及び第2クロックのうちのいずれか一つを遅延させるクロック遅延調節器と、を備えて、クロックマッシュの間のクロックスキューを検出し、該検出されたスキューに対応する遅延時間だけクロックマッシュに供給されるクロック等の遅延時間を調節することができる。

(もっと読む)

多相クロック生成回路

【課題】従来の多相クロック生成回路では、出力クロック信号に任意の周波数プロファイルを設定することができなかった。

【解決手段】本発明にかかる多相クロック生成回路1は、基準クロック信号に基づき多相クロック信号を生成する位相ロックループ回路10と、多相クロック信号の周波数プロファイルを保持し、開始信号に基づき周波数プロファイルの出力を開始し、基準クロック信号に基づき任意の周期で周波数プロファイルを更新する周波数プロファイル保持回路20と、周波数プロファイルに基づいて多相クロック信号のうち任意の位相のクロック信号を選択し、選択したクロック信号を位相ロックループ回路10に帰還させるクロック選択回路30とを有することを特徴とするものである。

(もっと読む)

装置、位相ロック・ループ・システム及び位相ロック・ループを動作させるための方法

【課題】フィード・フォワード位相周波数検出器を備えた、高速且つ低ジッタの位相ロック・ループ(PLL)を提供する。

【解決手段】

位相周波数検出器に含まれる位相差センサは、基準信号の立ち上がりエッジとフィードバック信号の立ち上がりエッジとの間の位相差期間を指示する出力信号を供給する。また、この装置に含まれる進み−遅れセンサは、基準信号がフィードバック信号より進んでいる場合を指示する出力信号を供給する。さらに、ステアリング論理が、位相差センサ及び進み−遅れセンサの出力に結合される。このステアリング論理は、基準信号がフィードバック信号より進んでいる場合は、位相差期間信号を第1出力に導き、基準信号がフィードバック信号より遅れている場合は、位相差期間信号を第2出力に導く。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】入力されるシステムクロック信号と反転されたシステムクロック信号との交差点と、基準信号とが一致するように調整可能な回路を備えた半導体メモリ装置を提供すること。

【解決手段】このため本発明は、システムクロック信号と反転されたシステムクロック信号との交差点を基準とする第1クロック信号を生成する第1クロック入力部と、システムクロック信号と基準信号との交差点を基準とする第2クロック信号を生成する第2クロック入力部と、反転されたシステムクロック信号と基準信号との交差点を基準とする第3クロック信号を生成する第3クロック入力部と、遅延制御信号に対応して第1クロック信号を遅延させ遅延クロック信号として出力する遅延部と、遅延クロック信号と第2クロック信号との位相差又は遅延クロック信号と第3クロック信号との位相差に対応して遅延制御信号を出力するクロック遅延調整部とを備える半導体メモリ装置を提供する。

(もっと読む)

半導体メモリ装置

【課題】半導体メモリ装置の遅延固定クロックの出力において、デューティ比を容易に補正して出力可能な遅延固定回路を備える半導体メモリ装置を提供すること。

【解決手段】このため、本発明は、システムクロックを所定の時間遅延させ、遅延固定クロックを出力する遅延固定回路と、該遅延固定クロックのデューティ比を補正して第1クロックを出力するにあたり、前記第1クロックの第2エッジと、前記第1クロックによって生成された第2クロックの第2エッジとのタイミング差に対応して、前記遅延固定クロックのハイレベル区間とローレベル区間との比を調整するデューティ補正回路と、前記第1クロックの第1エッジと前記第2クロックの第1エッジとの位相を合わせるクロック同期回路とを備える半導体メモリ装置を提供する。

(もっと読む)

位相制御回路

【課題】経時変化や温度変化に拘らず、常に最適なタイミングの調整をすることが可能な位相制御回路を実現する。

【解決手段】位相を制御する位相制御回路において、クロック信号を遅延する可変遅延回路と、遅延されたクロック信号がクロック入力端子に入力され、データ信号がデータ入力端子に入力される第1のフリップフロップ回路と、データ信号がクロック入力端子に入力され、遅延されたクロック信号がデータ入力端子に入力される第2のフリップフロップ回路と、第2のフリップフロップ回路の出力信号に基づいて可変遅延回路の遅延量を制御する積分回路とを備える。

(もっと読む)

クロック信号を発生するクロック発生回路及び方法

【課題】クロック信号を発生するクロック発生回路及び方法を公開する。

【解決手段】クロック発生回路は、外部クロック信号を直接受信して、反転された外部クロック信号を発生するインバータと、一番目のループ回路が反転外部クロック信号を受信してn(nは2以上の定数)個のノードをそれぞれ備え、M−1(Mは1以上の定数)個のループ回路のそれぞれがn個のノードの対応する1つからn個の中間内部クロック信号それぞれを発生し、n個の中間内部クロック信号の周波数が外部クロック信号及び反転外部クロック信号の周波数の倍数であることを特徴とする直列に配列されたM個のループ回路と、それぞれが直列に接続されて以前のループ回路から対応する中間内部クロック信号を受信し、対応する中間内部クロック信号を次のループ回路に出力するM−1個のインバータそれぞれと、を具備するn個のインバータの集合で構成されている。

(もっと読む)

デジタル位相検出器

【課題】 従来、デジタル位相検出器における位相検出限界は、遅延素子の遅延時間により決定されるため、例えば、PLL回路に低ジッタ特性が要求される場合には、全デジタルPLL回路は不適当であった。

【解決手段】 第1のクロックCLKfを遅延する複数の第1の遅延素子1011〜101nと、第2のクロックCLKrを遅延する複数の第2の遅延素子1021〜102nと、前記第2の遅延素子により順次遅延された前記第2のクロックREF1〜REFnに従って、前記第1の遅延素子により順次遅延された前記第1のクロックFB1〜FBnを取り込み、相対的な位相関係を表すデジタル値Q1〜Qnを保持する複数のデータ保持回路1031〜103nと、を備えるように構成する。

(もっと読む)

位相同期ループ回路及び位相同期方法

【課題】 電源電圧のレベルが低くなっても高周波数の多様なクロック信号を発生することが可能な位相同期ループ及び方法を提供すること。

【解決手段】 位相同期ループ回路は外部クロック信号と帰還クロック信号を受信し、外部クロック信号の位相が帰還クロック信号の位相より先行するとアップ信号を発生し、外部クロック信号の位相が帰還クロック信号の位相より遅れるとダウン信号を発生する位相検出器と、アップ信号に応答して制御電圧が増加し、ダウン信号に応答して制御電圧を減少するループフィルタ回路と、制御電圧を受信してn(nは4以上の整数)個の内部クロック信号を直接発生する電圧制御発振器回路とを含むこともできる。また、位相同期ループ回路は少なくとも4個のループを含み制御電圧を受信して複数の内部クロック信号を発生する電圧制御発振器回路も含むことができる。

(もっと読む)

デジタル制御型位相合成回路システム

【課題】 ジッタ耐性を強化し、かつロックレンジを拡大するデジタル制御型位相合成回路システムを得る。

【解決手段】 位相の異なる2つのクロックと制御信号が入力され、制御信号による重み付けに基づいて、これらのクロックの中間の位相をもつ出力クロックを合成する位相合成回路と、出力クロックの位相と基準クロックの位相とを比較するバイナリ型位相比較回路と、バイナリ型位相比較回路による比較結果に基づいて第1のカウント値をカウントアップ又はカウントダウンし、第1のカウント値の最上位ビットの値を出力し、第1のカウント値にキャリー又はボローが発生した場合にクロックパルスを出力する第1のアップダウンカウンタと、クロックパルスを動作クロックとし、第1のカウント値の最上位ビットに基づいて第2のカウント値をカウントアップ又はカウントダウンし、第2のカウント値を制御信号として出力する第2のアップダウンカウンタとを有する。

(もっと読む)

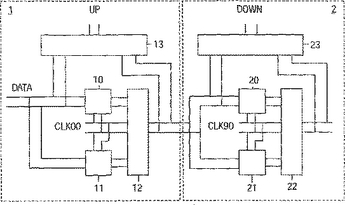

多重送信用ラッチ付き線形位相検出器

線形位相検出器は、クロック抽出器およびデータ再生器内で使用するために、第1および第2クロック信号(CLKOO,CLK90)を受信して第1および第2制御信号(UP,DOWN)を生成する回路(1,2)を備え、これらの回路は、入力および出力との間の長い経路の長さと多くの動作により大きな遅延を有する(洞察)。これらは、それぞれの回路(1,2)に2つの並列のラッチ(10,11,20,21)と、これらのラッチの出力信号を多重送信するマルチプレクサ(12,22)を与えることにより、より速くさせることが可能である(基本概念)。データ信号は第1回路(1)に供給され、第1回路出力信号は第2回路(2)に供給される。それぞれがまた2つのラッチとマルチプレクサを備える第3および第4回路(3,4)を導入することにより、高速線形位相検出器は、多数のトランジスタから独立した、データ信号におけるゲインを有するように構成されており、これは長所である。それぞれの回路(1,2,3,4)の論理回路(13,23)は、加算器/減算器(5)に結合される。  (もっと読む)

(もっと読む)

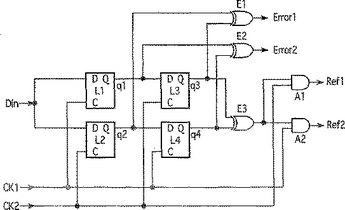

線形位相誤差検出に関する方法及び装置

【課題】超高速且つ高性能な線形位相誤差検出の方法及び検出回路を提供すること。

【解決手段】入力データ信号のエッジとクロック信号のエッジとの間の位相誤差を検出するために使用される方法及び装置を開示する。本発明は超高周波数において並びに線形位相誤差情報が必要な場合において使用される。本発明は任意の集積回路論理技術の利便性を拡張する。これにより周波数適用範囲が倍増するとともに、所望の線形位相誤差を測定する機能が維持される。クロッキング信号を用いてデータ入力信号のサンプリングを行うためにフリップフロップ回路が使用され、立ち上がりエッジのデータと立ち下がりエッジのデータに対して別個に処理が行われた後、両エッジからの位相誤差情報のアナログ式再合成が集積回路の速度による制限のない方法で行われる。

(もっと読む)

位相比較回路およびCDR回路

位相比較回路の動作速度を緩和して、高速なデータ信号入力に対しても安定したクロック抽出機能とデータ整形機能を有するCDR回路を提供する。入力されたデータ信号の単位時間幅の2倍の周期を有するクロック信号で動作する位相比較回路において、データ信号の遷移点とクロック信号の遷移点との間の位相差を表す位相誤差信号のパルス幅を、データ信号の単位時間幅だけ伸長する。  (もっと読む)

(もっと読む)

位相比較器及び位相比較器を有する半導体装置

【課題】 位相比較器の位相差の検出精度を高めることである。

【解決手段】 位相差信号生成回路24は、エッジ検出フラグ生成回路22で検出される比較対象信号COMP1の立ち上がりに同期した信号と、エッジ検出フラグ生成回路23で検出される比較対象信号COMP2の立ち上がりに同期した信号から比較対象信号COMP1と比較対象信号COMP2の位相差に応じた期間ハイレベルとなる信号C_SIGNALをトライステートバッファ12の制御端子に出力する。ステータス管理回路25は、比較対象信号COMP1と比較対象信号COMP2位相の進みまたは遅れに応じた信号A_SIGNALをトライステートバッファ12の入力端子に出力する。

(もっと読む)

半導体装置

【課題】 出力信号のAC特性を自動調整する機能を備えた半導体装置を提供する。

【解決手段】 第一及び第二の信号CLK,RDXを複数の端子2a,2bから並行して出力する信号出力部1と、各端子2a,2bから出力される第一の信号CLKと第二の信号RDXの遅延時間を検出する遅延検出部6と、遅延時間に基づいて第一の信号CLKと第二の信号RDXとの間の遅延時間を相殺するように、信号出力部1と端子2aとの間に遅延素子4a〜4dを挿入する遅延制御部7とを備えた。

(もっと読む)

差動遅延回路及びDLL回路

【課題】電流制御手段の電流制御用トランジスタに供給されるゲート電圧がトランジスタの閾値Vthに近づいても、出力されるクロック波形に振幅減衰が生じることのない差動遅延回路及びDLL回路を提供すること。

【解決手段】 互いに逆相の差動のクロック信号が入力される一対の差動トランジスタMP2,MP3と、前記差動トランジスタに接続されて、差動のクロック信号が出力される一対の出力ラインと、前記差動トランジスタに接続されて、制御電圧によって前記差動トランジスタに流れる電流の量を制御することによって、前記出力ラインに出力される差動のクロック信号の遅延量を制御することが可能な電流制御手段MP1,MN3〜MN5と、前記差動トランジスタに接続されて、前記差動トランジスタに流れる電流に所定の定電流を供給する電流供給手段MP4と、を具備したものである。

(もっと読む)

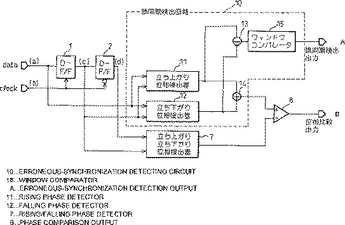

位相誤同期検出回路

位相比較回路に関し、特にデータとクロックとの位相差の比較において、データのデューティが100パーセントからずれたときに生じる位相の誤同期を検出する位相誤同期検出回路を提供する。データとクロックとの位相差を検出する位相比較器において、その位相誤同期検出回路は、データの立ち上がりとクロック位相との位相差を検出してその平均位相差を出力する第1の位相検出部と、データの立ち下がりとクロック位相との位相差を検出してその平均位相差を出力する第2の位相検出部と、前記第1の位相検出部からの平均位相差と前記第2の位相検出部からの平均位相差との差が所定の範囲を超えるときに位相誤同期と判定する位相誤同期判定部と、により構成する。  (もっと読む)

(もっと読む)

遅延同期ループ回路の良否検査方法及び遅延同期ループ回路の良否検査回路

【課題】

ディジタルデータをもとに良否判定可能な比較的安価な検査装置を用いて遅延同期ループ回路の良否検査を行うことができる遅延同期ループ回路の良否検査方法及び、遅延同期ループ回路の良否検査回路を提供する。

【解決手段】

基準信号を所定時間ずつ遅延させたN個のタップ信号を出力する遅延同期ループ回路の良否検査回路及びこの良否検査回路により行う良否検査方法において、各タップ信号をクロック信号とするN個のフリップフロップといずれかのタップ信号をクロック信号とするフリップフロップとを直列接続することによってシフトレジスタを形成し、このシフトレジスタを基準信号の1周期分動作させて、N個目のフリップフロップの出力信号とN+1個目のフリップフロップの出力信号とに基づいて遅延同期ループ回路の良否を判定することとした。

(もっと読む)

位相差検出回路

【課題】 ノイズ耐性を向上できる位相差検出回路を提供すること。

【解決手段】 次エッジタイプ判定器31と先立ち上がり判定器32と立ち上がりエッジ専用位相差検出回路80と立ち下がりエッジ専用位相差検出回路90とを設け、前記次エッジタイプ判定器31と前記先立ち上がり判定器32から出力される検出信号をもとに、立ち上がりエッジ専用位相差検出回路80と立ち下がりエッジ専用位相差検出回路90からそれぞれ出力されるUP出力、DN出力をスイッチ回路61〜68、スイッチ回路71〜78により切り替える。

(もっと読む)

61 - 80 / 82

[ Back to top ]