Fターム[5J039JJ18]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 比較結果の出力(アナログ) (180)

Fターム[5J039JJ18]の下位に属するFターム

比較結果が2端子に生じるもの (5)

デジタル出力 (138)

Fターム[5J039JJ18]に分類される特許

21 - 37 / 37

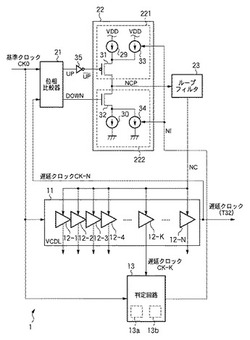

クロック生成回路

【課題】広帯域の周波数範囲におけるどの周波数の基準クロックを受けてもロックする時間を短くできるクロック生成回路を簡易な回路構成で実現。

【解決手段】基準クロックを第1の個数の電圧制御遅延素子12−1〜12−Nで遅延させて第1の遅延クロックを生成し、第2の個数の電圧制御遅延素子12−1〜12−Kで遅延させて第2の遅延クロックを生成する遅延部11と、前記基準クロックの位相と前記第1の遅延クロックの位相とを比較する位相比較部21と、遅延制御電流を出力するチャージポンプ22と、遅延制御部23と、前記基準クロックの位相と前記第2の遅延クロックの位相とを比較し、前記基準クロックと前記第1の遅延クロックとの位相差を判定する判定部13aと、前記位相差が閾値より大きい場合、前記遅延制御電流が第1の値になり、前記閾値以下の場合、前記第1の値より小さい第2の値になるように制御するチャージ制御部13bとを備える。

(もっと読む)

PLL回路

【課題】感度関数と相補感度関数の両方が低減されたPLL回路を提供する。

【解決手段】本発明のPLL回路10は、一般的なPLL回路の構成を備えた第1ループ50と、相補感度関数を低減するための第2ループ52とを備えて構成されている。第1ループ50では、周波数が高い基準クロック34を用いて比較部14にて位相比較を行うことにより、感度関数を下げている。そして、第2ループ52からの出力により電流補償部16にて電流値を補完することにより、相補感度関数を下げている。

(もっと読む)

位相同期回路及びその制御方法、通信装置

【課題】

安定した周波数の出力信号を出力できるようにした位相同期回路及びその制御方法、通信装置を提供する。

【解決手段】

位相同期回路は、入力される制御電圧に応じた周波数の信号を出力信号として出力する電圧制御発振回路と、入力信号と電圧制御発振回路の出力信号との位相を比較する比較手段と、位相の比較に基づく電圧を異なるタイミングでそれぞれ保持する2つ以上のサンプル/ホールド回路と、2つ以上のサンプル/ホールド回路のいずれかを選択し、該選択したサンプル/ホールド回路からの出力を制御電圧として電圧制御発振回路に入力する切換手段と、入力信号の異常を検出する異常検出手段とを具備し、切換手段は、異常検出手段による異常の検出結果に基づいて2つ以上のサンプル/ホールド回路のいずれかの出力を選択する。

(もっと読む)

リング発振器及びこれを用いるマルチ位相クロック補正回路

【課題】クロスカップル構造を有する複数のバッファを備えて発振し、CMLレベルのクロック信号を生成することのできるリング発振器を提供し、また、基準位相クロック信号を補正して希望の周波数、及び互いに予め定められた位相差を有するマルチ位相クロック信号を生成することのできるマルチ位相クロック補正回路を提供する。

【解決手段】 本発明のリング発振器は、各々クロスカップル構造を有し、予め定められた電圧レベルのバイアス電圧が印加されて複数のクロック信号を生成するための複数のバッファ手段を備え、前記複数のクロック信号が、前記バイアス電圧に対応するスイング幅を有する。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】親機、複数台の中継機、複数台の子機を備えた大規模なシステムで符号長が比較的長い同期信号を用いても、安定したPLLの引き込みを実現可能とする。

【解決手段】このPLL制御装置では、TIM抽出回路101は入力信号からタイミング成分を抽出し、VCXOは供給される制御信号に基づき基準信号の位相及び/又は発振周波数を制御する。0次PLL回路102はタイミング成分の位相差に基づき基準信号の発振周波数範囲を設定するための制御信号を出力し、1次PLL回路103はタイミング成分の位相差に基づき基準信号の位相を制御するための制御信号を出力する。制御セレクタ105は、0次PLL回路102又は1次PLL回路103からの制御信号を順次切り替えてVCXOに供給する。

(もっと読む)

半導体集積回路装置

【課題】遅延を有する論理回路から検出した信号を直接利用して、その論理回路の電源電圧の制御を行うような機構が求められている。

【解決手段】本発明は、本発明は、論理回路と、前記論理回路の遅延の変化に応じた周波数の検出信号を出力する遅延特性検出回路と、前記検出信号に応じて抵抗値が変化する抵抗素子と、前記抵抗素子の抵抗値の変化に応じて参照電圧を出力する参照電圧生成回路と、前記参照電圧を前記論理回路及び遅延特性検出回路に出力する電圧供給回路とを有する半導体集積回路装置である。

(もっと読む)

タイミングリカバリー回路

【課題】 構成を簡易にしたタイミングリカバリー回路を提供する。

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号が入力される端子とVCXO109の入力端子との接続を制御し、異常信号によって接続をオンにするスイッチとを有するタイミングリカバリー回路である。

(もっと読む)

試験測定装置並びに位相拘束ループ及び方法

【課題】消費電力が大きくなく、位相ノイズが小さく、広い同調範囲のPLLを提供する。

【解決手段】位相検出器34は、基準信号路30及び帰還信号路32から入力の位相差を検出し、位相検出器出力を発生する。発振器32は、位相検出器出力に応答し且つこの位相検出器出力に基づいた発振出力Foutを発生する。この発振出力Foutが帰還信号路32に供給される。基準信号路30内のミキサ74は、基準信号Frefをダイレクト・デジタル・シンセサイザ72からの出力と混合する。基準信号路内のスイッチング機構80は、複数の異なるフィルタの1つを選択的にミキサ及び位相検出器の間に直列に配置する。

(もっと読む)

位相調整回路および試験装置

【課題】被測定信号の位相を、基準信号の位相に精度よく合わせることができる位相調整回路を提供する。

【解決手段】被測定信号の位相を調整する位相調整回路であって、トリガ信号を生成するトリガ発生部と、基準信号を受け取り、共通の前記トリガ信号のタイミングで、被測定信号および基準信号を測定し、被測定信号および基準信号のそれぞれの信号レベルの差分に応じた測定結果を出力するレベル比較部と、レベル比較部が出力する信号レベルの差分が略零となるように、被測定信号の位相を調整する信号位相調整部とを備える位相調整回路を提供する。

(もっと読む)

半導体集積回路装置および出力バッファ遅延変動検出方法

【課題】I/Oバッファの実際の配置場所及び実際の動作タイミングにおけるI/Oバッファの同時スイッチングによる出力バッファの遅延変動を容易に検出し、オーバーマージンな設計を回避できるようにした半導体集積回路装置を提供する。

【解決手段】差動アンプ152で、VSS変動の影響を受けている出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP1として求める。差動アンプ153で、VDE変動の影響を受けている出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP2として求める。差動アンプ154で、VDE・VSS変動の影響を受けていない状態での出力バッファ151の遅延を出力バッファ遅延変動検出用信号SAMP3として求める。

(もっと読む)

半導体装置

【課題】テスト中に所望の位相に対して追随できるテスト回路を備え、安価にDDRifのテストを行うことを目的としている。

【解決手段】本発明における半導体装置は、位相シフト量を決定するDLL200と、テストモード時に所定位相ずらす演算回路300と、位相シフト量を設定するレジスタ11〜16と、設定した位相にシフトして信号の送受信を行う伝送回路10とを備える。伝送回路10は、第1の信号を設定した位相にシフトする位相シフタ1と、テストモード時に第1の信号をループバックする双方向バッファ21と、双方向バッファ21から出力された信号の位相をシフトする位相シフタ2と、第3の信号の位相をシフトする位相シフタ3と、テストモード時に第3の信号をループバックする双方向バッファ22と、双方向バッファ22から出力された信号の位相をシフトする位相シフタ4と、位相シフタ2,4の出力信号を取り出すFIFO30とを備える。

(もっと読む)

デジタル位相検知器及びデジタル位相検知信号の発生方法

【課題】フェーズロックループで使用可能なデジタル位相検知器において、サンプリングクロック信号を基準として高い位相分解能で入力クロック信号の位相を検知する。

【解決手段】サンプリングクロック信号はサンプリング14に対して、前もってデジタル的に調節可能な位相変位12へ露呈され、「補助サンプリングクロック信号」CK<1:8>が発生する。サンプリング14は位相検知信号PD OUTの第一のより上位のデジタルコンポーネントOUT1<9:0>を送給する。この第一のデジタルコンポーネントOUT1<9:0>の評価に基づいて、位相変位12が行われ且つ位相検知信号PD OUTの第二デジタルコンポーネントOUT2<12:0>が発生される。補助サンプリングクロック信号CK<1:8>は段階的に調節可能であり、それは各場合においてサンプリングクロック信号CKの1周期よりも小さい。

(もっと読む)

半導体集積回路

【課題】複数のシリアル伝送チャネルで使用するクロックの同期をとる際に、PLL回路から各CDR回路に供給されるクロック配線のレイアウト上の制約を無くし、ジッタの発生の少ない半導体集積回路を提供する。

【解決手段】半導体集積回路は、位相周波数比較回路とチャージポンプとループフィルタと発振回路とを有し、リファレンスクロックに同期した発振出力信号を生成するPLL回路と、発振出力信号とシリアルデータとの位相を調整する複数のCDR回路とを備え、PLL回路はループフィルタから出力された発振回路の発振周波数を制御する制御電圧をディジタルコードに変換し、このディジタルコードをこれら複数のCDR回路に分配する。

(もっと読む)

同期回路

【課題】 リセット端子を持たない1:nDEMUXやn:1MUXの複数個を同期させて並列動作させることが可能な同期回路を実現する。

【解決手段】 クロック信号を入力して作動する複数のカウンタIC手段の動作タイミングを一致させる同期回路において、前記複数のカウンタIC手段のうち、基準となるカウンタIC手段のクロック信号と同期対象となる他のカウンタIC手段のクロック信号との位相差を検出する位相差検出手段と、検出された前記位相差に基づいて前記他のカウンタIC手段のクロック信号の位相を制御する位相制御手段と、を備える。

(もっと読む)

線形位相誤差検出に関する方法及び装置

【課題】超高速且つ高性能な線形位相誤差検出の方法及び検出回路を提供すること。

【解決手段】入力データ信号のエッジとクロック信号のエッジとの間の位相誤差を検出するために使用される方法及び装置を開示する。本発明は超高周波数において並びに線形位相誤差情報が必要な場合において使用される。本発明は任意の集積回路論理技術の利便性を拡張する。これにより周波数適用範囲が倍増するとともに、所望の線形位相誤差を測定する機能が維持される。クロッキング信号を用いてデータ入力信号のサンプリングを行うためにフリップフロップ回路が使用され、立ち上がりエッジのデータと立ち下がりエッジのデータに対して別個に処理が行われた後、両エッジからの位相誤差情報のアナログ式再合成が集積回路の速度による制限のない方法で行われる。

(もっと読む)

半導体集積回路

【課題】複数のシリアル伝送チャネルで使用するクロックの同期をとる際に、PLL回路から各CDR回路に供給されるクロック配線のレイアウト上の制約を無くし、ジッタの発生の少ない半導体集積回路を提供する。

【解決手段】

半導体集積回路は、位相周波数比較回路とループフィルタと発振回路とを有し、リファレンスクロックに同期した発振出力信号を生成するPLL回路と、発振出力信号とシリアルデータとの位相を調整する複数のCDR回路とを備え、PLL回路はループフィルタから出力された発振回路の発振周波数を制御する電圧を電流に変換し、変換後の電流をこれら複数のCDR回路に分配する。

(もっと読む)

2つのPLLを用いた微小時間差回路及び時間測定回路

【課題】1桁以上時間分解能を向上させることができる微小時間差回路及び時間測定回路を提供する。

【解決手段】所定の基準クロック信号を受け、第1発振周波数を発生する電圧制御発振回路を具える第1位相同期ループ回路と、前記第1位相同期ループ回路と同じ基準クロック信号を受け、前記第1発振周波数と異なる第2発振周波数を発生する電圧制御発振回路を具える第2位相同期ループ回路とを具え、前記第1位相同期ループ回路と前記第2位相同期ループ回路の出力信号の遅延時間差から微小時間を得る。

(もっと読む)

21 - 37 / 37

[ Back to top ]