Fターム[5J039JJ20]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 比較結果の出力(アナログ) (180) | デジタル出力 (138)

Fターム[5J039JJ20]に分類される特許

41 - 60 / 138

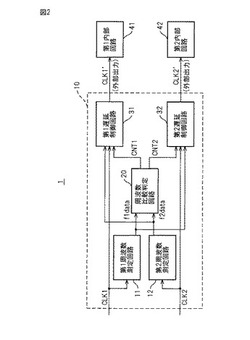

ジッタ低減回路および半導体集積回路

【課題】クロック信号に乗るジッタを低減することが可能なジッタ低減回路および半導体集積回路の提供を図る。

【解決手段】第1クロック信号CLK1の第1周波数を測定する第1周波数測定回路11と、第2クロック信号CLK2の第2周波数を測定する第2周波数測定回路12と、測定された前記第1および第2周波数を比較し、該第1および第2周波数が所定の関係に有るかどうかを判定する周波数比較判定回路20と、前記周波数比較判定回路からの第1制御信号CNT1を受け取り、前記第1クロック信号の遅延を制御して前記第2クロック信号によるジッタを低減する第1遅延制御回路41と、を有するように構成する。

(もっと読む)

信号発生装置

【課題】

積分回路や発振回路に、時間差なく各信号が入力され、さらには、積分回路や発振回路の補正や校正の自由度を高くする。

【解決手段】

複数のアナログ信号を入力し当該アナログ信号をそれぞれ積分した積分信号をそれぞれ出力する積分回路111,112と、各積分信号をそれぞれ入力し、積分信号の大きさを所定のしきい値と比較して比較信号をそれぞれ出力する比較回路121,122と、積分回路のうち少なくとも2つの積分回路の制御端子に接続され、それぞれセットされた時間だけ、他の少なくとも1つの積分回路の積分動作の開始タイミングと異なるタイミングで積分動作を開始させる遅延回路131,132と、比較信号を入力し、これらの入力信号の入力タイミングを比較し、これらの入力タイミングに応じた比較結果信号を出力する信号処理回路14とを備える。

(もっと読む)

発振器制御装置

【課題】安定したPLL動作を確立できる発振器制御装置を提供する。

【解決手段】発振器制御装置は、発振器調整信号OTWに応じた発振周波数の発振信号を出力するデジタル制御発振器100と、発振信号で同期化された基準信号に基づいてカウント値を出力するカウンタ120と、発振信号と基準信号との位相差dを算出する時間デジタル変換器130と、カウント値と位相差とを加算し、加算値を第1位相情報として出力する加算器140と、発振信号の立ち上がりタイミングと基準信号の立ち上がりタイミングとの時間差が所定時間未満である場合に、デジタル制御発振器の発振周波数を設定するための位相制御信号Acc1に基づいて第1位相情報を補正し、第2位相情報を出力する補正部160と、位相制御信号と第2位相情報との差分を平滑化するフィルタ180と、フィルタ出力にパラメータKを乗算して発振器調整信号OTWを出力する乗算器190と、を備える。

(もっと読む)

インピーダンス調整回路及びこれを備える半導体装置

【課題】インピーダンス調整回路における調整誤差を低減する。

【解決手段】レプリカ回路1441,1443のインピーダンスをそれぞれ変化させるカウンタ回路1421,1422と、これらカウンタ回路のカウント値を更新するインピーダンス調整制御回路141とを備える。制御回路141は、レプリカ回路1441のインピーダンスが外部抵抗REのインピーダンスよりも低い状態から高い状態に変化したことに応答してカウンタ回路1421のカウント値更新を終了し、レプリカ回路1443のインピーダンスがレプリカ回路1441のインピーダンスよりも高い状態から低い状態に変化したことに応答してカウンタ回路1422のカウント値更新を終了する。これにより、レプリカ回路1441,1443にて生じる調整誤差が相殺される。

(もっと読む)

2相カウンタおよびカウンタシステム

【課題】カウント動作を高速でも容易に行えるようにすること。

【解決手段】A相パルスの前パルスエッジとB相パルスの前パルスエッジとのエッジ位相差と、A相パルスの後パルスエッジとB相パルスの前パルスエッジとのエッジ位相差とを検出し、上記両エッジ位相差の比率を演算し、上記エッジ位相差比率に対応して割り当てられたカウント値を演算する2相カウンタ。

(もっと読む)

位相比較器、PLL回路、及び位相比較器の制御方法

【課題】電圧制御発振器VCOの出力信号と参照信号との位相差をデジタル信号として高精度に検知できる位相比較器、PLL回路、及び位相比較器の制御方法を提供する。

【解決手段】各々複数段縦列接続され、基準信号および対象信号が入力される遅延回路と、各々の段の遅延時間の差により、基準信号と対象信号との位相差を出力する保持回路と、その出力結果を元に、遅延素子の時間差及び大小を変更する論理回路とを備えた。

(もっと読む)

半導体集積回路装置および遅延路の制御方法

【課題】電力効率を向上させる。

【解決手段】クロック信号CLKに同期して動作する2つの同期動作回路11、12間を並列形態で接続して信号伝送可能とされる複数の遅延路13a、13b、・・13nと、複数の遅延路13a、13b、・・13nにおけるそれぞれの遅延時間を検出する遅延検出部14と、遅延検出部14の検出結果に基づいて複数の遅延路13a、13b、・・13nの内の一の遅延路を選択し、選択した一の遅延路以外における信号伝送を阻止するように制御する制御部15と、を備える。

(もっと読む)

デューティ感知回路およびこれを備えるデューティ補正回路

【課題】デューティ補正回路のロッキングタイムを減らし、正確なデューティの補正が可能となり、多様な周波数のクロックについてデューティ補正を可能にするデューティ補正回路を提供すること。

【解決手段】本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、前記出力クロックのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、前記差異値を累積して前記デューティ調節コードを生成する累積部130とを備える。

(もっと読む)

DLL回路及びその制御方法

【課題】本発明は、短いロッキングタイムを有する多相DLL回路及びその制御方法を提供する。

【解決手段】本発明のDLL回路は、 基準クロックを遅延させてDLLクロックを生成するが、制御電圧のレベルに応じて遅延量を調整する遅延手段;制御電圧の初期レベルを制御し、検出イネーブル信号を生成する初期動作制御手段;及び、検出イネーブル信号に応じて前記基準クロック及びDLLクロックの位相を比較して、制御電圧を生成する遅延制御手段を含むことを特徴とする。

(もっと読む)

半導体装置、内部信号タイミング回路、及び遅延時間測定方法

【課題】内部信号のタイミングを測定する場合、チップ内に形成されたトランジスタ等の素子における場所依存性によって特性が異なる場合にも、内部信号のタイミングを測定できる測定回路を提供する。

【解決手段】内部で実信号として用いられる第1及び第2の内部回路制御信号を生成する内部回路と、内部回路を通して受信される第1及び第2の内部回路制御信号を遅延時間測定開始信号及び遅延時間測定終了信号として受け、当該遅延時間測定開始信号及び遅延時間測定終了信号間の遅延時間を測定し、出力する遅延時間測定回路を備えた内部信号タイミング回路及び当該回路を含む半導体装置。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

半導体装置

【課題】PVT変動による遅延制御回路の遅延量変動を正しく補正する。

【解決手段】互いに動作条件が異なる第1及び第2の遅延素子列121,122と、第1及び第2の遅延素子列121,122に同時に入力されたパルス信号Pの伝搬速度差を検出する検出回路123と、検出回路123による検出結果に基づいて選択信号SELを生成する設定回路124とを備える。選択信号SELは、基準信号を遅延させることによって動作タイミング信号を生成する遅延制御回路130に供給され、その遅延量は選択信号SELによって調整される。これにより、PVT変動を見越して遅延制御回路の遅延量を大きく設計しておく必要がなくなるため、パフォーマンスの低下を防止することが可能となる。

(もっと読む)

信号処理装置及び信号処理方法

【課題】ロック状態を維持したまま、発振周波数のVCO制御電圧特性を粗調整する。

【解決手段】VCO63は、トランジスタを内蔵し、入力されたVCO制御電圧に対応する発振周波数を発生させ、LPF131a乃至131dは、VCO63が内蔵するトランジスタのゲートに、予め決められた変化率でトランジスタのゲート電圧を変化させる入力電圧を入力し、VCO制御電圧に対する、発振周波数のVCO制御電圧特性を粗調整する。本発明は、例えばPLL回路やCDR回路に適用することができる。

(もっと読む)

信号再生回路向け位相比較回路及び信号再生回路向け位相比較回路を備える光通信装置

【課題】 1/Nレート構成に対応可能な高精度な位相比較回路を得る。

【解決手段】それぞれ、N相クロック信号CLKの各クロック信号を、受信データ信号DINの立ち上がりに同期してトラックホールドするN個のトラックホールド回路を備える。これらのN個のトラックホールド回路の出力から、受信データ信号DINの立ち上がりエッジが、クロック信号CLKの立ち上がりエッジに位置しているクロック信号をトラックホールドしているもののみをセレクタで選択して、位相差信号として出力する。

(もっと読む)

位相比較回路

【課題】D−FFの内部遅延が無視できない高速動作時において位相比較回路の低消費電力化を実現する。

【解決手段】マスタースレーブマスター型D−FF11は、第1のM−FF11−1,S−FF11−2および第2のM−FF11−3が縦続接続され、入力NRZデータ信号をクロック信号に応答して識別し、S−FFおよび第2のM−FFから出力する。遅延回路4は、入力NRZデータ信号をS−FFと同じ時間だけ遅延させる。第1のEXOR回路7は遅延回路の出力とS−FFの出力の排他的論理和演算を行ない、第2のEXOR8はS−FFの出力と第2のM−FFの出力の排他的論理和演算を行なう。加算器9は第1のEXOR回路の出力と第2のEXORの反転出力を加算する。

(もっと読む)

半導体集積回路

【課題】クロック信号の位相、デューティー比等の変動に対し耐性の強い、小型の半導体集積回路を提供する。

【解決手段】複数配設される回路部と、クロック信号の立ち上がりエッジから前記クロック信号を逓倍した周期の第1信号を生成する第1カウンタと、前記クロック信号の立ち下がりエッジから前記クロック信号を逓倍した周期の第2信号を生成する第2カウンタと、前記第1信号が転送される第1ラインと、前記第2信号が転送される第2ラインと、前記第1ライン及び前記第2ラインと接続され前記第1信号と前記第2信号との位相差から第3信号を生成し前記回路部に前記第3信号を出力する位相比較器と、を備え、前記位相比較器は、前記第1ライン及び前記第2ライン上に配設され且つ前記第1ライン及び前記第2ラインの末端と前記回路部との間に複数配設される。

(もっと読む)

デジタル位相検出器及びデジタル位相同期回路

【課題】デジタル位相検出器の時間分解能をデジタル制御し、回路規模・消費電力を低減する。

【解決手段】信号S1が入力される直列に接続された第1の遅延素子1011〜101Nと、信号S2が入力される直列に接続された第2の遅延素子1021〜102Nと、各々の第1の遅延素子の出力が与えられ、各々の第2の遅延素子の出力をクロックとするラッチ回路1031〜103Nと、前記ラッチ回路の出力値に基づいて信号S1のパルス幅を示すデジタルコードPWmを算出して出力するデコーダ回路104と、デジタルコードPWmと所定のデジタルコードPWrとを比較し、比較結果を出力する比較器105と、前記比較結果に基づいて前記第1及び第2の遅延素子の少なくともいずれか一方の遅延時間を制御する遅延制御回路106と、を備える。

(もっと読む)

半導体メモリ装置及びその駆動方法

【課題】遅延固定ループで反映される遅延の程度を測定して読み出し命令に反映することにより、CASレイテンシに対応する最終出力イネーブル信号を生成することができる半導体メモリ装置を提供すること。

【解決手段】本発明の半導体メモリ装置は、遅延固定ループ310と、外部クロック信号に同期化したロック完了情報に応答して基準クロック信号とフィードバッククロック信号との間の遅延の程度を測定し、これを遅延測定値として出力する遅延及び遅延時間測定手段330と、外部クロック信号に同期化した読み出し命令情報を、基準クロック信号とDLLクロック信号との間の遅延の程度に対応する分だけ遅延させ、遅延測定値及びCASレイテンシ情報に対応してDLLクロック信号に同期化させ、最終出力イネーブル信号として生成する出力イネーブル信号生成手段350と、を備える。

(もっと読む)

デジタル制御発振器及びこれを用いた位相同期回路

【課題】発振周波数を線形に近くかつきめ細やかに制御可能なデジタル制御発振器を提供する。

【解決手段】正相発振信号を出力する正端子213と、逆相発振信号を出力する負端子214と、センタータップ210とを有し、正端子とセンタータップとの間の任意の位置に第1の接点211を備え、負端子とセンタータップとの間の第1の接点に対応する位置に第2の接点212を備える差動インダクタ200と、正端子と負端子との間に接続され、第1のデジタル制御コードによってキャパシタンスを2値に変化させる第1の可変キャパシタを複数含む第1の可変キャパシタバンク220と、第1の接点と第2の接点との間に接続され、第2のデジタル制御コードによってキャパシタンスを2値に変化させる第2の可変キャパシタを複数含む第2の可変キャパシタバンク240と、正端子と負端子との間に接続される負性抵抗230とを具備する

(もっと読む)

位相同期ループ回路の制御方法及び位相同期ループ回路

【課題】ロックアップ時間を短縮すること。

【解決手段】PLL回路20の位相比較器23は、基準信号frと比較信号fpの位相を比較し、両信号fr,fpの位相差に応じた信号を出力する。ループフィルタ25は強誘電体容量C1を含み、位相比較器23の出力信号に応じたチャージポンプ24から出力される位相差電流IPにより直流電圧を生成するとともに、その直流電圧を平滑化して制御電圧VCを生成する。VCO26は、制御電圧VCに応じた周波数の出力信号foを生成する。カウンタ31は、入力信号fiをカウントし、カウント値と第1の設定値,第2の設定値とを比較し、第1の期間、強誘電体容量C1を高電位電源VDDの電源線に接続し、第2の期間、強誘電体容量C1と低電位電源VSSの電源線を接続する。

(もっと読む)

41 - 60 / 138

[ Back to top ]