Fターム[5J039JJ20]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 比較結果の出力(アナログ) (180) | デジタル出力 (138)

Fターム[5J039JJ20]に分類される特許

101 - 120 / 138

時間計測回路

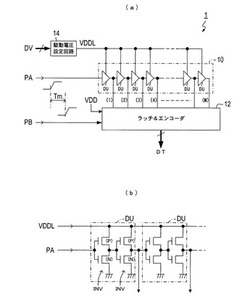

【課題】短い時間幅の高分解能な計測と長い時間幅の低分解能な計測とを、回路規模を大幅に増大させることなく、いずれも実現させることが可能な時間計測回路を提供する。

【解決手段】駆動電圧VDDLに応じた遅延時間で信号を遅延させる遅延ユニットDUをM(Mは正整数)段直列接続してなり、起動用パルスPAの入力により起動され、各遅延ユニットDUにてパルス信号を順次遅延させながら伝送するパルス遅延回路10と、計測用パルスPBが入力されると、パルス遅延回路10内でのパルス信号の位置を検出(ラッチ)し、その検出結果を、起動用パルスPAの入力から計測用パルスPBの入力までの時間Tm内にパルス信号が通過した遅延ユニットDUの段数を表す所定ビットのデジタルデータDTに変換して出力するラッチ&エンコーダ12と、電圧設定データDVに従った大きさの駆動電圧VDDLを発生させる駆動電圧設定回路14とを備える。

(もっと読む)

デジタル型ヘリウム−ネオン安定化レーザ

【目的】 安定化のために、デジタル量を用いる安定化ヘリウム−ネオンレーザの高度の安定度をうるため、デジタルのパルスの形状を正確に揃える手段の提供を行なうと共に、前記安定化のためのデジタル量のパルスの周波数を正確に一定にする手段の提供を行なうことを目的とする。

【構成】

レーザから安定化のために使用出来るデジタル量のパルス周波数を、基準周波数を完全に、しかも安定に一致させるため、ダイオードの順方向の電圧を利用して、正負のパルスの基線を零ボルトにし、さらに、このデジタル量をアナログ量に変換する際、F/V変換回路と正負のパルスの電荷をゆっくり積分する回路を並列にして誤差信号の値を完全に零にしている。

(もっと読む)

位相調整回路装置及びタイミング調整回路システム

【課題】 所定の入力信号または出力信号について製造バラツキや電源電圧や温度変化の影響を少なくし、適切なタイミングでの動作を実現する位相調整回路装置を提供する。

【解決手段】 2つの入力クロック信号の位相差に応じた電圧の位相差検出信号を出力する位相比較回路2と位相差検出信号Sfの電圧値に応じた周波数で発振する基準クロック信号C0を出力する電圧制御発振回路3を有する位相同期回路8、位相の異なる複数のクロック信号C6の1つを選択して位相調整用の参照クロック信号C3として出力する位相選択回路4、及び、第1入力クロック信号C1の信号レベルの変化タイミングを参照クロック信号C3の立ち上がりまたは立ち下がりタイミングに合わせる位相調整を行うフリップフロップ回路5を備え、位相調整後の第1入力クロック信号C4と基準クロック信号C0が外部回路を経由して得られる遅延クロック信号C2を位相比較回路2に入力する。

(もっと読む)

位相比較器

【課題】フルレートとハーフレートの両方に対応した位相比較器を得る。

【解決手段】データ信号の立ち下がりタイミングでクロック信号の振幅値を検出する第一の検出手段1と、データ信号の立ち上がりタイミングでクロック信号の振幅値を検出する第二の検出手段2と、第一の検出手段1がクロック信号の立ち上がり状態又は立ち下がり状態の振幅値を検出しているのかを識別して第一の識別結果を出力し、第二の検出手段2がクロック信号の立ち上がり状態又は立ち下がり状態の振幅値を検出しているのかを識別して第二の識別結果を出力するエッジ比較手段3と、第一の識別結果に応じて第一の検出手段1の出力の極性を反転する第一の極性反転手段4と、第二の識別結果に応じて第二の検出手段2の出力の極性を反転する第二の極性反転手段5と、データ信号の極性に応じて第一又は第二の極性反転手段4、5の出力値を選択して出力する信号選択手段6とを設けた。

(もっと読む)

位相同期ループ回路及びこの位相同期ループ回路の制御方法

【課題】電圧制御水晶発振器の経年変化による異常が発生しても、この異常を確実に検出できるようにした位相同期ループ回路を提供する。

【解決手段】カウンタ111にて外部クロック信号から内部クロック信号に同期した矩形波信号を生成するとともに、カウンタ112−2にて内部クロック信号から外部クロック信号の異常を検出するために必要なウインドウ信号W1を生成し、カウンタ115にて内部クロック信号から電圧制御水晶発振器12の異常を検出するために必要なウインドウ信号W2を生成し、異常判定制御部114−2にて矩形波信号の立ち上がりがウインドウ信号W1,W2のハイレベル期間内に入っているか否かを判定し、ウインドウ信号W1のハイレベル期間に入っていて、ウインドウ信号W2のハイレベル期間内に入っていない場合に、電圧制御水晶発振器12の異常と判定するようにしている。

(もっと読む)

ディジタル位相同期装置

【課題】入力された正弦波と周波数が等しく、かつ位相が同期した正弦波を、簡易で正確に、出力する装置を提供する。

【解決手段】位相差検出回路1は、外部から入力された第一の正弦波と正弦波生成回路5より出力する第二の正弦波との位相差を、ディジタル信号処理により算出する。その算出値に基づいて第二の正弦波の位相と周波数を調整するので、正弦波生成回路5は入力された第一の正弦波に周波数が等しく、かつ位相が同期した第二の正弦波を簡易に正確に出力することができる。

(もっと読む)

パルス位相差符号化回路

【課題】入力される電圧信号のレベルが回路の動作電源電圧より上昇した場合でも、正確な符号化動作を行うことができるパルス位相差符号化回路を提供する。

【解決手段】A/D変換回路11を構成するパルス位相差符号化回路13において、カウンタ2のカウント値をデータラッチ回路4にラッチさせるタイミング信号を生成するため、符号化周期信号PBに所定の遅延時間T12を付与する遅延回路12を、電圧入力端子に与えられる電圧信号Vinのレベルが上昇するのに応じて遅延時間が短縮されるように構成する。具体的には、遅延回路12を、リングディレイライン1を構成するNOTゲートと同じNOTゲートを、リングディレイライン1を構成する直列段数の1/2となる段数で直列接続して構成し、それらのNOTゲートを、A/D変換対象となる入力電圧Vinを電源として動作させる。

(もっと読む)

遅延素子の遅延寄与決定を有する時間−デジタル変換

【課題】本発明は、時間−デジタル変換に対応する方法に関する。

【解決手段】遅延素子(126.1、...、126.N)の少なくとも1つのチェーンを備える時間−デジタル変換器(110)であって、前記遅延素子(126.1、...、126.N)のチェーンのステータスが変換する時間間隔に関連するデジタル信号を表し、前記時間−デジタル変換器(110)が、遅延素子(126.1、...、126.N)の中で転送されるパルスを基準にして統計的に等しく分散された可変位置を有するトリガ信号(154)を供給する手段(156)であり、前記較正トリガ信号(154)に応じて遅延素子(126.1、...、126.N)の前記チェーンのステータスを捕捉する手段(130)であって、前記ステータスは前記遅延素子(126.1、...、126.N)の遅延時間によって決まり、前記較正トリガ信号(154)に応じて、パルス位置の発生に基づく前記遅延素子(126.1、...、126.N)の全遅延に対する少なくとも幾つかの前記遅延素子(126.1、...、126.N)の実寄与を決定する手段と、前記時間間隔を前記デジタル信号(168)に変換する際に、少なくとも幾つかの前記遅延素子(126.1、...、126.N)の前記実寄与を考慮する手段(164)とを備えることを特徴とする時間−デジタル変換器(110)。

(もっと読む)

位相比較回路およびそれを用いたPLL周波数シンセサイザ

【課題】高速に周波数切り換えが可能であり、且つ小型でスプリアスを低減することが可能な位相比較回路を提供する。

【解決手段】本発明の一実施形態に係る位相比較回路は、制御回路からの制御信号に基づいて、クロックを分数分周した分数分周信号を生成する分数分周器と、分数分周信号を整数分周した第1の整数分周信号を生成する第1の整数分周器と、基準クロックを整数分周した第2の整数分周信号を生成する第2の整数分周器と、切換信号に基づいて、分数分周信号と第1の整数分周信号とのいずれか一方を選択的に出力する第1の選択回路と、制御回路からの切換信号に基づいて、基準クロックと第2の整数分周信号とのいずれか一方を選択的に出力する第2の選択回路と、第1の選択回路からの出力信号と第2の選択回路からの出力信号との周波数差および位相差を表す比較信号を生成する位相比較器とを備えている。

(もっと読む)

クロック信号を発生するクロック発生回路及び方法

【課題】クロック信号を発生するクロック発生回路及び方法を公開する。

【解決手段】クロック発生回路は、外部クロック信号を直接受信して、反転された外部クロック信号を発生するインバータと、一番目のループ回路が反転外部クロック信号を受信してn(nは2以上の定数)個のノードをそれぞれ備え、M−1(Mは1以上の定数)個のループ回路のそれぞれがn個のノードの対応する1つからn個の中間内部クロック信号それぞれを発生し、n個の中間内部クロック信号の周波数が外部クロック信号及び反転外部クロック信号の周波数の倍数であることを特徴とする直列に配列されたM個のループ回路と、それぞれが直列に接続されて以前のループ回路から対応する中間内部クロック信号を受信し、対応する中間内部クロック信号を次のループ回路に出力するM−1個のインバータそれぞれと、を具備するn個のインバータの集合で構成されている。

(もっと読む)

デジタル位相検出器

【課題】 従来、デジタル位相検出器における位相検出限界は、遅延素子の遅延時間により決定されるため、例えば、PLL回路に低ジッタ特性が要求される場合には、全デジタルPLL回路は不適当であった。

【解決手段】 第1のクロックCLKfを遅延する複数の第1の遅延素子1011〜101nと、第2のクロックCLKrを遅延する複数の第2の遅延素子1021〜102nと、前記第2の遅延素子により順次遅延された前記第2のクロックREF1〜REFnに従って、前記第1の遅延素子により順次遅延された前記第1のクロックFB1〜FBnを取り込み、相対的な位相関係を表すデジタル値Q1〜Qnを保持する複数のデータ保持回路1031〜103nと、を備えるように構成する。

(もっと読む)

差動増幅装置

【課題】1対の入力信号の同相成分に比べ、電圧レベル差が少さい場合でも、これを感知して論理レベルに応じて出力できる差動増幅装置を提供すること。

【解決手段】本発明の差動増幅装置は、第1(IN)及び第2入力信号(INB)が有する電圧レベルの差を感知及び増幅して、第1(OUT)及び第2出力信号(OUTB)として出力するための増幅手段と、前記第1出力信号を第1フィードバック信号(OUT_FD)として、前記第2出力信号を第2フィードバック信号(OUTB_FD)として受けて、前記第1フィードバック信号と前記第2フィードバック信号との電圧レベルの差を増幅するためのフィードバック手段(NM9,10、MN15,16)とを備える。

(もっと読む)

多相デジタルサンプリングのための装置および方法

【課題】入力信号周波数と基準信号周波数との間の関係を決定する方法および装置を提供する。

【解決手段】本システムは、基準信号から複数の内部基準信号を得る。内部基準信号は、レベル検出回路20aに与えられる。レベル検出回路20aは、入力信号をある期間内にある回数サンプリングする。これらのサンプルに関連付けられた値は、前回の期間からのサンプルの1つの値と同様に記憶される。記憶されたサンプルの相関が取られ、入力信号周波数と基準信号周波数との間の関係が得られる。

(もっと読む)

半導体装置の二重基準入力受信器及びその入力データ信号の受信方法

【課題】半導体装置の二重基準入力受信器及びその入力データ信号の受信方法を提供する。

【解決手段】第1及び第2入力バッファと位相検出器とを備える入力受信器であって、第1入力バッファは、クロック信号によって同期して、イネーブルまたはディセーブルされ、ポジティブ入力端子に入力される入力データ信号とネガティブ入力端子に入力される第1基準電圧との電圧差を感知して増幅し、第2入力バッファは、クロック信号によって同期して、イネーブルまたはディセーブルされ、ポジティブ入力端子に入力される第2基準電圧とネガティブ入力端子に入力される入力データ信号との電圧差を感知して増幅する。第1基準電圧のレベルは、入力データ信号のレベルの中間レベルより高く、第2基準電圧のレベルは、入力データ信号のレベルの中間レベルより低い。位相検出器は、第1入力バッファの出力信号と第2入力バッファの出力信号との位相差を検出し、検出された位相差に対応する出力信号を発生させる。

(もっと読む)

位相同期ループ回路での周波数検出器及び周波数エラーの検出方法

【課題】 位相同期ループ回路において周波数エラーを高速で検出できる周波数検出器及び周波数エラーの検出方法を提供する。

【解決手段】 予測されたランレングス信号の予測分布度に基づいて、周波数検出周期の間にサンプルされたRF信号からランレングス信号を検出するランレングス信号検出ユニットと、周波数検出周期の間に、検出されたランレングス信号をカウントする少なくとも一つのカウンタを備えたカウンタユニットと、サンプルされたRF信号のパッシングエッジをカウントして、周波数検出周期を制御するエッジカウンタと、カウンタユニットに含まれたカウンタによりカウントされた値及び所定の基準値を利用して、周波数検出周期の間の周波数エラーを生成する周波数エラー生成ユニットとを備える。

(もっと読む)

信号伝送回路

【課題】 クロック信号を含むいずれの信号であっても、その信号のデューティを維持することができる信号伝送回路を提供する。

【解決手段】 第1の配線経路11および第1のデューティ調整回路12からなる本経路の特性と同一の特性を有する、第2の配線経路22および第2のデューティ調整回路23からなるレプリカ回路を備え、本経路,レプリカ経路に1つのエッジから作られた相補信号を入力し、これら本経路からの信号INRとレプリカ経路からの信号INFとの双方の信号の位相を位相比較器30で比較し、比較結果に応じてそれら双方の信号INR,INFの位相が揃うように制御回路40で第1,第2のデューティ調整回路12,23を制御する。

(もっと読む)

デジタル制御型位相合成回路システム

【課題】 ジッタ耐性を強化し、かつロックレンジを拡大するデジタル制御型位相合成回路システムを得る。

【解決手段】 位相の異なる2つのクロックと制御信号が入力され、制御信号による重み付けに基づいて、これらのクロックの中間の位相をもつ出力クロックを合成する位相合成回路と、出力クロックの位相と基準クロックの位相とを比較するバイナリ型位相比較回路と、バイナリ型位相比較回路による比較結果に基づいて第1のカウント値をカウントアップ又はカウントダウンし、第1のカウント値の最上位ビットの値を出力し、第1のカウント値にキャリー又はボローが発生した場合にクロックパルスを出力する第1のアップダウンカウンタと、クロックパルスを動作クロックとし、第1のカウント値の最上位ビットに基づいて第2のカウント値をカウントアップ又はカウントダウンし、第2のカウント値を制御信号として出力する第2のアップダウンカウンタとを有する。

(もっと読む)

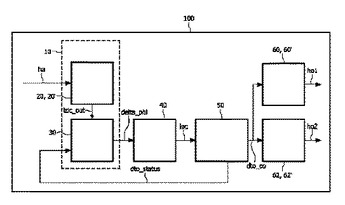

位相ロックループ回路装置及びこれを利用したクロック信号発生方法

回路装置(100)、特にサブクロックまたはサブピクセルの正確な位相測定及び位相発生用の位相ロックループ、並びにこれに対応する方法を、クロック乗算器位相ロックループを時間−ディジタル変換器の後方に設けず、アナログ遅延線も信号除算器ユニットも、ディジタルランプ発振器または離散時間発振器とディジタル−時間変換器との間に設けず、ディジタル環境におけるノイズ及び接地バウンスの影響を受け易いアナログ回路がより少ない方法でさらに発展させるために、少なくとも1つの位相測定ユニット(10);少なくとも1つの位相検出器ユニット(30)の少なくとも1つの出力信号(delta_phi)を供給される少なくとも1つのループフィルタユニット(40, 40’);ループフィルタユニット(40, 40’)少なくとも1つの出力信号、特に少なくとも1つの増分(inc)を供給される少なくとも1つのディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)を設け、ディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)の少なくとも1つのレジスタユニット(54, 54’)の状態信号(dto_status)は位相検出器ユニット(30)に入力信号として供給され、さらに、少なくとも1つのディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)の少なくとも1つの出力信号(dto_co)を供給されて少なくとも1つの出力信号(ho1, ho2)発生する少なくとも1つのディジタル−時間変換器ユニット(60, 62, 60’, 62’)を設けることを提案する。  (もっと読む)

(もっと読む)

クロックジェネレータ

【課題】 チャージポンプ回路の出力電圧変動を抑制する。

【解決手段】 PLL回路1は、位相比較器2、チャージポンプ回路・LPF部3、VCO4、及び分周器5から構成され、チャージポンプ回路・LPF部3には、チャージポンプ回路6の充電電流及び放電電流を同一にするための補正チャージポンプ電流をチャージポンプ回路6に供給するチャージポンプ電流補正回路9が設けられている。

(もっと読む)

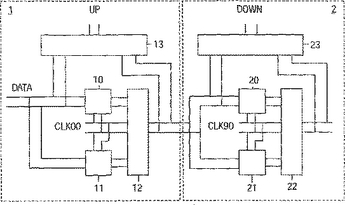

多重送信用ラッチ付き線形位相検出器

線形位相検出器は、クロック抽出器およびデータ再生器内で使用するために、第1および第2クロック信号(CLKOO,CLK90)を受信して第1および第2制御信号(UP,DOWN)を生成する回路(1,2)を備え、これらの回路は、入力および出力との間の長い経路の長さと多くの動作により大きな遅延を有する(洞察)。これらは、それぞれの回路(1,2)に2つの並列のラッチ(10,11,20,21)と、これらのラッチの出力信号を多重送信するマルチプレクサ(12,22)を与えることにより、より速くさせることが可能である(基本概念)。データ信号は第1回路(1)に供給され、第1回路出力信号は第2回路(2)に供給される。それぞれがまた2つのラッチとマルチプレクサを備える第3および第4回路(3,4)を導入することにより、高速線形位相検出器は、多数のトランジスタから独立した、データ信号におけるゲインを有するように構成されており、これは長所である。それぞれの回路(1,2,3,4)の論理回路(13,23)は、加算器/減算器(5)に結合される。  (もっと読む)

(もっと読む)

101 - 120 / 138

[ Back to top ]