Fターム[5J039JJ20]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 比較結果の出力(アナログ) (180) | デジタル出力 (138)

Fターム[5J039JJ20]に分類される特許

121 - 138 / 138

高速線形位相検出器

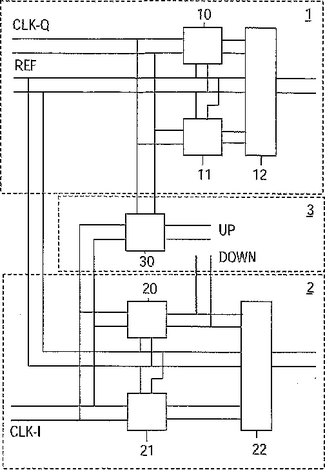

第1および第2(位相)制御信号(UP、DOWN)を生成するために基準信号(REF)および第1および第2クロック信号(CLK−Q、CLK−I)を受信する回路を備える乗算器回路、復調器および受信機用の線形位相検出器は、長い経路長および入力と出力との間の多くの動作のために大きな遅延を有する(洞察)。各回路(1、2)に2個の並列ラッチ(10、11、20、21)およびラッチ出力信号を多重化するための多重化装置(12、22)を備えることによって、線形位相検出器をより高速にすることができる(基本概念)。前記多重化装置は、周波数検出器に供給されるべき(周波数制御)信号を生成し、第3回路(3)が前記(位相)制御信号(UP、DOWN)のうちの少なくとも1つを生成している。前記第3回路(3)は、前記第1(位相)制御信号(UP)を生成するラッチ(30)を備え、第2回路(2)のラッチの1つ(20)が第2(位相)制御信号(DOWN)を生成している。または、前記第3回路(3)は、4個のEXORゲート(31〜34)を備える論理回路(31〜34)を備える。第5EXORゲート(35)が、第3回路(3)を平衡させるために使用される。  (もっと読む)

(もっと読む)

半導体装置の遅延調節回路、及び遅延調節方法

【課題】動作条件の変化による遅延時間を検出し、この遅延時間を一定範囲内に入るように調節可能な遅延調節回路が開示される。

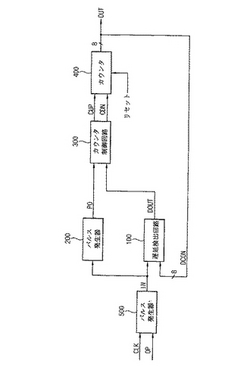

【解決手段】遅延調節回路は、遅延検出回路、第1パルス発生器、カウンタ制御回路、及びnビットカウンタを備える。遅延検出回路は、出力信号に応答して入力信号を第1時間遅延させ、入力信号と遅延した入力信号とを互いに比較し、第1信号を発生させる。第1パルス発生器は、入力信号に応答して第2信号を発生させる。カウンタ制御回路は、第1信号と第2信号とに応答してカウントアップ信号とカウントダウン信号とを発生させる。nビットカウンタは、カウントアップ信号とカウントダウン信号に応答して第1時間を2n(nは自然数)区間に分けるためのデジタル出力信号を発生させる。従って、遅延調節回路は、半導体製造工程、温度、電圧などの条件が変化しても遅延時間を一定範囲内に入るように調節することができる。

(もっと読む)

比較器

【課題】小面積で計算速度が速い比較器を提供する。

【解決手段】比較器は、各々の入力端にクロック信号が共通して入力される第1及び第2遅延回路と各々の第1入力端に第1遅延回路の出力信号及び第2遅延端の出力信号が各々入力される第1及び第2論理ゲートを含む第1ラッチ回路、及び第1論理ゲートの出力端から出力される信号及び前記第2論理ゲートの出力端から出力される信号をラッチする第2ラッチ回路を備える。第1遅延回路の遅延時間は外部から入力される第1デジタル信号により制御される可変の遅延時間であり、前記第2遅延回路の遅延時間は外部から入力される第2デジタル信号により制御される可変の遅延時間である。

(もっと読む)

半導体集積回路装置

【課題】 高信頼性のデッドロック解除機能を持つPLL回路を備えた半導体集積回路装置を提供する。

【解決手段】 PLL回路のデッドロック解除回路として、制御電圧モニタ回路によりPLL回路の位相比較出力に対応したVCO制御電圧が規定値を超えることを検出し、位相モニタ回路により基準信号と帰還信号の位相が入力半サイクル以上外れていることを検出し、判定回路により上記制御電圧モニタ回路と位相モニタ回路の両検出信号が成立した場合にのみデッドロック状態と判定して、上記VCO制御電圧を強制的に下げてデッドロック状態の解除を行う。

(もっと読む)

半導体装置

【課題】

オシレータから出力されるクロックに発振異常が発生した場合、その異常に対応してマイクロコンピュータの動作を適切に停止させる。

【解決手段】

発振器と、発振異常検出部とを具備する半導体装置を構成する。発振異常検出部は、その発振器から出力されるクロックを計測して得られたカウント値に基づいてその発振器の周波数を特定する。そして、その周波数が所定の周波数範囲外のときに、発振異常信号を生成する。

(もっと読む)

位相比較器及び位相比較器を有する半導体装置

【課題】 位相比較器の位相差の検出精度を高めることである。

【解決手段】 位相差信号生成回路24は、エッジ検出フラグ生成回路22で検出される比較対象信号COMP1の立ち上がりに同期した信号と、エッジ検出フラグ生成回路23で検出される比較対象信号COMP2の立ち上がりに同期した信号から比較対象信号COMP1と比較対象信号COMP2の位相差に応じた期間ハイレベルとなる信号C_SIGNALをトライステートバッファ12の制御端子に出力する。ステータス管理回路25は、比較対象信号COMP1と比較対象信号COMP2位相の進みまたは遅れに応じた信号A_SIGNALをトライステートバッファ12の入力端子に出力する。

(もっと読む)

ディジタル回路電源電圧制御システム

【課題】

アナログ回路とディジタル回路が同一半導体基板上に集積化されたシステムにおいて、ディジタル回路が動作したときのディジタルノイズを減少させる。

【解決手段】

本発明は、ディジタル回路と同一の素子で構成されたクロック信号発生回路を設けて、そのクロック信号発生回路の出力信号と基準信号との位相差からディジタル回路の電源電圧を調整してディジタルノイズを低減するよう構成し、ディジタル回路と同一半導体基板上に集積化されたアナログ回路への影響を少なくして、通信システムにおける受信感度などの品質劣化を防止できる。

(もっと読む)

位相比較器

【課題】比較演算に係る論理回路の回路規模を削減し、その結果、その回路面積を縮小し、遅延時間を短縮し、消費電力を低減することができる位相比較器を提供する。

【解決手段】位相比較器は、データとデータのハーフレートの位相が90°ずつずれた4相の第1〜第4のクロックとの間の位相を比較するもので、データを4相の第1〜第4のクロックで各々サンプリングする第1〜第4のサンプリング回路と、第1および第2のサンプリング回路によって、その位相が隣接する2相の第1および第2のクロックで各々サンプリングされた2つのデータ同士を比較し、両者が異なる場合に第1のアップ信号を出力する第1の比較回路と、第4および第1のサンプリング回路によって、その位相が隣接する2相の第4および第1のクロックで各々サンプリングされた2つのデータ同士を比較し、両者が異なる場合に第1のダウン信号を出力する第2の比較回路とを備える。

(もっと読む)

位相誤同期検出回路

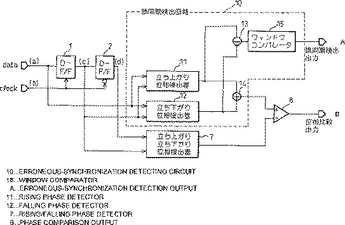

位相比較回路に関し、特にデータとクロックとの位相差の比較において、データのデューティが100パーセントからずれたときに生じる位相の誤同期を検出する位相誤同期検出回路を提供する。データとクロックとの位相差を検出する位相比較器において、その位相誤同期検出回路は、データの立ち上がりとクロック位相との位相差を検出してその平均位相差を出力する第1の位相検出部と、データの立ち下がりとクロック位相との位相差を検出してその平均位相差を出力する第2の位相検出部と、前記第1の位相検出部からの平均位相差と前記第2の位相検出部からの平均位相差との差が所定の範囲を超えるときに位相誤同期と判定する位相誤同期判定部と、により構成する。  (もっと読む)

(もっと読む)

可変遅延回路及び半導体集積回路装置

【課題】 高い精度で遅延時間を制御できる可変遅延回路を用いた半導体集積回路装置を提供することを目的とする。

【解決手段】入力クロック信号を遅延させる第1のDLL回路3と、第1のDLL回路よりも高い精度で遅延を制御できる第2のDLL回路10とを有し、第1及び第2のDLL回路の位相比較(31、14)を独立に動作させ、かつ第2のDLL回路の遅延量制御を第1のDLL回路の動作に従属させることで、入力クロック信号に対し所定の位相関係を有する出力クロック信号を出力するように第1及び第2のDLL回路で遅延を与える半導体集積回路装置。

(もっと読む)

等間隔パルス列生成装置および生成方法

【課題】 低消費電力を図り、かつ周波数の変動を生じない精度の良い出力波を得ることのできる位相合成装置および位相合成方法を提供する。

【解決手段】

クロックに同期した位相データと所定電圧値とのクロス点前後の位相データの差分をサンプルホールドした後アナログ値に変換するD/A変換器2と、D/A変換器により変換されたアナログ値を電流に変換する電流源3および該電流を時間的に積分するコンデンサ4からなる積分器5と、積分器の電荷を放電するリセット回路6とを備える直線補間回路を有する位相合成装置およびそれを用いた位相合成方法により、コンデンサのゲイン変化やD/A変換におけるDCオフセット誤差に影響されることなく、ジッタの小さい精度の良い出力波を合成することができる。

(もっと読む)

変調回路、同変調回路を有する位相同期回路及び同位相同期回路を有するインタフェース装置

【課題】ジッタが低減される変調回路、又はそれを用いた、小数点以下の分周数を有する位相同期回路、或いは同位相同期回路を用いたインタフェース装置を提供すること。

【解決手段】本発明の変調回路は、レベルに応じて分離された信号modiと信号modtを出力するレベルシフト部0901と、信号modiを入力し、入力されるクロックclockによって動作して信号modoを出力する変調器0903と、信号modoと信号modtとを入力して演算を行ない、振れ幅1の信号divoを出力する演算器0905とを備える。信号divoは、例えば、任意の整数M,Nに対して、整数値N,(N+1),・・・・・・,(N+2M),(N+2M+1)を表す信号として実現される。

(もっと読む)

位相比較器

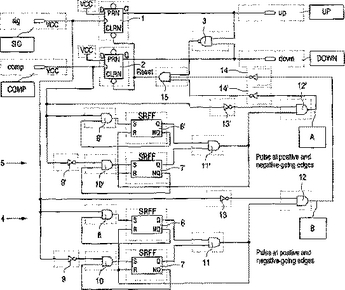

とりわけ、PLLモジュールに対する位相比較器は、入力信号の位相角をそれら入力信号のエッジを評価することで比較し、調節信号を生成する。この調節信号を入力信号についての崩壊或いは干渉に対して強くするために、これら入力信号(SIG、COMP)の更なる異なるエッジを評価し、これらから調節信号(UP、DOWN)に対する追加のリセット信号を生成するための追加の回路(4、5)が提供される。  (もっと読む)

(もっと読む)

位相差検出回路

【課題】 ノイズ耐性を向上できる位相差検出回路を提供すること。

【解決手段】 次エッジタイプ判定器31と先立ち上がり判定器32と立ち上がりエッジ専用位相差検出回路80と立ち下がりエッジ専用位相差検出回路90とを設け、前記次エッジタイプ判定器31と前記先立ち上がり判定器32から出力される検出信号をもとに、立ち上がりエッジ専用位相差検出回路80と立ち下がりエッジ専用位相差検出回路90からそれぞれ出力されるUP出力、DN出力をスイッチ回路61〜68、スイッチ回路71〜78により切り替える。

(もっと読む)

進歩した位相等化を用いたDLL位相検出

【解決手段】同期回路(例えば、遅延ロックドループ即ちDLL)の初期化中にクロックのシフトモードを開始及び終了するシステム及び方法が開示されている。初期化の際に、DLLは、ForceSL(Force Shift Left)モード及びOn1xモード(即ち、クロックサイクル毎にレフトシフト)に入る。フィードバッククロックは、(システムクロックから順次供給される)リファレンスクロックの位相をトラックし、コース位相検出ウインドウに与えられる前に、最初にコース位相検出器内で遅延される。フィードバッククロックの2つの遅延バージョンが、リファレンスクロックでサンプリングされて、一組の位相情報信号が生成される。それら信号は、その後、アドバンスド等位相(APHEQ)信号を確立するために使用される。APHEQ信号は、PHEQ(位相等化)位相のオンセットを進め、ForceSLモード及びOn1xモードの終了に使用される。これによって、クロックジッタによる不適切なForceSLの終了、又はOn1xが終了する間におけるフィードバックパスのオーバーシューティングが防止される。不適切なForceSLの終了及びOn1xのオーバーシューティングの問題が避けられることで、DLLのロッキングタイムはより速くなる。 (もっと読む)

差動位相検出器

【課題】本発明は、完全にデジタルで実装される差動位相検出器と、該差動位相検出器のための補間器に関する。

【解決手段】本発明によると、4つの光検出器のデジタル化された信号(A、B、C、D)からトラッキング誤差信号を生成する差動位相検出器は、デジタル化された信号(A、B、C、D)を時間多重するマルチプレクサと、時間多重されたデジタル化信号(A、B、C、D)からサンプルを同期化するためのデマルチプレクサ/補間器を含む。デマルチプレクサ/補間器は、好ましくは、4個の信号の時間多重信号を受信し、時間多重信号の半分の速度である4チャネルの信号を生成する。

(もっと読む)

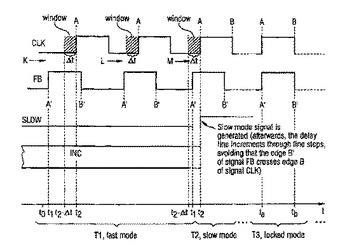

クロック信号を同期化する際に使用する装置、および、クロック信号同期化方法

本発明は、可変制御可能な遅延時間(tvar)を有する遅延手段(2)を備え、クロック信号(CLK)またはこのクロック信号(CLK)から得られる信号が、遅延手段(2)に入力され、可変制御可能な遅延時間(tvar)だけ遅延され、遅延されたクロック信号(DQS)の形状で出力される、クロック信号同期化方法、および、クロック信号(CLK)の同期化に使用する装置(1)に関するものである。本発明は、遅延手段(2)から出力される遅延されたクロック信号(DQS)またはこのクロック信号(DQS)から得られる信号(FB)の上記クロックエッジ(A’)が、上記クロック信号(CLK)またはこのクロック信号(CLK)から得られる信号の対応するクロックエッジ(A)の前の所定の時間窓の内側にあるかどうかを決定するためのデバイス(5)が設けられていることを特徴とする。  (もっと読む)

(もっと読む)

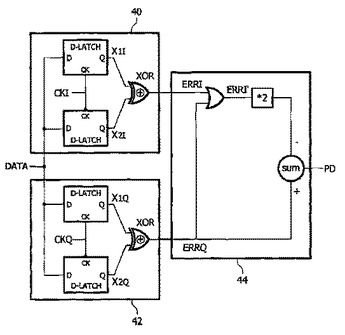

位相検出器

本発明は、データ信号DATAを用いてデータクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を検出する位相検出器に関する。データ信号DATAの遷移は、データクロックDATA-CLKの遷移と同期している。データクロックDATA-CLK及び参照クロックREF-CLKは同じ周波数を持つ。位相検出器は、第1のバイナリ信号ERRQを生成する第1の信号生成器を有する。そのパルス幅は、データ信号DATAの遷移とデータ信号DATAの遷移に隣接する第1の参照クロック信号CKQの遷移との間の第1の時間差ΔT1に等しい。第1の信号生成器は、第1の参照クロック信号CKQを受信する入力と、データ信号DATAを受信する入力とを有する。位相検出器は、第2のバイナリ信号ERRIを生成する第2の信号生成器を有する。第2のバイナリ信号ERRIのパルス幅は、データ信号DATAの遷移とそのデータ信号DATAの遷移に隣接する第2の参照クロック信号CKIの遷移との間の第2の時間差ΔT2に等しい。第2の信号生成器は、第2のバイナリ信号ERRIを受信する入力と、第2の参照信号CKIを受信する入力とを有する。位相検出器は、データクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を表す出力信号を生成する出力信号生成器を有する。出力信号は、ANDが論理AND演算を表すとき、ERRQ-2*(ERRQ AND ERRI)に等しいか、又はXORが論理XOR演算を表すとき、(ERRQ XOR ERRI)-ERRIに等しい。  (もっと読む)

(もっと読む)

121 - 138 / 138

[ Back to top ]