Fターム[5J039KK00]の内容

パルスの操作 (9,993) | 回路要素 (4,666)

Fターム[5J039KK00]の下位に属するFターム

非安定回路、発振回路 (298)

単安定回路 (7)

二安定回路 (568)

論理回路 (748)

遅延回路(遅延線を含む) (417)

積分回路 (81)

微分回路 (27)

定電流回路 (313)

差動増幅器 (237)

オペアンプ (72)

比較器 (415)

シュミット回路 (26)

波形整形回路 (39)

カウンタ (299)

シフトレジスタ (65)

分周回路 (200)

A/D,D/A変換回路 (157)

マルチプレクサ (134)

マトリックス回路 (4)

エンコーダ、デコーダ (47)

レートマルチプライヤ (2)

フィルタ(濾波器) (195)

レベルシフト回路 (45)

ピークホールド回路 (24)

リミッタ回路 (6)

クランプ回路 (29)

Fターム[5J039KK00]に分類される特許

201 - 211 / 211

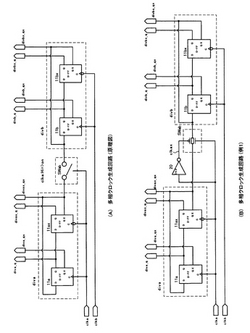

多相クロック生成回路

【課題】 基準クロックの高速性やフリップフロップの高速動作を必要とせずに、狭い位相差を有する多相クロックを生成することができる多相クロック生成回路を提供する。

【解決手段】 基準クロックを基に位相が異なる複数の出力クロックを生成する多相クロック生成回路において、位相が異なる第1及び第2の基準クロック(clka,clkb)をそれぞれ分周して出力クロックを生成する第1及び第2の分周回路(diva,divb)と、第1及び第2の分周回路の所定のノード(divbx_qx,divax_qx)間を間欠的に短絡するスイッチとを有し、当該スイッチは、定常動作状態で前記所定のノードが同じレベルに制御されるタイミングで、当該所定のノード間を短絡する。具体的には、スイッチは、第1、第2の基準クロックのいずれかまたは両方により短絡制御される。独立して動作する分周回路が、位相が異なる基準クロックを分周して、位相が異なる出力クロックを生成し、短絡スイッチにより両分周回路の動作を整合させて、分周回路が生成するそれぞれの分周クロックの位相ずれを整合させる。

(もっと読む)

等間隔パルス列生成装置および生成方法

【課題】 低消費電力を図り、かつ周波数の変動を生じない精度の良い出力波を得ることのできる位相合成装置および位相合成方法を提供する。

【解決手段】

クロックに同期した位相データと所定電圧値とのクロス点前後の位相データの差分をサンプルホールドした後アナログ値に変換するD/A変換器2と、D/A変換器により変換されたアナログ値を電流に変換する電流源3および該電流を時間的に積分するコンデンサ4からなる積分器5と、積分器の電荷を放電するリセット回路6とを備える直線補間回路を有する位相合成装置およびそれを用いた位相合成方法により、コンデンサのゲイン変化やD/A変換におけるDCオフセット誤差に影響されることなく、ジッタの小さい精度の良い出力波を合成することができる。

(もっと読む)

ピーク検出回路及び放電灯点灯装置

【課題】 高周波信号のピーク検出を精度良く行う。

【解決手段】 ピーク検出回路1において、演算増幅器2と、その出力信号を受けて動作する複数のトランジスタ3、4と、ホールド用のコンデンサ5を設ける。トランジスタ3、4をエミッタホロワ又はソースホロワとして用いるとともに、トランジスタ3の出力信号を演算増幅器2に入力して負帰還とし、トランジスタ3の出力信号をコンデンサ5に供給する。また、コンデンサ5に対して並列に放電用抵抗を設けて意図的にドループを与えることで、時々刻々と変化する入力信号のピーク変化を捉えることができる。

(もっと読む)

コンパレ一タ回路

【課題】 スイッチングトランジスタにおける入力容量の低減、ゼロクロス周波数特性の向上を図り、高周波数の矩形波をサンプリングするコンパレータ回路(高周波トランジスタ回路)等の特性を改善する。

【解決手段】 プッシュプル回路40を構成するスイッチングトランジスタQ6と、前段のスイッチング回路30を構成する位相反転用トランジスタQ4のみを化合物半導体トランジスタで構成する。他のトランジスタの動作速度に限界があっても、充放電電流の減少やゼロクロス周波数の改善により、従来にない高速かつ高精度な動作(高周波数の矩形波のサンプリング等)が可能となる。

(もっと読む)

信号検出回路

【課題】 高速信号に対応し、精度良く差動信号の検出が可能であり、回路のレイアウト面積を縮小し、消費電力を低減することができる。

【解決手段】 本発明による信号検出回路は、2つある差動比較回路の一方にオフセット調整回路抵抗Rb1を持たせ、一方の差動比較回路からの差動出力信号にオフセット電圧Voffを与え、2つの差動比較回路の逆相出力によって形成される差動出力信号を差動排他的論理和回路EOR3へ入力し、排他的論理和を出力して、オフセット調整回路抵抗Rb1で設定したレベル以上の差動入力信号を検出する。

(もっと読む)

チャージポンプ回路

【課題】チャージポンプ回路の効率を向上させるとともに、チャージポンプ回路の全体のパターン面積を小さくする。

【解決手段】第1及び第2の電荷転送用MOSトランジスタM1(N),M2(N)の両方をNチャネル型で構成する。第2の電荷転送用MOSトランジスタM2(N)をスイッチング動作させるために、もう一段のポンピングパケットを追加した。第2の電荷転送用MOSトランジスタM2(N)がオンするときのVGS(ゲートソース間電圧)を高くして、低いオン抵抗を得るために、当該ポンピングパケットを駆動する第2のクロックドライバーCD2の電源として、定常動作時において、出力電圧B(2VDD)を第2のダイオードD2を通して供給する。チャージポンプ回路の起動時には、第2のクロックドライバーCD2の電源として第1のダイオードD1を通して入力電圧VDDを供給する。

(もっと読む)

ジッタ印加回路、及び試験装置

【課題】広帯域、高分解能、大振幅の位相ジッタ成分を、クロック信号に容易に印加することができるジッタ印加回路を提供する。

【解決部】与えられるジッタデータに応じた位相ジッタ成分を含むクロック信号を生成するジッタ印加回路であって、与えられる基準信号に応じて発振信号を生成するPLL回路と、発振信号を遅延させたクロック信号を出力する可変遅延回路と、ジッタデータの低周波成分に基づいてPLL回路の発振周波数を制御し、発振信号に位相ジッタ成分の低周波成分を印加する低周波印加部と、ジッタデータの高周波成分に基づいて可変遅延回路における遅延量を制御し、クロック信号に位相ジッタ成分の高周波成分を印加する高周波印加部とを備えるジッタ印加回路を提供する。

(もっと読む)

スプレッドスペクトラムクロック生成器及びその変調方法

【課題】製造バラツキ、電源電圧、使用温度、使用周波数が変化しても所望の変調度の周波数変調クロックを供給可能とするスプレッドスペクトラムクロック生成回路を提供する。

【解決手段】制御信号に応じて制御周期間隔で発振周期を可変に制御する第1の遅延制御型発振回路104と、第1の遅延制御型発振回路の出力を分周したクロック信号fo1と、位相比較結果に基づき周波数制御信号Cを出力する制御回路103と、変調最大値Aを決定する変調最大値決定回路106と、変調最大値A内で変調制御信号αを生成する変調信号発生回路107と、出力クロック信号の発振周期を制御信号に応じ制御周期間隔に可変に制御する第2の遅延制御型発振回路108を備えている。

(もっと読む)

電圧比較器および電圧比較方法

【課題】不感領域を小さくできるとともに高い応答性と高精度な電圧比較を実現する。

【解決手段】第1の入力信号処理回路10で、第1の入力信号12の電圧をサンプリングして保持した後、これに応じた電位の第1の評価信号13を信号レベル判定回路30へ出力するとともに、第2の入力信号処理回路20により、第2の入力信号の電圧をサンプリングして保持した後、これに応じた電位の第2の評価信号23を信号レベル判定回路30へ出力し、これら第1の評価信号13および第2の評価信号23を信号レベル判定回路30で比較する。

(もっと読む)

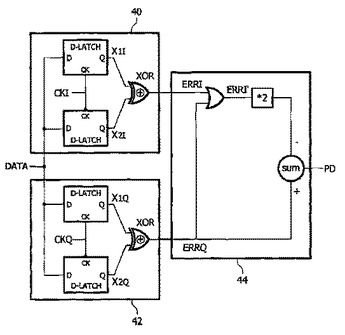

差動位相検出器

【課題】本発明は、完全にデジタルで実装される差動位相検出器と、該差動位相検出器のための補間器に関する。

【解決手段】本発明によると、4つの光検出器のデジタル化された信号(A、B、C、D)からトラッキング誤差信号を生成する差動位相検出器は、デジタル化された信号(A、B、C、D)を時間多重するマルチプレクサと、時間多重されたデジタル化信号(A、B、C、D)からサンプルを同期化するためのデマルチプレクサ/補間器を含む。デマルチプレクサ/補間器は、好ましくは、4個の信号の時間多重信号を受信し、時間多重信号の半分の速度である4チャネルの信号を生成する。

(もっと読む)

位相検出器

本発明は、データ信号DATAを用いてデータクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を検出する位相検出器に関する。データ信号DATAの遷移は、データクロックDATA-CLKの遷移と同期している。データクロックDATA-CLK及び参照クロックREF-CLKは同じ周波数を持つ。位相検出器は、第1のバイナリ信号ERRQを生成する第1の信号生成器を有する。そのパルス幅は、データ信号DATAの遷移とデータ信号DATAの遷移に隣接する第1の参照クロック信号CKQの遷移との間の第1の時間差ΔT1に等しい。第1の信号生成器は、第1の参照クロック信号CKQを受信する入力と、データ信号DATAを受信する入力とを有する。位相検出器は、第2のバイナリ信号ERRIを生成する第2の信号生成器を有する。第2のバイナリ信号ERRIのパルス幅は、データ信号DATAの遷移とそのデータ信号DATAの遷移に隣接する第2の参照クロック信号CKIの遷移との間の第2の時間差ΔT2に等しい。第2の信号生成器は、第2のバイナリ信号ERRIを受信する入力と、第2の参照信号CKIを受信する入力とを有する。位相検出器は、データクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を表す出力信号を生成する出力信号生成器を有する。出力信号は、ANDが論理AND演算を表すとき、ERRQ-2*(ERRQ AND ERRI)に等しいか、又はXORが論理XOR演算を表すとき、(ERRQ XOR ERRI)-ERRIに等しい。  (もっと読む)

(もっと読む)

201 - 211 / 211

[ Back to top ]