Fターム[5J039KK00]の内容

パルスの操作 (9,993) | 回路要素 (4,666)

Fターム[5J039KK00]の下位に属するFターム

非安定回路、発振回路 (298)

単安定回路 (7)

二安定回路 (568)

論理回路 (748)

遅延回路(遅延線を含む) (417)

積分回路 (81)

微分回路 (27)

定電流回路 (313)

差動増幅器 (237)

オペアンプ (72)

比較器 (415)

シュミット回路 (26)

波形整形回路 (39)

カウンタ (299)

シフトレジスタ (65)

分周回路 (200)

A/D,D/A変換回路 (157)

マルチプレクサ (134)

マトリックス回路 (4)

エンコーダ、デコーダ (47)

レートマルチプライヤ (2)

フィルタ(濾波器) (195)

レベルシフト回路 (45)

ピークホールド回路 (24)

リミッタ回路 (6)

クランプ回路 (29)

Fターム[5J039KK00]に分類される特許

41 - 60 / 211

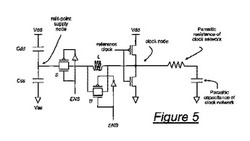

共振クロックネットワークを従来モードで作動させるためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。提示されたアーキテクチャにより、共振クロック分配ネットワークの従来モードでのエネルギ効率の良い作動が可能になり、クロック波形の目標仕様を満たすことができる。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、アットスピード試験及び達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

インダクタオーバーヘッドなしで共振クロック分配ネットワークの固有周波数を選択する方法

共振クロック分配ネットワークのためのインダクタアーキテクチャが提示される。このアーキテクチャにより、選択的にインダクタを切り離すことによって共振クロック分配ネットワークの固有周波数の調整が可能になり、複数のクロック周波数でエネルギ効率の良い作動が実現する。提示されたアーキテクチャは、主として統合されたインダクタを備える共振クロックネットワーク設計を対象としており、面積オーバヘッドが現れない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

共振クロック分配ネットワークの周波数スケール調整された作動のためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。このアーキテクチャにより、選択的にイネーブルされるフリップフロップの導入によって、複数のクロック周波数での共振クロック分配ネットワークのエネルギ効率の良い作動が可能になる。提示されたアーキテクチャは、主として一体化インダクタを有する共振クロックネットワーク設計を目的としており、インダクタのオーバヘッドが出現しない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

プログラム可能な駆動回路を備えた共振クロック分配ネットワークアーキテクチャ

プログラム可能なサイズのクロック駆動回路及びプログラム可能なデューティサイクルの基準クロックを使用して、共振又は非共振モードで複数のクロック周波数の中の任意の1つの周波数で作動する場合に小さなエネルギ消費で目標クロック立ち上がり時間及びクロック振幅を実現する共振クロック分配ネットワークアーキテクチャが開示さる。一般に、このネットワークは、複数のクロック周波数をもつ半導体デバイス、及び高性能で低電力クロックを必要とするマイクロプロセッサ、ASIC、及びSOC等に適用可能である。 (もっと読む)

モータ用位相同期回路及びそれを用いたスピンドルモータ

【課題】入力信号の周波数が変化するようなモータの駆動制御において、ステップ入力などのように入力信号の位相が急激に変化した場合でも、オーバーシュートやスリップによる振動などの過渡的な振動の発生を抑制することができる多重PLL回路の構成を得る。

【解決手段】第2PLL21の第2位相比較回路24によって検出される位相差が所定範囲外である場合には、ループ加算器26を介さずに、第1PLL11を用いて第2PLL21のモータ部22を制御する一方、上記位相差が所定範囲内である場合には、上記ループ加算器26を介して上記第1PLL11と上記第2PLL21とを接続して多重PLL回路を構成するように、信号経路切換部33によって、該第1及び第2PLL11,12の信号経路を切り換える。

(もっと読む)

画像形成装置、画像形成方法、及びプログラム

【課題】消費電力増加を抑制した画像形成装置、画像形成方法、及びプログラムを提供する。

【解決手段】上位装置からの印刷データを受信し、印刷する画像形成装置であって、コントローラが省エネ復帰信号を省エネ制御コントローラに出力した際は復帰要因送信ビットに“1”を立て、MAIN CPUが省エネ状態から復帰した後、復帰要因送信ビットが“1”ならば処理は行わず、復帰要因送信ビットが“0”ならば入力された全てのノイズの特性から最適なノイズキャンセル回路の設定値を計算し、設定変更するようにした。

(もっと読む)

電圧範囲判断回路

【課題】電圧範囲判断回路を提供すること。

【解決手段】電圧範囲判断回路は対象電圧生成部、選択電圧生成部、比較電圧選択部及び出力信号生成部を含む。対象電圧生成部は、入力電圧に基づいて対象電圧を生成する。選択電圧生成部は、基準電圧に基づいて第1〜第2選択電圧を生成する。比較電圧選択部は、出力信号に基づいて、第1〜第2選択電圧の中で1つを選択して比較電圧に出力する。出力信号生成部は、対象電圧と比較電圧を比べて出力信号を生成する。電圧範囲判断回路は外部ノイズが流入する場合も入力電圧の電圧範囲を正確に判断することができる。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

周波数の即時調整が可能な節電型トリガー制御装置、および、その方法

【課題】周波数の即時調整が可能な節電型トリガー制御装置及びその方法を提供する。

【解決手段】本発明に係る装置は、少なくとも2つの信号入力端を有する信号制御ユニットと、計数制御ユニットと、クロック生成器と、からなる。2つの信号入力端はそれぞれ、トリガー回数を受信し、その後対応する回数の周波数逓増トリガー信号又は周波数逓減トリガー信号を生成する。計数制御ユニットにより受信した周波数逓増トリガー信号及び周波数逓減トリガー信号を計数する。クロック生成器により計数した周波数逓増トリガー信号又は周波数逓減トリガー信号の回数に基づき、出力周波数を線形逓増又は逓減する。本発明の装置は更に、電源コントローラーを有し、出力電圧を調整する。本発明は、システムのいかなる状態下でも、外部の制御により即時にシステムの周波数/電圧を線形調整でき、節電目的が達成される。

(もっと読む)

同期信号発生回路

【課題】 PWM信号からその同期信号を発生する。

【解決手段】 三角波発生回路101は、PWM信号PWMINの立ち上がりエッジおよび立ち下がりエッジの各々を検出する度に、先行して開始した三角波信号の発生と並行して三角波信号を発生する手段であり、立ち上がりエッジまたは立ち下がりエッジの検出後、三角波信号を基準レベルから一定の時間勾配で変化させ、その後、同種のエッジが検出された以降、同じ大きさの逆方向の時間勾配で三角波信号を変化させる。同期信号発生部160は、三角波発生回路101が発生する三角波信号TRIA、TRIB、TRICに基づいてPWM信号PWMINに同期した同期信号SYNCを発生する手段であり、相前後して発生を開始した2個の三角波信号の大小関係が逆転したとき、同期信号SYNCのレベルを反転させ、先行して発生を開始した三角波信号を基準レベルに初期化する。

(もっと読む)

中波放送機の発振部

【課題】2台の水晶発振器を備え、一方の水晶発振器が出力する周波数信号を利用して発振する中波放送機の発振部において、2台の水晶発振器各々の発振器の出力周波数のズレを監視し、ズレが発見された場合に、アラーム信号を発生し、迅速な対応を即すことで、中波放送機の信頼性をより高める。

【解決手段】現用と予備の2台の水晶発振器の出力周波数を、常に比較若しくは監視し、周波数ズレが発生した場合に対応できるように発振制御を行う中波放送機の発振部とした。

(もっと読む)

遅延回路

【課題】矩形波を入力される遅延回路において、入力信号にノイズパルスが存在すると、出力信号のジッターが生じる。

【解決手段】シュミットコンパレータ102からの出力信号VdoでスイッチSW3を制御し、コンデンサCstへの充電電流を供給する電流源I1と、放電電流を供給する電流源I2とのいずれかを選択する。入力信号VdiでスイッチSW1,SW2を制御することで、選択された電流源からの電流供給がオン/オフされる。シュミットコンパレータ102はコンデンサCstの電圧Vstに応じてVdoを切り替える。Vdiの立ち上がり時には、VdiのHレベル期間にてコンデンサCstへ充電電流を供給し、Vdiの立ち下がり時には、VdiのLレベル期間にてコンデンサCstへ放電電流を供給する。

(もっと読む)

PLL回路

【課題】温度変動による位相雑音の悪化を低減することが可能なPLL回路を提供することを目的とする。

【解決手段】電圧制御発振回路81と、分周器82と、基準信号REF-INと発振信号Outputとの互いの位相を比較し、位相差に応じたパルス幅のパルス信号UP、DOWNを出力する位相比較器と、パルス信号UP、DOWNのパルス幅に応じた大きさのCP電流ICPp、ICPnを出力する出力電流補正機能付きチャージポンプ1と、CP電流ICPp、ICPnに応じてVt電圧を制御するループフィルタ85と、温度変動に応じて遅延時間が変化する遅延回路8とを備えてPLL回路100を構成し、遅延回路8の遅延時間に基づいて、CP電流ICPpとCP電流ICPnとの差が小さくなるように、CP電流ICPp又はCP電流ICPnを補正する。

(もっと読む)

信号処理装置

【課題】 温度によるクロックの変動を抑える。

【解決手段】 クロックを用いて信号を生成する信号処理部と、外部からの入力信号と前記信号処理部から出力された信号との位相差を検出し、前記位相差を示す信号を出力すると共に前記入力信号が無くなるとその直前の位相差の信号を出力する位相差検出部と、温度補償型の発振器からの出力信号に応じて前記位相差検出部からの出力に応じた値をカウントし、前記カウント値に基づいて基準信号を生成するデジタル発振器と、前記デジタル発振器からの基準信号と前記クロックを分周した信号との位相差に応じて前記クロックを生成するクロック生成部とを備える。

(もっと読む)

半導体集積回路

【課題】電源ノイズ耐性の優れ、かつ低消費電流でかつ多段接続が可能な増幅回路を実現する。

【解決手段】第1の電位変換用トランジスタ対(MN1,MN2)および第2のプリチャージトランジスタ対(MP3,MP4)を用いて電流/電圧変換用の容量素子(CL1,CL2)の対向電圧をそれぞれ第1の電源(VDD)レベルおよび第2の電源(VSS)レベルにプリチャージする。このプリチャージ完了後、第1の電源から差動トランジスタ対(MP1,MP2)を介して定電流を入力信号(VIP,VIN)に応じて振り分けて容量素子に供給する。この容量素子への電流供給停止後、第1のトランジスタ対(MN1,MN2)をオン状態、第2のトランジスタ対(MP3,MP4)をオフ状態に設定し、出力ノード(2a,2b)の電圧のレベルシフトをして、出力信号(VON,VOP)を生成する。

(もっと読む)

データ送受信方法

【課題】同期式連続データ伝送の信頼性を確保すると共に容易に設計することができるデータ送受信方法を提供する。

【解決手段】データ送信装置11は、通信開始時にテストデータをデータ受信装置12に送信する。データ受信装置12は、システムクロックを数倍に逓倍した内部クロックによりテストデータをサンプリングしてキャプチャ回路23に取り込み、データ取り込みタイミング制御部24において上記取り込みデータから最適のデータ取り込みタイミングを選択して設定する。データ受信装置12は、通常のデータを取り込む際は、データ取り込みタイミング制御部24において設定された最適のデータ取り込みタイミングにて受信データの取り込みを行う。

(もっと読む)

ラッチ機能付きコンパレータおよびそれを用いた試験装置

【課題】高速な応答性を有するラッチ機能付きのコンパレータを提供する。

【解決手段】比較増幅部20は、正側ラインLPの信号および負側ラインLNの信号のレベルを比較し、比較結果をラッチする。第1インバータ22は、その入力端子が正側ラインLPと接続され、その出力端子が負側ラインLNと接続される。第2インバータ24は、その入力端子が負側ラインLNと接続され、その出力端子が正側ラインLPと接続される。

活性化スイッチ26は、共通接続されたインバータ22、24の他方の電源端子に、電源電圧Vddを出力して比較増幅部20を不活性化する状態と、接地電圧VGNDを出力して比較増幅部20を活性化する状態と、を選択的に切りかえる。コンパレータTCは、比較増幅部20が活性化された後のタイミングにおける正側ラインLPの信号OPと負側ラインLNの信号ONの少なくとも一方に応じた信号を出力する。

(もっと読む)

クロック生成回路

【課題】高速動作するクロック・データリカバリのための正確なクロック信号を生成するクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1入力電圧に応じて第1周波数信号を出力する第1電圧制御発振回路と、第2入力電圧に応じて第2周波数信号を出力する第2電圧制御発振回路と、制御信号を受け取り、第1周波数信号と第2周波数信号との位相差が制御信号に応じた値になるように第1入力電圧と第2入力電圧とを制御する位相調整回路と、第1周波数信号に同期して受信信号を検出して出力する第1判定回路と、第2周波数信号に同期して受信信号を検出して出力する第2判定回路と、第1判定回路の出力と第2判定回路の出力とに基づいて受信信号の位相を検出し、その位相検出の結果に応じて第1入力電圧と第2入力電圧とを制御する位相検出器とを含む。

(もっと読む)

パルス発生装置

【課題】良好な信号レベルのパルス信号を効率よく発生するのに好適なパルス発生装置を

提供する。

【解決手段】パルス発生装置100を、CLK信号の入力に応じて起動開始信号D0と、

D0を反転したXD0とを出力する起動開始信号生成回路20と、起動開始信号の入力に

応じてパルス信号を発生する、各々の信号出力部が独立した第1〜第Nのパルス発生回路

21_1〜21_Nと、第1〜第Nのパルス発生回路21_1〜21_Nのうちパルス信

号を出力する予定の一部の回路の信号出力部を順次選択して、該選択した信号出力部を共

通の信号出力線に接続し、残りのパルス発生回路の信号出力部を共通の信号出力線から電

気的に切断する選択回路22とを含む構成とした。

(もっと読む)

周波数シンセサイザ

【課題】不要波成分の出力を抑圧することができる周波数シンセサイザを得ることを目的とする。

【解決手段】不要波抑圧回路10が、クロック信号源1により生成されたクロック信号に同期して、デジタル振幅データ生成回路2により生成された振幅信号A2に応じた波形のアナログ信号B2を生成して、そのアナログ信号B2をクロック周波数fckで90度の位相量だけシフトし、位相シフト後のアナログ信号B2とMN−DAC3から出力されたアナログ信号B1を合成する。

(もっと読む)

41 - 60 / 211

[ Back to top ]