Fターム[5J039KK00]の内容

パルスの操作 (9,993) | 回路要素 (4,666)

Fターム[5J039KK00]の下位に属するFターム

非安定回路、発振回路 (298)

単安定回路 (7)

二安定回路 (568)

論理回路 (748)

遅延回路(遅延線を含む) (417)

積分回路 (81)

微分回路 (27)

定電流回路 (313)

差動増幅器 (237)

オペアンプ (72)

比較器 (415)

シュミット回路 (26)

波形整形回路 (39)

カウンタ (299)

シフトレジスタ (65)

分周回路 (200)

A/D,D/A変換回路 (157)

マルチプレクサ (134)

マトリックス回路 (4)

エンコーダ、デコーダ (47)

レートマルチプライヤ (2)

フィルタ(濾波器) (195)

レベルシフト回路 (45)

ピークホールド回路 (24)

リミッタ回路 (6)

クランプ回路 (29)

Fターム[5J039KK00]に分類される特許

61 - 80 / 211

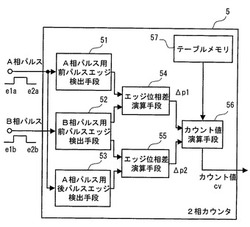

2相カウンタおよびカウンタシステム

【課題】カウント動作を高速でも容易に行えるようにすること。

【解決手段】A相パルスの前パルスエッジとB相パルスの前パルスエッジとのエッジ位相差と、A相パルスの後パルスエッジとB相パルスの前パルスエッジとのエッジ位相差とを検出し、上記両エッジ位相差の比率を演算し、上記エッジ位相差比率に対応して割り当てられたカウント値を演算する2相カウンタ。

(もっと読む)

クロック信号供給回路の設計方法、情報処理装置およびプログラム

【課題】半導体集積回路におけるクロック信号の供給において、回路全体を通しクロックラインを短縮し得る構成を提供することを目的とする。

【解決手段】回路素子のグループ間で回路素子の交換、移動を実行し、当該実行の前後でグループごとに回路素子の位置と中心位置との距離の合計し更に全グループについて合計した値が減少する場合には当該実行後のグループを維持し減少しない場合には当該実行前のグループを維持する最適化を実行する構成である。

(もっと読む)

FM信号のノイズキャンセラ回路

【課題】FM信号に含まれるノイズを適切に低減する。

【解決手段】処理対象となるFM信号の復調前の信号の振幅と閾値とを比較してFM信号の欠落を検出する検出回路102と、FM信号の復調後の信号に基づいて閾値を設定する閾値設定回路104と、を備えるFM信号のノイズ検出回路とする。

(もっと読む)

FM信号のノイズキャンセラ回路

【課題】FM信号に含まれるノイズを適切に低減する。

【解決手段】処理対象となるFM信号の復調前の信号の振幅と閾値とを比較してFM信号の欠落を検出し、検出信号を欠落が発生している期間出力する検出回路102と、検出信号を受けた時点におけるFM信号の復調後の信号を保持するホールド回路40と、検出信号が出力されていない間はFM信号の復調後の信号を選択して出力し、検出信号が出力されている間はホールド回路40の出力を選択して出力するセレクタ回路42と、を備えるノイズキャンセラ部106を含む。

(もっと読む)

ゼロクロス検出装置及び画像形成装置

【課題】 低消費電力で駆動して交流電圧のゼロクロス点を検出することが可能なゼロクロス検出装置及び該ゼロクロス検出装置を有する画像形成装置を提供する。

【解決手段】

交流電圧のゼロクロス点を検出するゼロクロス検出装置において、交流電圧を整流して全波整流電圧を出力する全波整流手段と、全波整流電圧の印加で所定の充電電圧に充電され、全波整流電圧が充電電圧以下になると、充電電流を出力する充電手段と、充電電流の入力でゼロクロス検出信号を出力する信号出力手段とを含む。

(もっと読む)

位相比較回路

【課題】D−FFの内部遅延が無視できない高速動作時において位相比較回路の低消費電力化を実現する。

【解決手段】マスタースレーブマスター型D−FF11は、第1のM−FF11−1,S−FF11−2および第2のM−FF11−3が縦続接続され、入力NRZデータ信号をクロック信号に応答して識別し、S−FFおよび第2のM−FFから出力する。遅延回路4は、入力NRZデータ信号をS−FFと同じ時間だけ遅延させる。第1のEXOR回路7は遅延回路の出力とS−FFの出力の排他的論理和演算を行ない、第2のEXOR8はS−FFの出力と第2のM−FFの出力の排他的論理和演算を行なう。加算器9は第1のEXOR回路の出力と第2のEXORの反転出力を加算する。

(もっと読む)

位相同期回路及びその制御方法、通信装置

【課題】

安定した周波数の出力信号を出力できるようにした位相同期回路及びその制御方法、通信装置を提供する。

【解決手段】

位相同期回路は、入力される制御電圧に応じた周波数の信号を出力信号として出力する電圧制御発振回路と、入力信号と電圧制御発振回路の出力信号との位相を比較する比較手段と、位相の比較に基づく電圧を異なるタイミングでそれぞれ保持する2つ以上のサンプル/ホールド回路と、2つ以上のサンプル/ホールド回路のいずれかを選択し、該選択したサンプル/ホールド回路からの出力を制御電圧として電圧制御発振回路に入力する切換手段と、入力信号の異常を検出する異常検出手段とを具備し、切換手段は、異常検出手段による異常の検出結果に基づいて2つ以上のサンプル/ホールド回路のいずれかの出力を選択する。

(もっと読む)

比較演算増幅回路、AD変換回路、電子機器

【課題】比較演算増幅回路やAD変換回路において、回路規模や消費電力のさらなる低減を図る。

【解決手段】サンプルホールド回路503では、複数のサンプルホールド回路と信号選択回路により、AD変換対象の差動アナログ信号対について、ホールドモード時の出力信号対を時分割で出力するようにする。フォールディング方式を採らないAD変換においては、比較演算増幅回路501は、時分割で供給される複数の出力信号対について、信号選択回路により複数の差動基準信号対を時分割で扱うように切り替えながら、各出力信号対と各差動基準信号対の差を各差動増幅回路で増幅することで複数の増幅出力信号対を時分割で出力するようにする。デジタルデータ取得部6は、時分割で供給される複数の増幅出力信号対の差をそれぞれ2値化することでデジタルデータを取得する。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】親機、複数台の中継機、複数台の子機を備えた大規模なシステムで符号長が比較的長い同期信号を用いても、安定したPLLの引き込みを実現可能とする。

【解決手段】このPLL制御装置では、TIM抽出回路101は入力信号からタイミング成分を抽出し、VCXOは供給される制御信号に基づき基準信号の位相及び/又は発振周波数を制御する。0次PLL回路102はタイミング成分の位相差に基づき基準信号の発振周波数範囲を設定するための制御信号を出力し、1次PLL回路103はタイミング成分の位相差に基づき基準信号の位相を制御するための制御信号を出力する。制御セレクタ105は、0次PLL回路102又は1次PLL回路103からの制御信号を順次切り替えてVCXOに供給する。

(もっと読む)

DDS回路及び電子装置

【課題】 チューニングワードのビット長を増加させずに、分解能を向上させ得るDDS回路及び電子装置を提供することを目的とする。

【解決手段】 リファレンスクロックの周波数に基づいて、チューニングワードから正弦波の信号を出力するDDS部11と、リファレンスクロックの周波数を分周する分周器12aと、DDS部11で出力された正弦波の信号の周波数を分周する分周器12bと、分周器12aで分周された周波数と分周器12bで分周された周波数とを合成した合成周波数を備える正弦波の信号を出力するミキサ12cと、を有することを特徴としている。

(もっと読む)

電子回路、電子回路を備えた電子装置及び電子装置のパルス検出方法

【課題】回路が簡単で安定性が高い二乗検出回路。

【解決手段】入力端子101と、入力端子101から入力された信号から平衡信号と不平衡信号とを出力する平衡−不平衡変換器102と、ゲート端子に平衡信号が接続され、ソース端子が接地された第1の電界効果型トランジスタ103と、ゲート端子に不平衡信号が接続され、ソース端子が接地された第2の電界効果型トランジスタ104と、第1の電界効果型トランジスタ103のドレイン端子と第2の電界効果型トランジスタ104のドレイン端子とを相互に接続しドレイン電流を出力する出力端子112と、を含む電流出力部120と、電流出力部120の出力線113と接続され、電流出力部120から出力されるドレイン電流を加算した加算電流を出力する電流加算部121と、を含む電子回路1。

(もっと読む)

半導体集積回路

【課題】動作モードによって周波数変調を行うか行わないかを選択することによって受信側の負荷を低減することができる半導体集積回路を提供すること。

【解決手段】半導体集積回路1は、2以上の内部回路(ビデオデコーダ11、CPU12など)と、所定の周波数のクロックを発生するPLL31と、周波数を変調させたクロックを発生するSSCG PLL32と、内部回路にPLL31からのクロックか、SSCG PLL32からのクロックのいずれかを選択して内部回路に入力するセレクタ21とを有する。

(もっと読む)

ジッタ印加回路、パターン発生器、試験装置、および、電子デバイス

【課題】高周波数かつ大振幅のジッタを生成する。

【解決手段】ジッタを有するジッタ重畳信号を生成するジッタ印加回路であって、与えられる基準信号を、それぞれ予め設定される遅延量で順次遅延させる、縦続接続された複数の遅延回路と、それぞれの遅延回路が出力する信号のタイミングに応じて、ジッタ重畳信号のそれぞれのエッジを生成する信号生成部と、ジッタ重畳信号の各周期に印加すべきジッタに応じた遅延量をそれぞれ設定する遅延設定部とを備え、少なくとも一つの遅延回路の遅延量が、ジッタ重畳信号の平均周期の整数倍とは異なる値に設定されるジッタ印加回路を提供する。

(もっと読む)

信号変調回路

【課題】発振回路からの連続信号のレベル調整を行う場合であっても、送信電力を制御することが可能な信号変調回路を提供する。

【解決手段】信号変調回路の一例であるパルス生成回路は、発振回路と、制御信号発生回路と、逓倍回路と、フィルタと、制御部からなる。発振回路、及び逓倍回路は能動素子で構成されるアクティブ回路である。発振回路から連続信号が出力されて逓倍回路に入力され、制御信号発生回路から出力される制御信号によって逓倍回路が間欠的に動作することでパルス信号を生成し、制御部からの信号により電力レベルを簡易に調整する。

(もっと読む)

車載情報伝達装置

【課題】インバータの温度を感知する感温ダイオードSDの温度に関する情報をマイコン20に伝達する際に、マイコン20のタイマ機能やA/D変換機能を備えたポートを使用すると、そのリソースが低減すること。

【解決手段】感温ダイオードSDの出力電圧に基づき周波数変調回路34にて周波数変調された信号は、フォトカプラ36に取り込まれる。フォトカプラ36の出力は、マイコン20に取り込まれる。マイコン20においては、フォトカプラ36の出力電圧が閾値電圧以上であるなら論理「H」と認識し、閾値電圧未満であるなら論理「L」と認識する処理を、ハードウェアにて行う。一方、論理「H」である期間や論理「L」である期間に基づく温度情報の復調処理を、ソフトウェア処理とする。

(もっと読む)

イコライザのテスト回路および集積回路の評価システム

【課題】量産テストでの使用に適したイコライザのテスト回路および集積回路の評価システムを提供する。

【解決手段】テスト回路1は、擬似乱数データ生成部11が、擬似乱数データを生成し、重み付け係数生成部12が、符号間干渉の干渉強度設定用の重み付け係数を生成し、擬似符号間干渉データ生成部13が、擬似乱数データのビット系列に応じて擬似乱数データに擬似的な符号間干渉を発生させ、重み付け係数により振幅を変化させた擬似符号間干渉データを生成し、ドライバ14が、生成された擬似符号間干渉データを差動信号として出力する。比較部15は、イコライザ100の出力をサンプリング回路200によりサンプリングしたデータを、符号間干渉発生前の元の擬似乱数データと比較し、カウント部16が、比較部15により検出された不一致の数をカウントする。

(もっと読む)

コンパレータ回路

【課題】定電流型ヒステリシスコンパレータと電圧型ヒステリシスコンパレータの2つの機能を有し、回路規模を削減できるコンパレータ回路を提供する。

【解決手段】定電流の供給可能な定電流源12と、入力端子IN1及びIN2から与えられる信号を比較するコンパレータ11と、一端が接地された抵抗R1と、一端が抵抗R1の他端、定電流源12及び入力端子IN2に接続された抵抗R2と、抵抗R2の他端に電源電圧VDDを印加可能なスイッチS1と、一端が定電流源12に接続され、他端が出力ドライバ13に接続された抵抗R3と、コンパレータ11の出力に基づいて抵抗R3の前記他端を接地するか否か切り替えるスイッチS2と、スイッチS1及び定電流源12のオン・オフ制御を行い、定電流源12をオンさせる時はスイッチS1をオフし、スイッチS1をオンする時は定電流源12をオフする制御部10と、を備える。

(もっと読む)

ポートからポートへの遅延を実装することにより雑音を減らす方法

【課題】

ポートからポートへの遅延を実装することにより雑音を減らす。

【解決手段】

雑音を減らす方法は、次を含む:電源供給網をオンにする時に、高速データリンクの最大の雑音の周波数を特定すること;その最大の雑音を最小化する、第1のポートと第2のポートの間の遅延時間を特定すること;及び、第1のポートをオンにした時から、その遅延時間後に、第2のポートをオンにすること。他の実施例も開示し請求する。

(もっと読む)

位相差平滑化装置

【課題】多相クロック生成及び伝送の過程において発生した多相クロックの位相誤差を低減する。

【解決手段】入力多相クロックのうち所望の位相関係にある複数のクロックを入力して各クロックの位相に所望の重み付けをする重み付け手段と、重み付けされたクロックを加算する加算手段と、を有する位相フィルタ回路を前記多相クロックの位相数と同数備え、位相フィルタ回路から出力されたクロックを出力多相クロックとして出力する。

(もっと読む)

クロック生成回路およびその使用方法

【課題】基準信号の周波数を逓倍又は分周したクロック信号を生成するクロック生成回路において、一つの基準信号から任意周波数のクロック信号を発生可能とする。

【解決手段】クロック生成回路1は、リング状に連結したm個の遅延素子DUからなるパルス遅延回路10と、各遅延素子DUから順次出力される通過信号P1〜Pmに基づき、基準信号CKIの周期を遅延素子DUでの遅延時間を単位として表した周期データDTを生成する周期測定部20と、除数又は乗数として使用される設定値MNを格納する設定値レジスタ50と、周期データDTに、設定値MNを乗・除してクロック信号の出力周期を表す制御データCDを生成する制御部30と、制御データCDと通過信号P1〜Pmとに基づき、基準信号CKIを分周又は逓倍したクロック信号CKOを出力する出力部40とを備え、実数で表された設定値MNを用いる。

(もっと読む)

61 - 80 / 211

[ Back to top ]