Fターム[5J039KK00]の内容

パルスの操作 (9,993) | 回路要素 (4,666)

Fターム[5J039KK00]の下位に属するFターム

非安定回路、発振回路 (298)

単安定回路 (7)

二安定回路 (568)

論理回路 (748)

遅延回路(遅延線を含む) (417)

積分回路 (81)

微分回路 (27)

定電流回路 (313)

差動増幅器 (237)

オペアンプ (72)

比較器 (415)

シュミット回路 (26)

波形整形回路 (39)

カウンタ (299)

シフトレジスタ (65)

分周回路 (200)

A/D,D/A変換回路 (157)

マルチプレクサ (134)

マトリックス回路 (4)

エンコーダ、デコーダ (47)

レートマルチプライヤ (2)

フィルタ(濾波器) (195)

レベルシフト回路 (45)

ピークホールド回路 (24)

リミッタ回路 (6)

クランプ回路 (29)

Fターム[5J039KK00]に分類される特許

121 - 140 / 211

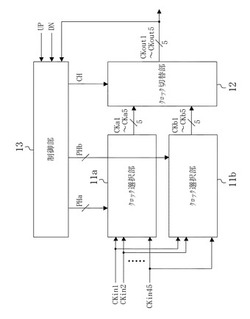

クロック選択回路及びそれを備えたクロックデータリカバリ回路

【課題】クロック選択回路の出力切り替えに起因するグリッチを排除する。

【解決手段】クロック選択回路は、互いに位相のずれた複数のクロック信号を受け、これらクロック信号の中から一つ以上を選択的に出力する2個のクロック選択部(11a、11b)、これらクロック選択部(11a、11b)のいずれか一方を選択し、当該選択した方から出力されたクロック信号を出力するクロック切替部(12)、及びこれらクロック選択部(11a、11b)及びクロック切替部(12)を制御する制御部(13)を備えている。制御部(13)は、2個のクロック選択部(11a、11b)のうちクロック切替部(12)によって選択されていない方に対してクロック信号の再選択を指示し、当該指示後に、クロック切替部(12)に対して出力の切り替えを指示する。

(もっと読む)

信号処理回路

【課題】たとえば非接触形ICカードの読取信号などのように、クロック信号に2値信号が重畳しており、しかもノイズが混入するような入力信号を適切に処理するための信号処理回路構成を簡単化する。

【解決手段】逆並列接続のダイオードD1 、D2 を介して入力信号S1 を非反転入力端子に入力させる比較器11と、非反転入力端子に接続する片端接地のコンデンサCとを設け、比較器11の反転入力端子には、入力信号S1 を分岐入力させる。

(もっと読む)

半導体装置

【課題】 半導体装置における通常モードと特殊モードとの混載をコストの増大および特殊モードへの誤移行の危険性を回避して実現する。

【解決手段】 短パルス除去回路(11)は、外部制御信号(/CE)について第1所定時間より短いパルス幅の活性パルスおよび非活性パルスを除去して内部制御信号(/CEI)として出力する。短パルス検出回路(12)は、外部制御信号について第1所定時間より短いパルス幅の活性パルスおよび非活性パルスを検出する。内部回路(13)は、通常モードおよび特殊モードを有し、外部制御信号に代えて内部制御信号に応じて動作する。内部回路は、短パルス検出回路による活性パルスの検出に応答して通常モードから特殊モードに移行し、短パルス検出回路による非活性パルスの検出に応答して特殊モードから通常モードに移行する。

(もっと読む)

位相比較信号処理回路

【課題】PLLのデジタル位相比較器の出力矩形波信号を処理し、PLLの引き込み可能な周波数幅を拡げ、同期時間を短縮する位相比較信号処理回路を提供する。

【解決手段】矩形波信号を両極性信号に変換する電圧シフタ7と出力端子22間に並列接続され、整流回路8と積分保持回路9と微分回路10とゲート回路12と電圧ホールド回路13と共通の加算回路14とからなる第1信号路、及び、整流回路15と積分保持回路16と微分回路17とゲート回路19と電圧ホールド回路20と前記加算回路14とからなる第2信号路、第1信号路及び第2信号路の積分保持回路9、16とゲート回路12、19を個別制御する制御信号発生器21を備え、第1及び第2信号路で、両極性信号の整流、整流電圧の積分保持、積分保持値の微分、微分出力の保持、保持電圧の加算を行うことにより処理信号を出力する。

(もっと読む)

クロック分配回路、半導体集積回路、クロック分配回路の形成方法及びそのプログラム

【課題】異なるクロックツリー間の回路間をつなぐデータ転送パスが存在しても、OCVに影響されずにクロックを分配する。

【解決手段】クロック分配回路は、クロック分配網20aの分岐点NA3経由の第1クロック信号で動作する順序回路25aと、クロック分配網20bの分岐点NB3経由の第2クロック信号で動作する順序回路26aと、順序回路25aと順序回路26aとの間のデータ転送パス40とを有する半導体集積回路45へ第1クロック信号及び第2クロック信号を分配する。クロック分配回路20は、分岐点NA3からの第1フィードバック信号と第1リファレンス信号とから第1クロック信号を出力するPLL回路21と、分岐点NB3からの第2フィードバック信号と第2リファレンス信号とから第2クロック信号を出力するPLL回路22とを具備する。

(もっと読む)

シリアル通信用ボーレートジェネレータ

【課題】シリアル通信システムにおいて、ボーレートを補正するノード内のCPUの負担を軽減するシリアル通信回路を提供する。

【解決手段】本発明によるボーレートジェネレータ12は、入力されるシンクフィールド42のビット数を入力順に計数するエッジカウンタ22と、エッジカウンタ22が所定のビット数を計数するまでの時間33を測定するシンクフィールド測定タイマ23と、測定時間33を用いて、シンクフィールド42における1/2ビット期間であるボーレート補正値34を生成するボーレート補正回路24とを具備し、ボーレート補正値34に基づき、シリアル通信のボーレートを決定する。

(もっと読む)

時間計測回路

【課題】短い時間幅の高分解能な計測と長い時間幅の低分解能な計測とを、回路規模を大幅に増大させることなく、いずれも実現させることが可能な時間計測回路を提供する。

【解決手段】駆動電圧VDDLに応じた遅延時間で信号を遅延させる遅延ユニットDUをM(Mは正整数)段直列接続してなり、起動用パルスPAの入力により起動され、各遅延ユニットDUにてパルス信号を順次遅延させながら伝送するパルス遅延回路10と、計測用パルスPBが入力されると、パルス遅延回路10内でのパルス信号の位置を検出(ラッチ)し、その検出結果を、起動用パルスPAの入力から計測用パルスPBの入力までの時間Tm内にパルス信号が通過した遅延ユニットDUの段数を表す所定ビットのデジタルデータDTに変換して出力するラッチ&エンコーダ12と、電圧設定データDVに従った大きさの駆動電圧VDDLを発生させる駆動電圧設定回路14とを備える。

(もっと読む)

PLL回路および記録情報再生装置

【課題】PD出力から微分値を求めると、平均値が“0”の周期関数の微分の平均値はやはり“0”となり、上下バランスが崩れた位相誤差検出特性が得られない。

【解決手段】加算器4203の加算結果ADDである位相誤差絶対値を絶対値比較器4205でしきい値Vthと比較し、当該位相誤差絶対値がしきい値Vthを超えた時点でのPHERR信号の極性と、現時点でのPHERR信号の極性とを不一致検出回路4208で比較する。そして、不一致のときにビットスリップが起きたと判断し、現時点でのPHERR信号の極性を極性反転回路4210で反転し、最終的なPD出力とすることで、上下バランスが崩れた位相誤差検出特性を実現する。

(もっと読む)

通信システム及び通信装置並びにPWM制御のデューティ決定方法

【課題】通信周波数を微小変動させる技術よりも、ノイズレベルの低減を更に図ることができる通信システムを提供する。

【解決手段】マスタ11は、通信中において通信周波数を微小変動させると共に、バス3のドライブレベルを許容範囲内で変化させる。また、マスタ11は、バス3をドライブする場合の電流駆動能力を変化させてレベル遷移に要する時間も変化させるので、信号レベルが変化する場合の波形の傾きもダイナミックに変化させて信号の周波数帯域をより拡げるようにして、発生するノイズのピークレベルを一層抑制する。

(もっと読む)

位相比較器

【課題】フルレートとハーフレートの両方に対応した位相比較器を得る。

【解決手段】データ信号の立ち下がりタイミングでクロック信号の振幅値を検出する第一の検出手段1と、データ信号の立ち上がりタイミングでクロック信号の振幅値を検出する第二の検出手段2と、第一の検出手段1がクロック信号の立ち上がり状態又は立ち下がり状態の振幅値を検出しているのかを識別して第一の識別結果を出力し、第二の検出手段2がクロック信号の立ち上がり状態又は立ち下がり状態の振幅値を検出しているのかを識別して第二の識別結果を出力するエッジ比較手段3と、第一の識別結果に応じて第一の検出手段1の出力の極性を反転する第一の極性反転手段4と、第二の識別結果に応じて第二の検出手段2の出力の極性を反転する第二の極性反転手段5と、データ信号の極性に応じて第一又は第二の極性反転手段4、5の出力値を選択して出力する信号選択手段6とを設けた。

(もっと読む)

比較回路

【課題】スイッチトキャパシタを利用し回路規模の小さな比較回路を得る。

【解決手段】入力INAは、スイッチSW1によりコンデンサCaを介し、コンパレータCom1,Com2の正入力端に供給される。入力INBはスイッチSW2によりコンデンサCb1を介しコンパレータCom1の負入力端に供給されると共に、スイッチ3,4によりコンデンサCb2を利用して反転されて、コンパレータCom2の負入力端に供給される。コンパレータCom1、Com2の出力は排他的論理和回路EXORに入力され、ここから入力INAが±入力INBの範囲内か否かの判定結果が出力される。

(もっと読む)

レシーバ回路及びレシーバ回路試験方法

【課題】 レシーバ回路の速度試験をドライバ回路の接続無しに行えるようにすること。

【解決手段】 遅延部3は遅延制御信号に応答してクロック入力信号の位相を遅延制御して出力する。セレクタ2は、実速度試験時、遅延部3からのクロック入力信号と外部端子からの入力信号の中から前記クロック入力信号を選択して出力する。シリアルパラレル変換器4は、サンプリングクロック信号に基づいてセレクタ2から出力された信号をサンプリングし、シリアル信号をパラレル信号形式に変換して出力する。クロックデータリカバリ回路5は、変換器4の出力信号7に応じた最適な位相のサンプリングクロック信号を生成して変換器4に供給する。前記サンプリングクロックの位相を制御するための制御コード60をモニタすることで、遅延変化量とコード変化量の相関をとり、実測度試験を行う。

(もっと読む)

スプレッドスペクトラムクロッキングに使われる遅延された高周波クロック信号を発生させる方法、回路、及びシステム

【課題】スプレッドスペクトラムクロッキングに使われる遅延された高周波クロック信号を発生させるための方法、回路、及びシステムを提供する。

【解決手段】スプレッドスペクトラムクロック信号を発生させる方法は、同期システムのためのスプレッドスペクトラムクロック信号を提供するために選択される複数の遅延された高周波クロック信号を提供するために高周波クロック信号を遅延させる段階を含む。

(もっと読む)

波形改善回路

【課題】コンデンサに充電された電荷の放電タイミングを最適にし、高速信号に対応できるようにした波形改善回路を提供する。

【解決手段】信号線4に伝送されるデジタルの信号Stの波形を改善する波形改善回路1は、信号Stのレベルが所定値を超えたことをレベル検出回路11Aが検出すると、その出力電圧Vdに基づいてスイッチ回路12Aが導通状態になり、電源電圧VBを充電回路13Aのコンデンサ131に印加してコンデンサ131を充電する。信号Stの電圧レベルが、コンデンサ131の充電電圧Vcよりも低くなったタイミングでコンデンサ131から信号線4へ、放電回路14Aのダイオード141を介して放電が行われ、アンダーシュートが改善される。

(もっと読む)

ディジタル位相同期装置

【課題】入力された正弦波と周波数が等しく、かつ位相が同期した正弦波を、簡易で正確に、出力する装置を提供する。

【解決手段】位相差検出回路1は、外部から入力された第一の正弦波と正弦波生成回路5より出力する第二の正弦波との位相差を、ディジタル信号処理により算出する。その算出値に基づいて第二の正弦波の位相と周波数を調整するので、正弦波生成回路5は入力された第一の正弦波に周波数が等しく、かつ位相が同期した第二の正弦波を簡易に正確に出力することができる。

(もっと読む)

パルス位相差符号化回路

【課題】入力される電圧信号のレベルが回路の動作電源電圧より上昇した場合でも、正確な符号化動作を行うことができるパルス位相差符号化回路を提供する。

【解決手段】A/D変換回路11を構成するパルス位相差符号化回路13において、カウンタ2のカウント値をデータラッチ回路4にラッチさせるタイミング信号を生成するため、符号化周期信号PBに所定の遅延時間T12を付与する遅延回路12を、電圧入力端子に与えられる電圧信号Vinのレベルが上昇するのに応じて遅延時間が短縮されるように構成する。具体的には、遅延回路12を、リングディレイライン1を構成するNOTゲートと同じNOTゲートを、リングディレイライン1を構成する直列段数の1/2となる段数で直列接続して構成し、それらのNOTゲートを、A/D変換対象となる入力電圧Vinを電源として動作させる。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路に好適な積分回路及び高性能化を図ったカメラ用前処理LSIを提供する。

【解決手段】第1タイミング期間にオン状態にされる第1スイッチ及び第2スイッチにより第1キャパシタの第1端子と第2端子に入力電圧を供給する。上記第1タイミング期間と異なる第2タイミング期間にオン状態にされる第3スイッチ及び第4スイッチにより上記第1キャパシタの第1端子と第2端子を利得1のバッファアンプの入力端子と出力端子に接続する。上記バッファアンプの入力端子と固定電位との間に第2キャパシタを設ける。上記バッファアンプの入力端子又は出力端子の電圧を積分出力とする。固体撮像素子で形成された画素信号のフィードスルー部との差を表す信号部を相関二重サンプリング回路で取り出し、黒レベルクランプ信号を前記の積分回路により取り出して電圧保持回路で保持させる。

(もっと読む)

波形整形回路

【課題】波形整形用コンパレータのしきい値を変更する。

【解決手段】入力端10からの入力信号は、コンデンサ12を介し、コンパレータ14に供給され、ここでしきい値と比較され波形整形される。このコンパレータ14には、しきい値として、アナログスイッチ64または66の出力が供給され、平滑端子32に平滑容量34が接続されている場合には、この平滑端子32に得られる入力信号の中点電位が供給され、平滑端子32がグランド電位になっているときには基準電圧VREFが供給される。この切換は、平滑端子32の電位に応じて切換制御回路36が自動的に行う。

(もっと読む)

半導体装置

【課題】USBクロックやシステムクロック等を使用する半導体装置において、汎用性を向上することができる技術を提供する。

【解決手段】複数のクロック(入力クロック1、入力クロック2)を入力とし、その複数のクロックのそれぞれを入力クロック1カウンタ110a及び入力クロック2カウンタ110bで一定期間計測し、その計測結果を用いて複数のクロックのそれぞれの周波数を検出し、その検出結果に基づいて、クロックソース選択回路107bで複数のクロックのいずれかを選択し、PLL回路2(108b)で逓倍し、分周回路2(109b)で分周し、USBクロックを生成する。

(もっと読む)

クロックおよび電源グリッドスタンダードセルを用いたASICデザイン

【解決手段】 ASICソフトウエアデザインツールを用いて配列および配線することができる集積または統合された電源およびクロックグリッド。集積されたグリッドは、電源レールとクロックラインを含む、3つのタイプのグリッドユニットを含む。電源レールおよびクロックラインは、種々のグリッドユニットセルにおいて種々の配向を含む。 (もっと読む)

121 - 140 / 211

[ Back to top ]