Fターム[5J039KK00]の内容

パルスの操作 (9,993) | 回路要素 (4,666)

Fターム[5J039KK00]の下位に属するFターム

非安定回路、発振回路 (298)

単安定回路 (7)

二安定回路 (568)

論理回路 (748)

遅延回路(遅延線を含む) (417)

積分回路 (81)

微分回路 (27)

定電流回路 (313)

差動増幅器 (237)

オペアンプ (72)

比較器 (415)

シュミット回路 (26)

波形整形回路 (39)

カウンタ (299)

シフトレジスタ (65)

分周回路 (200)

A/D,D/A変換回路 (157)

マルチプレクサ (134)

マトリックス回路 (4)

エンコーダ、デコーダ (47)

レートマルチプライヤ (2)

フィルタ(濾波器) (195)

レベルシフト回路 (45)

ピークホールド回路 (24)

リミッタ回路 (6)

クランプ回路 (29)

Fターム[5J039KK00]に分類される特許

141 - 160 / 211

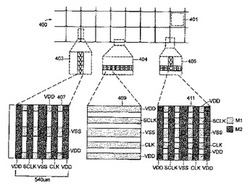

クロックおよび電源グリッドスタンダードセルを用いたASICデザイン

【解決手段】 ASICソフトウエアデザインツールを用いて配列および配線することができる集積または統合された電源およびクロックグリッド。集積されたグリッドは、電源レールとクロックラインを含む、3つのタイプのグリッドユニットを含む。電源レールおよびクロックラインは、種々のグリッドユニットセルにおいて種々の配向を含む。 (もっと読む)

比較器、DC−DCコンバータ、及びこれを利用した有機発光表示装置

【課題】信号の応答特性がよくなるようにして消費電力を減らすようにした比較器、DC−DCコンバータ、及びこれを利用した有機発光表示装置を提供する。

【解決手段】入力電圧Vin及び参照電圧Vrefとの差に対応して出力が決定される比較器であって、入力電圧及び参照電圧に対応する電圧を保存する電荷保存用キャパシタC10と、フィードバック電圧を分配する第1キャパシタC11と、電荷保存用キャパシタ及び第1キャパシタに保存された電圧に対応して信号を出力する少なくとも一つのインバータと、を含む増幅部と、増幅部から出力される電圧と、参照電圧が伝達される場合に増幅部から出力される電圧の伝達を受けてフィードバック電圧を生成し、当該フィードバック電圧を利用して入力電圧と参照電圧との差を調節する帰還部と、増幅部の出力の伝達を受けて出力する出力部と、を含む。

(もっと読む)

マルチセルコンピューティングシステムにおけるクロック分配

【課題】マルチセルコンピューティングシステムにおけるクロック分配を実現する。

【解決手段】

本発明に係るシステムは、複数のプロセッサを有する複数の処理セルを備える。処理セルは、a)抽出されたクロックが複製されて、それぞれが処理セルのプロセッサに供給される複数のクロックを提供することと、b)抽出されたクロックが、クロック源と共に位相情報として使用されて、処理セルのプロセッサに供給される複数のクロックを提供することとの少なくとも1つで使用される、抽出されたクロックを受信する。抽出されたクロックは、データと結合され、少なくとも2つの処理セルがスイッチを介して互いに通信することを可能にするリンクにより処理セルへ送信された、符号化されたクロックから抽出される。

(もっと読む)

データ処理装置

【課題】A/D変換器のサンプリング周波数を高速化することなく、高周波ノイズが入力した場合の誤動作を簡易的に防止することができるデータ処理装置を提供する。

【解決手段】A/D変換器からのサンプリング値Snを記憶した後、ピーク値Spと比較し、ピーク値Spより大きいとき、ピーク値Spを更新する。一方、サンプリング値Snがピーク値Spより小さい場合、サンプリング値Snがオフセット値(0V)より小さく、ピーク値Spが0.1Vより大きいとき、ピーク値Spのサンプリング値Snを記憶しているメモリの記憶領域にフラグをセットし、一定期間内のフラグの数が4より大きいと判定した場合、高周波ノイズが含まれていると判断し、データ処理部での判定を禁止する。

(もっと読む)

半導体集積回路のクロック構成方法およびそのプログラム

【課題】実際のデバイス上でのクロックスキューの増大を抑制し、オンチップばらつき耐性を強くする。

【解決手段】所定数のフリップ・フロップ(FF)を含む領域G1〜G8を2つの群に群分けする。このとき、境界線の横切るデータ接続経路の数が最小となるようにする。ここでは、データ接続経路A1、A2を横切るようにすると、境界線が横切るデータ接続経路数が2で最小となる。さらに、領域G1〜G4、領域G5〜G8を群分けした後に、クロックツリー合成(CTS)を行う。このようにしてクロック構成を行うことにより、実際のデバイス上でのクロックスキューの増大を抑制し、オンチップばらつき耐性を強くすることができる。

(もっと読む)

昇圧回路

【課題】レイアウトの小面積化を実現する標準CMOSプロセスのLSIに混載可能な昇圧回路を提供する。

【解決手段】各段がMOSトランジスタ(M04、M14、M24、M34)と、前記MOSトランジスタのドレイン又はソースの一方に一端が接続されたキャパシタ(C14、C24a、C24b、C34a、C34b、C34c)とからなり、前記MOSトランジスタが縦列接続されることによって各段が接続され、各段における前記MOSトランジスタのゲートとドレイン又はソースの一方とが互いに電気的に接続されるとともに、少なくとも1組の隣接するMOSトランジスタの基板がその一方のドレイン又はソースの一方と電気的に接続される。バックバイアス効果が抑制され、かつレイアウト面積を縮小することができる。また、後段の昇圧キャパシタを複数の直列キャパシタで構成することにより、各キャパシタの耐圧劣化を抑制することができる。

(もっと読む)

状態検出回路及び発振停止検出装置

【課題】 従来の発振停止検出回路は、クロック信号が何ら停止していないにも拘わらず、通常用電源電圧及び予備用電源電圧の切り替えにより、瞬間的に、クロック信号が停止している旨が出力されるという問題があった。

【解決手段】 本発明に係る発振停止検出回路は、インバータ回路と、1段目、2段目のトランジスタと、第1、第2のコンデンサと、抵抗器と、相互に並列接続された第1、第2のトランジスタと、通常用電源電圧の入力及び予備用電源電圧の入力を選択的に受け、第1のトランジスタの入力端に、通常用電源電圧の入力を受けるとき定電圧を出力し、予備用電源電圧の入力を受けるとき予備用電源電圧を出力する定電圧生成回路とを含む。

(もっと読む)

パルス信号測定装置及び方法

【課題】パルス信号の入力及びオーバーフローの双方について割り込み信号を発生するタイマを用いてパルス信号の幅や周期を正確に測定可能なパルス信号測定方法を提供する。

【解決手段】リロードレジスタへリロードすると共に割り込み信号を出力し、カウント値がオーバーフローした場合にはリロードレジスタへリロードせずに割り込み信号を出力すると共にオーバーフローフラグをオン状態にするタイマを用いてパルス幅又は周期を測定する際に、割り込み信号を受けてリロードレジスタのカウント値を読み出し(ステップST1)、タイマのオーバーフローフラグの状態を判別し(ステップST2)、オーバーフローフラグがオンしている場合に、リロードレジスタから読み出した今回値と前回値との比較に基づいてパルス信号の入力の有無を判断する(ステップST6)。

(もっと読む)

比較器

【課題】比較器を提供する。

【解決手段】本発明は、第一の入力端子と第二の入力端子、第一の出力端子と第二の出力端子、第一の入力インバータと第二の入力インバータ、第一のロードインバータと第二のロードインバータ、及び、第一のロードインバータと第二のロードインバータの入力端子にそれぞれ第一のバイアス電圧と第二のバイアス電圧を印加するバイアス制御回路を含む比較器を提供する。

(もっと読む)

スイッチ制御回路、ΔΣ変調回路、及びΔΣ変調型ADコンバータ

【課題】積分器の積分精度及びΔΣ変調回路の変調精度を向上させ、ΔΣ変調型ADコンバータにおける歪率劣化を抑制する。

【解決手段】第1〜第4スイッチを有するスイッチドキャパシタを用いて構成される積分器の前記第2及び第3スイッチと、前記第1及び第4スイッチとを相補的にオンオフするスイッチ制御回路であって、前記第1及び第4スイッチをオフ、前記第2及び第3スイッチをオンにする際には、前記第4スイッチをオフにする前に、前記第2スイッチをオンにする。

(もっと読む)

チョッパアンプ回路および半導体装置

【課題】 センサブリッジのオフセット電圧及びオフセット電圧の温度特性を低減可能なチョッパアンプ回路の提供。

【解決手段】 センサブリッジのオフセット電圧と等しい電圧を発生するオフセット調整電圧発生回路と、オフセット電圧の温度特性と等しい電圧を発生するオフセット温度特性調整電圧発生回路とを設け、これらの出力電圧をチョッパ変調して、チョッパ変調されたセンサブリッジの出力信号から減算する構成とした。

(もっと読む)

電力/ダイエリア削減を目的とするクロックスペクトラム拡散(ディザリング)回路の完全デジタル化

【課題】クロック列をデジタル的にスペクトラム拡散する。

【解決手段】クロック列を形成するクロック、及びクロック列を変調し、ディザリングされたクロック列を生成するべく、クロック列の周波数を時間変動分周値によって分周する可変分周器を有する。本回路は更に、周波数変調波形を生成するべくディザリングされたクロック列を蓄積する第1のアキュムレータ、及び位相変調信号を生成するべく、周波数変調波形を蓄積する第2のアキュムレータを有する。本回路は更に、位相変調信号に基づいて、時間変動分周値を計算する位相値計算器、及び最初に述べたクロック列の拡散スペクトラムである第2のクロック列を生成するべく、ディザリングされたクロック列の変調をトラッキング及びフィルタリングするクローズドループ制御回路を有する。

(もっと読む)

電子回路装置のEMI対策方法及び回路

【課題】 放射ノイズ低減とアナログ制御信号精度とのトレードオフ対策。

【解決手段】 システムコントローラーチップに供給する電源電圧にリップルを重畳することにより、動作クロックの周波数拡散を発生させて放射ノイズの低減を図る。システムチップから出力する信号の電圧安定化のために、チップ外部にゲートを設けて安定した電源で駆動する。

【選択図 】図1

(もっと読む)

半導体装置

【課題】本発明は、低いコストでワンチップLSIと同等のデータ転送速度を達成する半導体システムを提供することを目的とする。

【解決手段】半導体装置は、外部から受信した受信クロック信号を入力として内部クロック信号を供給する内部クロック発生回路と、チップの一辺に配置され該内部クロック信号を出力するクロック送信用端子と、該一辺に配置された複数の入出力端子と、該内部クロック信号に基づいて入出力制御用クロック信号を生成する制御用クロック発生回路と、該入出力制御用クロック信号に同期して該入出力端子を介して外部へのデータ出力及び外部からのデータ取り込みを行う複数の入出力回路と、該制御用クロック発生回路と該複数の入出力回路の各々とを接続する同一長の複数の接続配線を含むことを特徴とする。

(もっと読む)

クロック回路のための方法及びシステム

【課題】半導体に与えるクロック信号の一部の周波数を低減出来る回路を提供すること。

【解決手段】1組の時間インターバルを有するカウンタ信号122を出力するように動作するカウンタ回路120と、出力クロック信号114を発生するように動作するゲート回路110とを具備し、前記出力クロック信号114は、第1の動作モードにおいては、入力クロック信号112と実質的に同一であり、第2の動作モードにおいては、1組の時間インターバルのうちの少なくとも1つの時間インターバル中に、前記入力クロック信号112に実質的に等しくされている。

(もっと読む)

スイッチ動作検出回路

【課題】 スイッチ回路から出力されるオン/オフ信号を高精度に検出することが可能なスイッチ動作検出回路を提供できるようにする。

【解決手段】 スイッチ回路1からオン/オフ信号Sinが入力されると、所定の短い期間よりも長く、かつ所定の長い期間よりも短い期間において、前記オン/オフ信号Sinの電位反転が発生したか否かを検出する電位判定検出回路18と、前記電位判定検出回路18の検出結果に基づいて、予め設定された所定波形の開閉検出信号を生成して出力する開閉検出信号出力回路17とを設け、オン/オフ信号Sinを検出する精度を向上させることができるようにする。

(もっと読む)

周波数逓倍回路

【課題】 ディレイラインによるPLL技術を用いた周波数逓倍回路におけるEMIノイズを抑制する。

【解決手段】 本発明の周波数逓倍回路は、電圧制御遅延回路(Delay)と、N個のDelayにCLKが入力され、CLKを位相遅延させてDELCLKを生成するディレイライン11aと、位相ロック状態において所定の電圧をGNV0に出力する遅延制御回路12aと、N個のDelayにCLKが入力され、当該Delayの各出力から異なる位相遅延量を持つN個の出力クロック信号(OUTn)を生成するディレイライン11bと、GNV0および複数の異なる基準電圧Snに基づいて、ディレイライン11bの位相遅延量を電圧制御する遅延制御回路12bと、OUTnを論理演算し、周波数がCLKの略N/2倍であるCLKOUTを生成する論理回路14を有する。

(もっと読む)

データスライサ

【課題】入力信号を適切にスライス可能なデータスライサを実現する。

【解決手段】現在の入力電圧信号の最大値と最小値とだけではなく、入力電圧信号に含まれるヘッダパターンにおける平均電圧と、ヘッダパターン検出完了時のピーク電圧・ボトム電圧とにも基づいて、スライスレベルを算出する。具体的には、スライスレベルをS15、ヘッダパターンの平均電圧をS6、ヘッダパターン検出完了時のピーク電圧をS7、ヘッダパターン検出完了時のボトム電圧をS8、最大電圧検出・保持部に保持された最大電圧をS10、最小電圧検出・保持部に保持された最小電圧をS11として、スライスレベルの電圧値を、S15=S6+(S10+S11)/2−(S7+S8)/2と算出する。

(もっと読む)

構造化されたASICデバイスのためのクロック信号ネットワーク

【課題】クロック信号の好適な分配を行うことができる構造化されたASICデバイスを提供する。

【解決手段】構造化されたASIC(10)デバイスのクロック分配回路構成(200)は、決定性(deterministic)の部分および複数の設定可能な部分を含む。その決定性の部分は、コンダクタ(40)セグメントの所定の配置を用い、デバイス上の複数の所定のロケーションへ、クロック信号を分配するために、回路をバッファする。それぞれの所定のロケーションから、クロック分配回路構成の関連される設定可能な部分は、そのクロック信号を、その所定のロケーションから提供された、構造化されたASIC(10)の所定の領域においてそのクロック信号を必要とする任意のクロック利用回路構成に分配する。

(もっと読む)

比較回路

【課題】比較回路の入力端子に負電圧が印加されたときの出力信号の反転を防止する。

【解決手段】負電圧が印加される第1の入力端子(5)又は第2の入力端子(6)に接続された一方の主端子及び出力スイッチ(7)の制御端子に接続された他方の主端子を有する補償スイッチ(10)の制御端子をグラウンドに接続することにより、補償スイッチ(10)の何れかの主端子に接続された第1の入力端子(5)又は第2の入力端子(6)に負電圧が印加されたときに、補償スイッチ(10)がオンに切り換えられ、出力スイッチ(7)の制御端子がゼロボルト未満の負電位まで低下するので、出力スイッチ(7)をオフ状態に維持でき、出力スイッチ(7)は誤動作を発生しない。

(もっと読む)

141 - 160 / 211

[ Back to top ]