Fターム[5J039KK04]の内容

Fターム[5J039KK04]の下位に属するFターム

Fターム[5J039KK04]に分類される特許

61 - 80 / 163

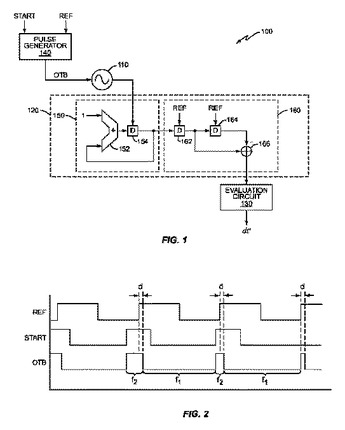

ノイズシェーピング時間測定回路

時間測定回路のある実施形態では、リファレンス信号期間の第1の部分においてデジタル制御発振器(DCO)を第1の周波数で動作させ、前記対象信号と前記リファレンス信号との時間差に応じて前記リファレンス信号期間中に動作周波数を前記第1の周波数から第2の周波数に変更することにより、対象信号とリファレンス信号の時間差が測定される。時間測定回路は、前記リファレンス信号期間において前記デジタル制御発振器の出力で何回の信号遷移が発生したかを継続的に計数する。対象信号とリファレンス信号の時間差は、前記リファレンス信号期間において計数された前記信号遷移の回数に基づいて推定される。

(もっと読む)

(もっと読む)

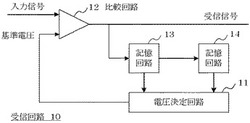

受信回路、電子機器、及び受信回路の制御方法

【課題】 直前の数サイクルに依存して波形が劣化する信号に対して正しく受信することができない。

【解決手段】 本発明の受信回路10は、入力信号を基準電圧と比較して比較結果をハイレベル又はローレベルで出力する比較回路12と、比較回路12の出力レベルを次の1サイクル間保持する第1の記憶回路13と、第1の記憶回路13の出力レベルを次の1サイクル間保持する第2の記憶回路14と、第1の記憶回路13と第2の記憶回路14の出力レベルに応じて前記基準電圧のレベルをサイクル毎に制御する電圧制御回路11を有する。

(もっと読む)

クロック信号供給回路の設計方法、情報処理装置およびプログラム

【課題】半導体集積回路におけるクロック信号の供給において、回路全体を通しクロックラインを短縮し得る構成を提供することを目的とする。

【解決手段】回路素子のグループ間で回路素子の交換、移動を実行し、当該実行の前後でグループごとに回路素子の位置と中心位置との距離の合計し更に全グループについて合計した値が減少する場合には当該実行後のグループを維持し減少しない場合には当該実行前のグループを維持する最適化を実行する構成である。

(もっと読む)

DLL回路及びその制御方法

【課題】冗長な回路、配線を不要とし、回路規模の増大を回避し、デューティを変更可能とするDLLを提供する。

【解決手段】外部信号の第1遷移(Rise)を可変に遅延させる第1可変遅延回路(10R)と、外部信号の第2遷移(Fall)を可変に遅延する第2可変遅延回路(10F)と、第1可変遅延回路(10R)の出力信号と第2可変遅延回路(10F)の出力信号とを合成する合成回路(13)と、合成回路(13)の出力信号のデューティの変更と検出を行うデューティ変更検出回路(21)と、デューティ変更検出回路(21)のデューティ検出結果(DCC)に従って第1可変遅延回路(10R)又は第2可変遅延回路(10F)の遅延を可変させる遅延制御回路(15R、15F)と、を備える。

(もっと読む)

半導体装置及びその制御方法

【課題】半導体装置の製造ばらつきや経年劣化に起因するクロックスキューを補正することができる半導体装置を提供する。

【解決手段】スキュー検出部6は、スキューを検出するための少なくとも1個のクリティカルパス7又はレーシングパス7を含む。クロック調整部5は、スキュー検出部6により検出されたスキューに基づいて、ディレイの設定値を設定する。クロックセル4は、ディレイの設定値に応じて、第1のクロックのディレイを調整して、第2のクロックとして出力する。

(もっと読む)

I2Cインタフェースを有するシステム及びその方法

【課題】本発明の目的は、I2Cインタフェースを有するシステムを提供することである。

【解決手段】本発明の第1の態様によると、マスター装置と前記マスター装置により制御されるスレーブ装置との間のインタフェースをとるI2Cインタフェースを有するシステムが提供される。前記マスター装置は第1のデータ・バスと接続され第1の駆動電圧で動作し、前記スレーブ装置は第2のデータ・バスと接続され第2の駆動電圧で動作し、前記システムは、それぞれ前記第1及び第2の駆動電圧の間のレベルシフト機能を有する第1及び第2の双方向デジタル入出力回路、及び前記第1及び第2の双方向デジタル入出力回路を制御するシーケンサ回路、を有し、前記シーケンサ回路は、前記第1及び第2の双方向デジタル入出力回路の出力に基づき、データの伝達方向を前記マスター装置から前記スレーブ装置へ、又は前記スレーブ装置から前記マスター装置へ切り替える。

(もっと読む)

コンパレータ回路

【課題】

MOSトランジスタの閾値電圧の差によって発生するオフセット電圧の影響を軽減させ、比較精度の高いコンパレータ回路を提供する。

【解決手段】

各スイッチがオンにされているキャリブレーションモードにおいて、第1のキャパシタCaおよび第2のキャパシタCbに、出力部5におけるプラス側とマイナス側の出力電圧を記憶させる。各スイッチがオフに切り替わり比較モードに移行すると、第1のMOSトランジスタM6および第2のMOSトランジスタM7のゲートに、キャパシタCaおよびCbが記憶したそれぞれの電圧が印加されて補正電圧を基準としたラッチ動作の準備が整う。電流ラッチ回路2は、入力電圧と基準電圧の差を増幅させてHIGHまたはLOWを出力する判定を行う。出力部5では、HIGHまたはLOWに応じた電圧差が生じ、これに応じた電流が流れる。

(もっと読む)

信号処理回路

【課題】高速信号を符号間干渉なく信号を受信することができる信号処理回路(コンパレータ回路)を提供することを課題とする。

【解決手段】入力信号から出力信号への信号伝達特性がクロック信号により変化するように入力信号を処理して出力信号を出力する入力回路(3111)と、クロック信号により活性化状態になった期間に入力回路の出力信号を増幅する増幅回路(3102)とを有する信号処理回路が提供される。

(もっと読む)

比較演算増幅回路、AD変換回路、電子機器

【課題】比較演算増幅回路やAD変換回路において、回路規模や消費電力のさらなる低減を図る。

【解決手段】サンプルホールド回路503では、複数のサンプルホールド回路と信号選択回路により、AD変換対象の差動アナログ信号対について、ホールドモード時の出力信号対を時分割で出力するようにする。フォールディング方式を採らないAD変換においては、比較演算増幅回路501は、時分割で供給される複数の出力信号対について、信号選択回路により複数の差動基準信号対を時分割で扱うように切り替えながら、各出力信号対と各差動基準信号対の差を各差動増幅回路で増幅することで複数の増幅出力信号対を時分割で出力するようにする。デジタルデータ取得部6は、時分割で供給される複数の増幅出力信号対の差をそれぞれ2値化することでデジタルデータを取得する。

(もっと読む)

スケルチ検出回路

【課題】温度、プロセス、電源電圧の変動に強く、安定したスケルチ検出信号を出力することができるスケルチ検出回路を提供する。

【解決手段】受信した差動信号RX+,RX−の電位振幅が所定値を超えているときその検出信号Vpをパルスとして出力するピーク検出回路11と、ピーク検出回路11から出力する検出信号Vpのパルス幅を差動信号RX+,RX−の少なくとも1周期分延長するパルス幅延長回路12とを備える。ピーク検出回路11は、差動信号RX+,RX−に同一のDCバイアスを与えた後にその差分に対応する電圧信号Vdataを出力する入力差動増幅回路11Aと、入力差動増幅回路11Aのほぼレプリカ回路として構成され、参照電圧Vref’をレベルシフトしたシフト参照電圧Vrefを出力するレプリカ参照電圧生成回路11Bと、電圧信号Vdataとシフト参照電圧Vrefとを比較して検出信号Vpを出力する電圧比較回路11Cと、を備える。

(もっと読む)

自動クロック切替回路および方法、ならびに電子機器

【課題】入力されたクロックが適切なものであるか常時監視することができ、クロックの切り替えを常時適切に行うことができるようにする。

【解決手段】判定回路10に固定クロックCLK1を常時入力する。判定回路10では、その常時入力される固定クロックCLK1に基づいて対象クロックCLK2の状態を監視し、対象クロックCLK2が入力停止状態にあるか、もしくは対象クロックCLK2の周波数が所定の周波数の範囲外にあるか否かを判断する。固定クロックCLK1を常時入力としているため、常にクロックの判定を行うことが可能であり、固定クロックCLK1から対象クロックCLK2へ、または対象クロックCLK2から固定クロックCLK1への切り替えが常時可能となる。また、対象クロックCLK2の入力停止状態から所望とするクロックの周波数範囲の判定まで、切れ目のない判定が可能となる。

(もっと読む)

セットアップ/ホールドタイム測定装置

【課題】テスト信号に応じて外部クロック信号からデータ信号と内部クロック信号を生成し、読取り/書込み動作無しでバッファリングされたデータの状態によってセットアップ/ホールドタイムを測定できるようにしたセットアップ/ホールドタイム測定装置を提供する。

【解決手段】外部クロック信号をカウント信号によって遅延させ、テスト信号に応答して、前記遅れた外部クロック信号から内部クロック信号及びデータ信号を生成するデータ生成部と、前記内部クロック信号に同期して、前記データ信号をバッファリングした信号をラッチするデータラッチと、前記テスト信号に応答して、前記データラッチ部でラッチされたデータ信号からフラグ信号を生成するフラグ信号生成部と、前記フラグ信号に応答して前記カウント信号をカウンティングするカウンターと、を含む構成とした。

(もっと読む)

リタイミング回路及び分周システム

【課題】クロック信号の同期エッジのタイミングと入力信号のエッジのタイミングが一致したときの誤動作を防止することができるリタイミング回路及び分周システムを提供することを課題とする。

【解決手段】第1及び第2のクロック端子に差動クロック信号を入力し、第1及び第2の入力端子に第1の差動信号を入力し、第1及び第2の出力端子から第2の差動信号を出力する第1のフリップフロップ回路(102)と、前記第2の差動信号を構成する第1及び第2の信号が同相になると同相検出信号を出力する同相検出回路(105)と、前記同相検出信号のカウント値をカウントするカウンタ(106)と、前記カウンタのカウンタ値に応じて前記第1のフリップフロップ回路の前記第1及び第2のクロック端子に入力する前記差動クロック信号の位相を切り換えるセレクタ(101)とを有することを特徴とするリタイミング回路が提供される。

(もっと読む)

差動電圧比較器及び差動回路

【課題】NBTI劣化又はPBTI劣化による入力トランジスタの閾値のバラツキの増大化を抑制することにより、入力オフセット電圧の増大化を抑制し、例えば、A/D変換器に使用する場合には、INLやDNL等のA/D変換精度の劣化を抑制することができるようにした差動電圧比較器を提供する。

【解決手段】入力制御部28は、判定結果出力期間の間は、入力電圧VIP及び入力電圧VIMの差動回路3の非反転入力端子3A及び反転入力端子3Bへの供給を遮断し、差動回路3の非反転入力端子3A及び反転入力端子3Bに電源電圧VDDを供給し、差動回路3の入力トランジスタをなすPMOSトランジスタのゲート−バルク間電圧を0Vにする。

(もっと読む)

単一電圧源CMOSのための自動検出入力回路

【課題】入力パッドに印加される比較的高電圧を維持し、回路内の供給電圧範囲の対応する信号レベルを生成する。

【解決手段】入力回路は、フローティングウェルと、対応するバイアスセレクタと、入力バイアストランジスタとを有し、予め定められた値より大きい電圧を維持する外部電圧にゲート酸化膜がさらされないようにする。バイアスセレクタは、利用可能な最高電圧を選択してフローティングウェルに対応するバイアスを逆にし、トランジスタに過度な電気的ストレスがかからないようにする。入力に関連する端子が関連する電圧を切り換えられると、バイアスセレクタは、別の端子を選択し、引き続き利用可能な最高電圧を選択して正しい逆バイアス条件を提供する。抵抗器およびクランプは、回路内の供給電圧範囲に制限された、変換された出力電圧レベルを生成する。ラッチ出力により、プルダウントランジスタは、正確なロウレベル出力信号を提供できる。

(もっと読む)

周波数異常検出回路

【課題】従来の、監視クロックが被監視クロックよりも高い周波数を使用する周波数異常検出回路は、高コストかつノイズ対策が必要で実装が困難であり、また、監視クロックが被監視クロックよりも低い周波数を使用する周波数異常検出回路は、クロック固着のタイミングによっては異常を検出できないだけでなく、リセット時にシフトレジスタを構成するすべてのレジスタ出力が“0”となるので、警報が発出されないようにする構成を別途設けなければならない問題があった。

【解決手段】クロック周波数の上限異常は被監視クロック数のカウント数と上限値との大小比較にて検出し、下限異常は、同期化した監視クロックの立ち上がりエッジにて出力する正極性パルスと、当該パルス出力で”High”を出力する初回エッジホールド回路出力と、下限値と被監視クロック数のカウント値の大小を比較するコンパレータ出力との論理積の出力にて検出すること。

(もっと読む)

半導体素子の内部電圧生成回路及び内部電圧生成方法

【課題】外部クロックの周波数の変動にかかわらず、常に安定した電圧レベルを維持できるようにする半導体素子の内部電圧生成回路を提供すること。

【解決手段】本発明は、内部電圧端の電圧レベルが所定の目標レベルより低くなる期間において、前記内部電圧端をプルアップ駆動する第1電圧駆動手段20と、外部クロックの周波数に対応する周期の1周期毎に、所定時間の間、前記内部電圧端をプルアップ駆動する第2電圧駆動手段22とを備える半導体素子の内部電圧生成回路を提供する。

(もっと読む)

クロック分配回路のレイアウト生成方法、および半導体集積回路装置

【課題】再収斂分岐構造を含むクロック分配回路のレイアウト生成において、冗長な迂回配線を生じさせることなく、クロックスキューを低減可能にする。

【解決手段】クロック分配回路の基本セル構成を解析し(S201)、解析された基本セル構成を基にして、クロック経路にクロックバッファを挿入する(S202)。その後、基本セルとクロックバッファとを配置し(S203)、配線を配置する(S105)。解析ステップ(S201)において、クロックの各経路における基本セルの段数の最大値を求め、挿入ステップ(S202)において、クロックの各経路におけるセル段数が、この最大値以上でかつ同じ値になるように、クロックバッファを挿入する。

(もっと読む)

信号処理装置

【課題】0と1の出現確率が異なるデータ信号のデューティサイクルの歪みを補正する。

【解決手段】位相検出回路21は、0と1の出現確率が異なるデータ信号の位相の進みおよび遅れを検出する。AND回路43はデータ信号の立ち上がりを検出し、AND回路44は立ち下がりを検出する。+DCD検出回路45は、位相検出回路21とAND回路43および44の検出結果に基づいて、デューティサイクルのプラス側の歪みを検出し、−DCD検出回路46は、デューティサイクルのマイナス側の歪みを検出する。デューティ調整回路12は、+DCD検出回路45と−DCD検出回路46の検出結果に基づいて、デューティサイクルを調整することにより、デューティサイクルの歪みを補正する。本発明は、例えば、データ信号を受信する受信装置に適用することができる。

(もっと読む)

半導体装置

【課題】 この発明は、テスト兼用端子に高電圧のノイズが入力された場合でも容易にテストモードに入ることのない半導体装置を提供する。

【解決手段】 この発明は、通常動作モードと、テストモードを備えた半導体装置において、前記半導体装置は、振幅が電源電圧以内の通常信号と振幅が前記電源電圧より高い高電圧信号の入力が可能なテスト兼用入力端子Aと、テスト兼用入力端子Aに入力される高電圧信号を検出する高電圧検出回路10と、高電圧検出回路10からの高電圧信号が所定のパターンで変化したことを検出するパターン検出回路20と、検出したテスト兼用入力端子Aから高電圧信号が所定のパターンで印加された場合に、前記通常動作モードから前記テストモードに切り換える切り替え手段30と、備えた。

(もっと読む)

61 - 80 / 163

[ Back to top ]