Fターム[5J039KK04]の内容

Fターム[5J039KK04]の下位に属するFターム

Fターム[5J039KK04]に分類される特許

81 - 100 / 163

フリップフロップ回路

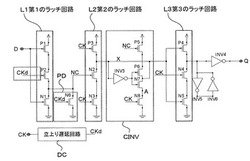

【課題】不感帯が少なく高速安定動作が可能なフリップフロップ回路を提供すること。

【解決手段】本発明は、データ信号Dと、立ち上がり遅延クロック信号CKdとを入力し、データ信号Dの立ち下がりと立ち上がり遅延クロック信号CKdの立ち下がりとによって内部ノードNCの信号を立ち上げる第1のラッチ回路L1と、内部ノードNCの信号とクロック信号CKとを入力し、内部ノードNCの信号が立ち上がっている状態でクロック信号CKが立ち下がるタイミングにより内部ノードXの信号を立ち下げる第2のラッチ回路L2と、内部ノードXの信号とクロック信号CKとを入力し、クロック信号CKが立ち上がっている状態でのデータ信号Dを保持する出力信号を生成するための第3のラッチ回路L3と、内部ノードNCの信号を立ち上がり遅延クロック信号CKdによってプルダウンさせるプルダウン回路PDとを備えるフリップフロップ回路である。

(もっと読む)

半導体集積回路

【課題】動作モードによって周波数変調を行うか行わないかを選択することによって受信側の負荷を低減することができる半導体集積回路を提供すること。

【解決手段】半導体集積回路1は、2以上の内部回路(ビデオデコーダ11、CPU12など)と、所定の周波数のクロックを発生するPLL31と、周波数を変調させたクロックを発生するSSCG PLL32と、内部回路にPLL31からのクロックか、SSCG PLL32からのクロックのいずれかを選択して内部回路に入力するセレクタ21とを有する。

(もっと読む)

ヒステリシスコンパレータ

【課題】入力信号の振幅が当初の想定よりも小さい場合や入力信号の振幅変動が生じた場合でも、適正な出力信号を得ることができるヒステリシスコンパレータを提供する。

【解決手段】電圧レベルが連続的に変化する入力信号を互いに異なる電圧レベルを有する2つの閾値電圧に基づいて2値化判定し、この判定結果に応じた出力信号を生成するヒステリシスコンパレータであり、入力信号のトップピークを検出し、トップピークに応じたトップピーク検出電圧を生成するトップピーク検出部と、入力信号のボトムピークを検出し、ボトムピークに応じたボトムピーク検出電圧を生成するボトムピーク検出部と、トップピーク検出電圧の電圧レベルとボトムピーク検出電圧の電圧レベルの範囲内で第1および第2の閾値電圧を生成する閾値電圧生成部と、第1および第2の閾値電圧と入力信号の電圧レベルを比較して入力信号を2値化判定し、この判定結果に応じた出力信号を生成する電圧比較部と、を含む。

(もっと読む)

クロック分配システム、分配方法、それらを利用した集積回路

【課題】消費電力と劣化を低減する。

【解決手段】集積回路にクロック信号を分配する装置100、方法が提供される。低速モード動作において、周期ごと、少なくとも、異なる第1、第2オン時間を有する第1、第2オンパルスを含み、第1、第2オン時間の合計が、各周期のオフ時間の合計と略等しい第1クロック信号200が生成される。分配クロック信号204それぞれを生成する複数の最終段のバッファ回路17が終点である分配ツリー16を介して第1クロック信号200が分配される。分配クロック信号204それぞれから、集積回路の少なくとも一部に供給すべき対応する第2クロック信号202が生成される。

(もっと読む)

半導体集積回路

【課題】雑なクロック選択回路に対応できる半導体集積回路を、簡単な配置クラスタリング工程で作製できるようにする。

【解決手段】クロック信号を種々の遅延量で遅延調整するクロックツリー回路と、遅延調整されたクロック信号が供給されるクロック同期回路とを備える。クロックツリー回路は、クロック信号導入端の後段に設けられた第一のクロックツリーセルと、クロック同期回路の前段でかつ第1のクロックツリーセルより後段に設けられた第二のクロックツリーセルと、第二のクロックツリーセルの前段に設けられたクロック分岐点とを備える。クロック同期回路は第二のクロックツリーセルで遅延調整されたクロック信号が供給される第一のクロック同期回路とクロック分岐点でクロックツリー回路から出力されるクロック信号が供給される第二のクロック同期回路とを備える。

(もっと読む)

ジッタ印加回路、パターン発生器、試験装置、および、電子デバイス

【課題】高周波数かつ大振幅のジッタを生成する。

【解決手段】ジッタを有するジッタ重畳信号を生成するジッタ印加回路であって、与えられる基準信号を、それぞれ予め設定される遅延量で順次遅延させる、縦続接続された複数の遅延回路と、それぞれの遅延回路が出力する信号のタイミングに応じて、ジッタ重畳信号のそれぞれのエッジを生成する信号生成部と、ジッタ重畳信号の各周期に印加すべきジッタに応じた遅延量をそれぞれ設定する遅延設定部とを備え、少なくとも一つの遅延回路の遅延量が、ジッタ重畳信号の平均周期の整数倍とは異なる値に設定されるジッタ印加回路を提供する。

(もっと読む)

電源装置及び電源装置におけるタイミング制御回路

【課題】電源投入時に流れる突入電流を削減すること。

【解決手段】商用電源2から電気機器3に電力を供給する電源装置1において、ON/OFFスイッチ22をONするとタイミング制御回路7で制御された無接点リレー6Aが交流波形の立ち下がりのゼロクロス点で交流電源電圧の供給を開始し、かつ、ON/OFFスイッチ22をOFFするとタイミング制御回路7Aで制御された無接点リレー6Aが交流波形の立ち下がりのゼロクロス点で交流電源電圧の供給を終了するようにした。

(もっと読む)

集積回路装置

【課題】データ信号を入出力可能な集積回路装置において、より適正に入力されているデータ信号を出力する。

【解決手段】集積回路装置10において、データ信号Dが通常入力時より遅延してフリップフロップFFのセットアップ時間制約に違反したタイミングでデータ信号Dが変化したときにはデータ信号Dが変化してから所定時間後に立ち上がるフリップフロップ制御用信号Gを生成して出力するようエッジ検出回路20とフリップフロップ制御用信号出力回路30とを構成し、こうして生成したフリップフロップ制御用信号Gと基準クロック信号Clkとを用いてデータ信号Dを入出力するようフリップフロップFFを構成した。これにより、より適正にデータ信号Dを入出力することができる。

(もっと読む)

モニタ回路及び電力低減システム

【課題】LSIテスト時においても選別用のモニタリングを行うことができると共に、小さな面積で簡便な構成によりモニタ可能なモニタ回路を提供すること。

【解決手段】モニタ回路は、クロック信号39に同期して入力信号を取り込むフリップフロップ回路32と、クロック信号40に同期して入力信号を取り込むフリップフロップ回路34と、フリップフロップ回路34の出力信号を受ける論理回路37と、クロック信号40に同期して論理回路37の出力信号を取り込むフリップフロップ回路35とを含み、クロック信号40の立ち上がりエッジ位置を調整し、フリップフロップ回路32の出力信号とフリップフロップ回路35の出力信号とが所定の組合せとなったときの、調整したクロック信号40の立ち上がりエッジ位置とクロック信号39の立ち上がりエッジ位置とに基づいてチップの性能を判別する。

(もっと読む)

半導体装置

【課題】消費電流を低減し、差動増幅動作の高速化を図り、かつ小型化を図ることが可能な半導体装置を提供する。

【解決手段】半導体装置101は、制御電極が第1入力ノードに結合されたトランジスタMP1の第2導通電極に結合された第1導通電極と、第1出力ノードに結合された第2導通電極とを有するトランジスタMP3と、制御電極が第2入力ノードに結合されたトランジスタMP2の第2導通電極に結合された第1導通電極と、第2出力ノードに結合された第2導通電極とを有するトランジスタMP4と、第1出力ノード、トランジスタMP3の第2導通電極およびトランジスタMP4の制御電極に結合された第1端子を有する第1のキャパシタCL1と、第2出力ノード、トランジスタMP4の第2導通電極およびトランジスタMP3の制御電極に結合された第1端子を有する第2のキャパシタCL2とを備える。

(もっと読む)

短絡検出回路

【課題】本発明は、コストアップや電力損失を招くことなく、プッシュプル回路の出力短絡を検出することが可能な短絡検出回路を提供することを目的とする。

【解決手段】本発明に係る短絡検出回路は、パルス信号Vxと同期したダミーパルス信号Vyを生成し、両信号間に所定の位相差が生じているか否かに応じて、OUT1P端子の短絡検出を行う構成とされている。

(もっと読む)

データセンタートラッキング回路及びこれを含む半導体集積回路

【課題】本発明は、外部環境の影響にも安定的に動作し、より向上した電力及び面積効率を具現するデータセンタートラッキング回路及びこれを含む半導体集積回路を提供する。

【解決手段】本発明は、直列連結した複数のクロックバッファーからなり、クロックをバッファーリングして出力信号を出力するクロックツリー;クロックに基づき、出力信号の位相の変化を感知して感知信号を出力する感知部;及び、感知信号に応じて、クロックツリーに供給される電流を調節し、出力信号の位相を調節するディレイ補償部を含む。

(もっと読む)

半導体メモリ装置及びその動作方法

【課題】クロックのデューティ検出において、半導体メモリ装置内のプロセス、電圧レベル、及び温度などによる環境変数の変化によって発生するオフセットを除去するための初期測定動作を行うことができる回路を提供すること。

【解決手段】本発明に係る半導体メモリ装置は、初期測定動作時、共通クロックの遷移時点に対応する2つの検出パルスを生成するクロックエッジ検出部100Bと、前記2つの検出パルスを比較し、その結果を出力するデューティ検出部200Bと、前記初期測定動作時、デューティ検出部200Bから出力された比較結果に基づいて、デューティ検出部200Bを制御するコードカウンタ300とを備える。

(もっと読む)

A−D変換装置

【課題】電圧−周波数変換方式のA−D変換装置の精度を向上する。

【解決手段】2つの等価な鋸波発生回路18Aおよび18Bと、その2つの鋸波発生回路18Aおよび18Bを交互に切り替えるスイッチ回路19と、を含む電圧制御型発振器24を有する、電圧−周波数変換回路を備える。好ましくは、第1の周期の周期信号を出力する第1の電圧制御型発振器と、第1の周期と異なり、かつ第1の周期と一定の比を保つ第2の周期の周期信号を出力する第2の電圧制御型発振器とを備え、サンプリング周期内に含まれる第1の周期信号の波数に基づいて、入力であるアナログ信号に対応するディジタル信号の上位ビットを算出し、サンプリング信号の活性化時点から第1および第2の周期信号の位相が一致する時点までの間に含まれる周期信号の波数に基づいて、デジタル信号の下位ビットを算出する。

(もっと読む)

半導体記憶装置

【課題】入力データとデータストローブクロックのタイミングにより自動的にデータ入力ストローブ信号の発生タイミングをチューニングする半導体記憶装置を提供する。

【解決手段】入力データとデータストローブクロックの入力タイミングによりデータ入力ストローブ信号の発生タイミングをチューニングする内部チューニング手段と、前記データ入力ストローブ信号に応答して、複数のデータをグローバルラインに伝送するデータ入力センスアンプとを含む。

(もっと読む)

逆ヒステリシス回路

【課題】入力信号の周波数に変化が生じた場合であれ、確実に動作することの逆ヒステリシス回路を提供する。

【解決手段】逆ヒステリシス回路1は、第1インバータ10の出力信号である第1出力信号OUT1の電圧レベル及び第2インバータ20の出力信号である第2出力信号OUT2の電圧レベルの双方に基づいて、逆ヒステリシス回路1としての入力端子に入力される入力信号の立ち上がり時における閾値電圧レベルを第1閾値電圧レベルとし、入力信号の立ち下がり時における閾値電圧レベルを第2閾値電圧レベルとする出力信号を生成する出力信号生成部を備える。出力信号生成部30は、第1出力信号OUT1の電圧レベルに応じて動作する第1フリップフロップ32と、第2出力信号OUT2の電圧レベルに応じて動作する第2フリップフロップ35とを含んで構成されている。

(もっと読む)

ジッタ検出回路及びジッタ検出方法

【課題】PLL回路からの出力に含まれるジッタ成分及びデータパスの電源に含まれる周期的ノイズ成分を低減するクロック信号を生成する。

【解決手段】クロック信号120と変調制御信号127に基づいて生成された信号122とを混合して変調クロック信号123を生成するミキサ110と、遅延制御信号124に基づく遅延ステップで遅延された前記クロック信号若しくは前記変調クロック信号に同期したテストパターン信号と期待値データとが一致するか否かを判定し、判定結果を出力する内蔵自己テスト回路106と、前記判定結果をプロットしてシュムープロットを作成し、一致と不一致の境界線パターンに基づいて前記シュムープロットに含まれるノイズ成分を検出し、前記ノイズ成分と同じ周波数でかつ逆位相の信号を生成するように前記変調制御信号を出力する制御部107と、を備える。

(もっと読む)

プログラム可能な遅延を有するシーケンスが独立のオーバーラップしないディジタル信号発生器

【課題】オーバーラップしないクロック発生回路を提供する。

【解決手段】複数の遅延された基準クロック信号を生成するプログラム可能な遅延基準クロック信号回路と、プログラム可能な遅延基準クロック信号回路と動作可能に接続され、オーバーラップしないクロック信号を発生する複数の遅延クロック信号発生器とを含む。各遅延クロック信号発生器は、クロック信号の立ち上がりの遅延を制御し第1の信号を出力するラッチまたはフリップフロップと、遅延されたクロック信号の立ち下がりエッジの遅延を制御し第2の信号を出力するもう一つのラッチまたはフリップフロップと、第1および第2の信号からクロック信号を発生する論理回路とを含む。ラッチまたはフリップフロップは、複数の遅延された基準クロック信号の1つに応答してクロック信号の立ち上がりエッジの遅延を独立して制御する。

(もっと読む)

グリッチに備えるセルフタイマ回路の強化

グリッチに対する自己クロック回路を強化するための複数の技術が開示されている。グリッチフィルタが、デジタル設計の同じ場所に設けられている。ある実施例では、グリッチフィルタが動的に同調可能である。一実施例では、入力が出力によってロックアウトされる。差動信号のための回路のように、コード符号を見積もるための方法が与えられている。 (もっと読む)

半導体メモリ装置のクロック生成回路

【課題】本発明は、P.V.T変化及び伝送距離により、立ち上りクロック及び立ち下りクロックの遷移タイミングがずれることを防止できる半導体メモリ装置のクロック生成回路を提供する。

【解決手段】本発明は、クロックを遅延させて遅延クロックを生成し、前記クロックを反転させて反転クロックを生成する位相スプリッタと、遅延クロック及び反転クロックをバッファリングして、立ち上りクロック及び立ち下りクロックとして出力するクロックバッファを含む。

(もっと読む)

81 - 100 / 163

[ Back to top ]