Fターム[5J039KK04]の内容

Fターム[5J039KK04]の下位に属するFターム

Fターム[5J039KK04]に分類される特許

101 - 120 / 163

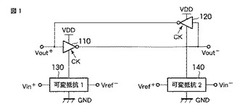

比較器及びこれを用いたアナログ−デジタル変換器

【課題】トランジスタのON抵抗または寄生容量による動作スピードの低下を防止可能な比較器を提供する。

【解決手段】正相入力信号と逆相基準信号との電圧に応じて抵抗値が変化する正相の可変抵抗部130と;逆相入力信号と正相基準信号との電圧に応じて抵抗値が変化する第2の可変抵抗部140と;クロック信号が第1レベルであれば第1及び第2のインバータの出力電位を第1または第2電源端子の電位にリセットする第1及び第2のスイッチと;第1レベルと第2レベル間を遷移するクロック信号を1つのゲート端子で受ける第1FinFETを含み、正相出力信号を反転させて逆相出力信号を出力する第1のインバータ110と;クロック信号を1つのゲート端子で受ける第1FinFETと同じ極性の第2FinFETを含み、逆相出力信号を反転させて正相出力信号を出力する第2のインバータ120と;を具備する。

(もっと読む)

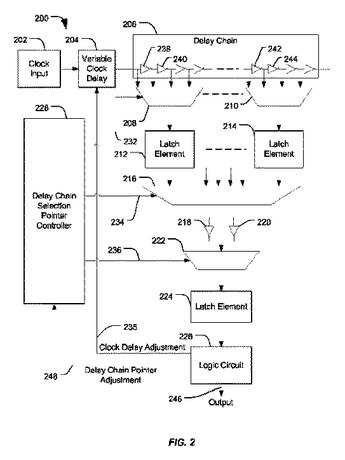

クロック・ジッタを測定する回路装置および方法

一実施形態では、回路装置の遅延チェーンにおいてクロック信号を受信すること、及び、該遅延チェーン内の選択される点において該クロック信号の値を決定すること、を含む方法が開示される。該方法は又、該値が該クロック信号のエッジの検出を示さない場合には、該選択される点を調整することを含む。  (もっと読む)

(もっと読む)

位相検出回路及びデータ処理装置

【課題】回路構成が簡素化され、低消費電力化され集積回路化する上で有利な構成の回路を得る。

【解決手段】第1クロックが各クロック入力端に与えられる複数段のフリップフロップ回路(Q1−Q7)と、第2クロックが入力される直列接続された複数段の遅延素子(D1−D6)と、前記複数段の遅延素子の出力をそれぞれ、前記複数段のフリップフロップ回路の各データ入力端に与える接続部(L1−L7)と、前記複数段のフリップフロップ回路の出力データが入力され、この出力データ内容に応じて変化する制御信号を得る信号生成回路(163)と、前記信号生成回路からの制御信号に応じて、前記第1若しくは第2クロックを相調整する位相調整信号を出力する位相調整信号出力部(164)を有する。

(もっと読む)

半導体装置

【課題】第三者による不正な攻撃によって故障動作を引き起こされた場合でも、故障動作を検出し、回路動作を停止することが可能となるような半導体装置を提供する。

【解決手段】複数のフリップフロップを含む信号処理回路を有する半導体装置において、前記信号処理回路は、フリップフロップの入力信号を入力としパリティデータを生成する第1のパリティ生成回路と、前記第1のパリティ生成回路の出力をラッチするための、パリティ格納回路と、フリップフロップの出力信号を入力としパリティデータを生成する第2のパリティ生成回路と、前記パリティ格納回路の出力と第2のパリティ生成回路の出力とを比較し、不一致の場合に異常検出信号を出力するパリティ比較回路を備える。

(もっと読む)

入力インタフェース回路、集積回路装置および電子機器

【課題】信号入力端子に静電気ノイズが印加された場合に、そのノイズの内部回路への伝達を未然に、かつ確実に防止することができる入力インタフェース回路を提供すること。

【解決手段】ノイズを検出するノイズ検出回路(200)と、ノイズが検出されたときに第1のスイッチ回路(SW1)をオフしてノイズ伝達を遮断する機能をもつノイズキャンセラ(300)と、を設ける。第1のスイッチ回路(SW1)がオフしているときは、第2のスイッチ回路(SW2)がオンして、直前の電圧をラッチする。ノイズ検出回路200に含まれるノイズ検出用トランジスタは、Nウエルの電位を適応的に最適化することができるフローティングNウエルトランジスタによって構成される。

(もっと読む)

キャパシタ回路、キャリブレーション回路、コンパレータ及び電圧比較器

【課題】短時間で高精度のオフセット・キャリブレーションを行うことができるコンパレータを提供する。

【解決手段】オフセット・キャリブレーションを行う場合は、アナログ入力電圧Vip>アナログ入力電圧Vimとし、キャリブレーション指示信号φRESをHレベルとする。キャリブレーション回路49、50は、逆相比較判定信号ComがLレベルの間は、粗調によるオフセット・キャリブレーションを実行し、逆相比較判定信号Comの論理がHレベルに反転するまでを高速に行い、逆相比較判定信号ComがHレベルに反転すると、その後は、逆相比較判定信号Comの論理の反転に関係なく、微調によるオフセット・キャリブレーションを実行する。

(もっと読む)

クロック生成回路、クロック選択回路、及び半導体集積回路

【課題】 PLL回路から出力される異常波形のクロックにより他の機能回路が誤動作すること。

【解決手段】 クロック生成回路50は、クロックCL1に同期したクロックCL2を出力するPLL回路11と、クロックCL1又はクロックCL2を出力するセレクタ14と、PLL回路11からのクロックCL2で異常波形のパルスが検出されたとき、クロックCL2に代えてクロックCL1を出力させる切替信号をセレクタ14に出力する切替信号生成回路13と、切替信号に基づいてセレクタ14がクロックCL2からクロックCL1に出力クロックを切り替えた後、異常波形のパルスがセレクタ14に入力されるように、PLL回路11からのクロックCL2を遅延させる遅延回路12と、を備える。

(もっと読む)

電圧制御発振回路

【課題】動作が誤発振状態または準安定状態となったことを検出し、誤発振状態または準安定状態から抜け出して正常な発振状態にとすることができるVCOをを提供する。

【解決手段】本発明の電圧制御発振回路は、互いに逆相の差動のクロック信号が入力される差動遅延素子を縦続接続し、バイアス電圧によって差動遅延素子に流れる電流の量を制御することで、該差動のクロック信号の遅延量を制御する差動リングオシレータ型の電圧制御発振回路であり、いずれかの差動遅延素子の差動出力の出力電圧と、異常動作を検出する電圧に設定されたリファレンス電圧とを比較することにより異常発振を検出して検出信号を出力する位相検出部と、差動遅延素子毎に設けられ、検出信号が入力されると、差動出力対間の電位差を増幅するクロスカップル回路とを有している。

(もっと読む)

高ヒステリシス幅入力回路

【課題】従来のヒステリシス入力回路は等価的にP型MOSFETとN型MOSFETのインバータ回路のβ比を変えて、ロジックレベルのヒステリシスを作っていたが、この方式では電源電圧が低下するとヒステリシス幅が極端に小さくなった。また、電源電圧の広範囲の変動に対してヒステリシス幅を確保することは難しかった。また、ロジックレベルを形成するのにP型とN型MOSFETを用いるので形状比の設定にやや無理があり、また製造工程でのバラツキの影響を受けやすかった。

【解決手段】入力回路2個と正極の電源にP型、N型MOSFET、負極の電源にN型、P型MOSFETと、及び前状態を記憶するラッチ回路を設け、前状態により、前記各MOSFETをオン・オフすることにより、ヒステリシス特性を得る。電圧特性が異なるMOSFETを使い分けることにより、前述の課題が解消できた。

(もっと読む)

コンパレータ回路

【課題】 高速動作が可能で、かつオフセット電圧を高精度にキャンセルすること可能なコンパレータ回路を提供すること。

【解決手段】 増幅回路の出力を増幅して増幅回路の入力に帰還する第2の増幅回路を設け、コンパレータ回路が入力電圧をサンプルするときに、第2の増幅回路が帰還して増幅率を高くすることによって、オフセットをキャンセルするような構成とした。さらに、第2の増幅回路の増幅率より増幅回路の増幅率を低くし、コンパレータ回路が入力電圧をコンパレートするときに、第2の増幅回路の帰還と切り離すことによって、高速にコンパレート動作することが可能な構成とした。

(もっと読む)

半導体集積回路

【課題】オフセット電圧の補正精度の劣化を防ぐことにより、電圧比較精度の向上を図ることが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路101は、第1の入力電圧を第1のスイッチS0Pを介して受け、第2の入力電圧を第2のスイッチS0Nを介して受ける差動増幅回路A1と、第1のキャパシタC1Pを介して差動増幅回路A1の第1出力端子から受けた電圧および第2のキャパシタC1Nを介して差動増幅回路A1の第2出力端子から受けた電圧に基づいて第1の入力電圧および第2の入力電圧の比較結果を表わすデジタル信号を出力するラッチ回路U1と、第1のキャパシタC1Pの第2端子に結合される第1端子、および第2のキャパシタC1Nの第2端子に結合される第2端子を有する第3のキャパシタCZ1とを備える。

(もっと読む)

逓倍クロック信号出力回路

【課題】リングオシレータが出力するクロック信号の周波数がより高くなった場合でも、逓倍クロック信号の周波数を安定した状態で出力できる逓倍クロック信号出力回路を提供する。

【解決手段】DPLL回路1において、データラッチ回路52より出力され、11ビットのダウンカウンタ54dに本来セットすべきデータ値のサイズが12ビット以上になると、オーバーフロー防止回路3が前記データ値を11ビットデータに置換する。

(もっと読む)

発振装置および周波数検出装置

【課題】 中心周波数と周波数可変範囲を自在に設定できる高安定、高精度な電圧制御発振器を提供すること。

【解決手段】 第1の水晶発振器の第1の周波数成分と、第2の水晶発振器の第2の周波数成分とを加算器等で加算する等して、所望の中心周波数および所望の可変周波数範囲を作る。

(もっと読む)

第1段階処理部および第2段階処理部を含むデータサンプラ

【課題】電力消費を低減する方法を、特に低電圧および/または低電力のデータサンプラを提供する。

【解決手段】第1段階処理部および第2段階処理部を含み、上記第1段階処理部は、各差動信号を受信し、上記各差動信号に基づいて、第1出力信号における第1エッジレートと、第2出力信号における第2エッジレートとを供給するように構成されている。上記第2段階処理部は、上記第1出力信号と上記第2出力信号との間の差を増幅し、各再生出力信号を供給するように構成されている。上記第2段階処理部は、上記第1エッジレートおよび上記第2エッジレートに基づき、第1内部信号における第3エッジレートを供給し、かつ、第2内部信号における第4エッジレートを供給する。

(もっと読む)

クロック制御回路および半導体集積回路

【課題】クロックの立上りエッジおよび立下りエッジの両エッジをトリガとするフリップフロップに対してクロックを分配するクロックイネーブラを提供する。

【解決手段】排他的論理和ゲート230はクロックCKとラッチ270の不一致を生成する。ラッチ240は、イネーブル信号ENが論理L(無効)にある間に排他的論理和ゲート230からの入力を通し、イネーブル信号が論理H(有効)に遷移するとその直前の入力を保持する。選択器220はラッチ240の出力を選択信号として、クロックの正転信号または反転信号の何れか一方を選択する。ラッチ270は、イネーブル信号が論理Hにある間に選択器220からの入力を通し、イネーブル信号が論理Lに遷移するとその直前の入力を保持する。イネーブル信号が論理Lから論理Hに遷移すると、その停止していたレベルを再起点として出力端子Xからクロックが出力される。

(もっと読む)

半導体装置

【課題】 半導体装置における通常モードと特殊モードとの混載をコストの増大および特殊モードへの誤移行の危険性を回避して実現する。

【解決手段】 短パルス除去回路(11)は、外部制御信号(/CE)について第1所定時間より短いパルス幅の活性パルスおよび非活性パルスを除去して内部制御信号(/CEI)として出力する。短パルス検出回路(12)は、外部制御信号について第1所定時間より短いパルス幅の活性パルスおよび非活性パルスを検出する。内部回路(13)は、通常モードおよび特殊モードを有し、外部制御信号に代えて内部制御信号に応じて動作する。内部回路は、短パルス検出回路による活性パルスの検出に応答して通常モードから特殊モードに移行し、短パルス検出回路による非活性パルスの検出に応答して特殊モードから通常モードに移行する。

(もっと読む)

誤り検出装置

【課題】デジタル演算処理装置におけるフリップフロップの遅延エラーを、回路占有面積を増大させることなく確実に検出する。

【解決手段】特定のフリップフロップ(FF(i))の入力および出力を受ける誤り判定回路(EDK)を設ける。この特定のフリップフロップ前段のフリップフロップ(FF(i−1))をラッチ状態に設定して、直後のサイクルで、誤り判定回路において、特定フリップフロップの入出力データの論理レベルの一致/判定を行ない、判定結果指示信号(Err)を生成する。

(もっと読む)

AD変換器、無線受信機

【課題】消費電力の増大を招くことなく、受動素子の数を削減しチップ占有面積を小さくして低コスト化を図ることが可能なAD変換回路を提供すること。

【解決手段】n次元ベクトルを表すm(n<m<2n)個のアナログ信号のそれぞれを1ビット以上に量子化してm個並列の量子化信号を生成する量子化部と、このm個並列の量子化信号をそれぞれ復号してm個の復号アナログ信号を生成する復号部と、このm個のアナログ信号のそれぞれと上記m個の復号アナログ信号のそれぞれとの差のそれぞれを定数倍してm個の増幅残差信号を出力する残差増幅部と、を有する変換ステージを複数縦続接続して備えた変換部と、この変換部の変換ステージそれぞれにおけるm個並列の量子化信号を該変換ステージの縦続位置に応じた遅延量を考慮して並列位置ごとに合成し、m個並列のディジタル信号を生成する合成部とを具備する。

(もっと読む)

半導体集積回路

【課題】消費電流をより低減することが可能な増幅回路を備えた半導体集積回路を提供する。

【解決手段】制御信号VP1が「H」レベル、制御信号VP0が「L」レベルに時にはキャパシタCL1,CL2の電荷が完全に放電される。次に制御信号VP1が「L」レベル、制御信号VP0が「H」レベルになると、相補スイッチSW1,SW2はオンして、入力電圧VIP,VINに従ってPチャネルMOSトランジスタMP1,MP2を介して電流源3から定電流IBが流れ込み、キャパシタCL1,CL2に電荷が充電される。出力ノードN2,N1には、入力電圧VIP,VINの電圧値の大小に対応した値となり、差動増幅動作が実行される。すなわち、増幅動作のために負荷となるキャパシタCL1,CL2へ充電する動作以外で、電流源3からの定電流IBを消費しないため、低消費電流にて動作を実現できる。

(もっと読む)

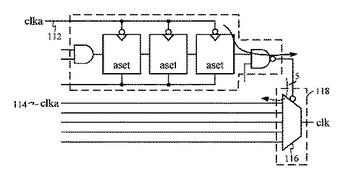

グリッチフリークロック信号マルチプレクサ回路および動作の方法

通信(例えばCDMA)システムにおける送信を処理することを含む(が、それに限定されない)デジタル信号プロセッサの設計及び利用の技術を開示する。クロックマルチプレクサを駆動する第1のクロック入力から第2のクロック入力への切換えにおいて起こるグリッチを低減する。クロックマルチプレクサは、第1のクロック入力を受信し、クロック出力を提供し、第1のクロック出力における低フェーズ入力レベルに応答してクロック出力における低フェーズ出力レベルを判定する。限定された期間、低フェーズ出力レベルは、第1のクロック入力信号のフェーズレベルに関わらず維持される。クロックマルチプレクサは、第2のクロック入力を受信し、第2のクロック入力信号における低フェーズ入力レベルを判定する。第2のクロック入力に応答してクロック出力を提供することへの切換えは、第2のクロック入力信号における低フェーズ入力レベルの間に起こる。その後、クロックマルチプレクサの出力は第2のクロック信号のフェーズレベルに従う。  (もっと読む)

(もっと読む)

101 - 120 / 163

[ Back to top ]