Fターム[5J039KK04]の内容

Fターム[5J039KK04]の下位に属するFターム

Fターム[5J039KK04]に分類される特許

121 - 140 / 163

時間計測回路

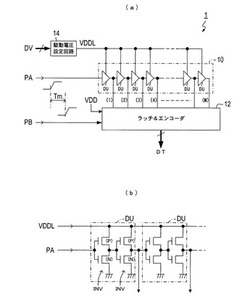

【課題】短い時間幅の高分解能な計測と長い時間幅の低分解能な計測とを、回路規模を大幅に増大させることなく、いずれも実現させることが可能な時間計測回路を提供する。

【解決手段】駆動電圧VDDLに応じた遅延時間で信号を遅延させる遅延ユニットDUをM(Mは正整数)段直列接続してなり、起動用パルスPAの入力により起動され、各遅延ユニットDUにてパルス信号を順次遅延させながら伝送するパルス遅延回路10と、計測用パルスPBが入力されると、パルス遅延回路10内でのパルス信号の位置を検出(ラッチ)し、その検出結果を、起動用パルスPAの入力から計測用パルスPBの入力までの時間Tm内にパルス信号が通過した遅延ユニットDUの段数を表す所定ビットのデジタルデータDTに変換して出力するラッチ&エンコーダ12と、電圧設定データDVに従った大きさの駆動電圧VDDLを発生させる駆動電圧設定回路14とを備える。

(もっと読む)

コンパレータ並びにA/D変換器

【課題】高速変換に適したフラッシュ型ADコンバータに使用することができるダイナミック・コンパレータを提供する。

【解決手段】ダイナミック・コンパレータは静止電流が全く流れず、低消費電力動作に最適な回路構成である。リニア領域で動作するNチャネル・トランジスタ1、2、3、4は抵抗値の大きさに応じたラッチ動作を行なうが、ラッチの時定数を微調整可能であるので、遅延時間のばらつき、素子(閾値電圧)のばらつきによるオフセットの影響によって劣化するビット・エラー・レートを改善することができる。

(もっと読む)

レベル判定回路

【課題】入力信号の論理レベルを正確に判定することが可能なレベル判定回路を提供する。

【解決手段】DRAM2の入力回路14は、入力信号VIの電位と参照電位VRDとの電位差を増幅する差動増幅回路20と、差動増幅回路20の出力信号の反転信号を出力するインバータ26と、前サイクルの出力信号を保持するラッチ回路29と、ラッチ回路29の出力信号VOPに従って参照電位VRDを切換えるための抵抗素子34,35とを含む。したがって、前サイクルの入力信号VIの論理レベルに応じて参照電位VRDを切換えるので、入力信号VIの論理レベルを正確に判定することができる。

(もっと読む)

半導体集積回路および半導体集積回路設計方法

【課題】設計期間を短縮化でき、半導体集積回路内の電源ノイズおよび製品のEMI問題を軽減できること。

【解決手段】階層化されたブロック間のインターフェースを、クロックとデータを同時に送るソースシンクロナスタイプにする。受信側ブロック22の受信器24にメソクロナスタイプの同期化回路を構成するクロック位相検出器27と、VDL28を備え、ブロック間インターフェースのデータをセットアップ/ホールド違反なしに受信し、受信側ブロック22の内部回路に転送する。

(もっと読む)

半導体記憶装置の同期モード検出回路及び方法

【課題】半導体記憶装置の同期モード検出回路及び方法に関するものであり、クロックが入力されれば同期モード信号をイネーブルにし、クロックが入力されなければ同期モードをディセーブルにすることによって、同期モードと非同期モードとを区分することができる半導体記憶装置の同期モード検出回路及び方法を提供する。

【解決手段】半導体記憶装置の同期モード検出回路は、有効アドレス信号とクロックを組み合わせて基準信号を生成する第1信号組合部と、前記基準信号をラッチする第1ラッチ部と、前記第1ラッチ部の出力信号と前記クロックを組み合わせて検出パルス信号を生成する第2信号組合部と、前記有効アドレス信号のイネーブル有無に応じて前記検出パルス信号の駆動を制御する制御部と、前記制御部の制御により前記検出パルス信号を駆動する駆動部と、前記駆動部で駆動された信号をラッチし、同期モード信号を出力するラッチ部とを含む。

(もっと読む)

信号増幅器

【課題】高速動作を可能とし、素子ばらつきに依存しない高信頼性動作を可能としている増幅器の提供。

【解決手段】一方の入力が他方の出力に接続され一方の出力が他方の入力に接続されることでフリップフロップを構成する第1及び第2のインバータを含み、インバータを構成する第1及び第2のトランジスタ対(MP1、MN1及びMP2、MN2)のうち、各一方のトランジスタ(MN1、MN2)の制御端子は、第1及び第2の容量(C1、C2)を介して第1及び第2のインバータの入力(1、2)にそれぞれ接続され、リセット時には、第1及び第2のインバータの互いの入力と出力(OUT、OUTB)を非接続とした状態で第1及び第2のインバータの入力には基準信号(VR)が共通に供給され、各一方のトランジスタはダイオード接続され、第1及び第2の容量には基準信号(VR)と各一方のトランジスタの制御端子との電圧差が蓄積される。

(もっと読む)

インタフェース回路および2値データ伝送方法

【課題】受信側で2値データの受信前にノイズマージンを拡大したり、発生するノイズの低減を図ることのできるインタフェース回路および2値データ伝送方法を実現する。

【解決手段】送信データ104は送信バッファ103から受信側に送信され、入力バッファ112を経て第3のフリップフロップ回路113に取り込まれる。検出部105は送信データ104の経時的な論理変化を検出して、基準電圧制御部114から出力される基準電圧調整信号124を変化させて2値化の適正化を図ると共に、遅延調整部106から出力されるクロック信号の位相を変化させてデータの取り込みを調整する。

(もっと読む)

位相調整回路および位相調整方法

【課題】センサ信号の伝達用搬送波の周波数が変動する場合においても、位相シフト量が変動することを防止することが可能である位相調整回路および位相調整方法を提供すること。

【解決手段】三角波変換回路2Gは、パルス列信号VPSINを三角波VCに変換する。三角波振幅制御回路3Gは、三角波VCの振幅値と振幅基準値VPAJとの比較を行い、両者の差分に応じた調整信号ASを三角波変換回路2Gに対して出力する。三角波変換回路2Gは、調整信号ASに応じて三角波VCの傾きを変化させることにより、三角波VCの振幅値を調整する。これによりフィードバックループが構成され、三角波VCの振幅値が振幅基準値VPAJに応じた一定値に維持される。位相シフト回路4は、元のパルス列信号VPSINに対して位相がシフトされたパルス列信号である移相パルス列信号VPSOUTを出力する。

(もっと読む)

位相比較回路およびそれを用いたPLL周波数シンセサイザ

【課題】高速に周波数切り換えが可能であり、且つ小型でスプリアスを低減することが可能な位相比較回路を提供する。

【解決手段】本発明の一実施形態に係る位相比較回路は、制御回路からの制御信号に基づいて、クロックを分数分周した分数分周信号を生成する分数分周器と、分数分周信号を整数分周した第1の整数分周信号を生成する第1の整数分周器と、基準クロックを整数分周した第2の整数分周信号を生成する第2の整数分周器と、切換信号に基づいて、分数分周信号と第1の整数分周信号とのいずれか一方を選択的に出力する第1の選択回路と、制御回路からの切換信号に基づいて、基準クロックと第2の整数分周信号とのいずれか一方を選択的に出力する第2の選択回路と、第1の選択回路からの出力信号と第2の選択回路からの出力信号との周波数差および位相差を表す比較信号を生成する位相比較器とを備えている。

(もっと読む)

半導体装置

【課題】USBクロックやシステムクロック等を使用する半導体装置において、汎用性を向上することができる技術を提供する。

【解決手段】複数のクロック(入力クロック1、入力クロック2)を入力とし、その複数のクロックのそれぞれを入力クロック1カウンタ110a及び入力クロック2カウンタ110bで一定期間計測し、その計測結果を用いて複数のクロックのそれぞれの周波数を検出し、その検出結果に基づいて、クロックソース選択回路107bで複数のクロックのいずれかを選択し、PLL回路2(108b)で逓倍し、分周回路2(109b)で分周し、USBクロックを生成する。

(もっと読む)

レシーバ

【課題】信号伝送を行う回路において、大きなコモンモード電圧の除去を図る。

【解決手段】複数の信号線SL0,SL1と、該信号線に接続された容量C11,C12および該容量の接続を制御するスイッチSW11〜SW16を有する容量ネットワークと、を備えたレシーバであって、前記複数の信号線が持つコモンモード電圧の成分を含む容量ノードの少なくとも1つを特定の電圧値Vrefに保たれたノードに接続して該信号線が持つコモンモード電圧を除去するコモンモード電圧除去手段を備えるように構成する。

(もっと読む)

クロック発生回路

【課題】基準クロックと分周クロックとの伝送路におけるチップ内ばらつきによるスキューを抑制し、タイミング収束性を改善したクロック発生回路を実現する。

【解決手段】クロック発生回路は、第1の回路10と、第2の回路20Aと、第3の回路50Aとを備えている。第1の回路10は、第1のクロック信号s10を生成する。第2の回路20Aは、前記第1のクロック信号s10を分周して、第2のクロック信号s20を生成する。第3の回路50Aは、前記第1及び第2のクロック信号s10,s20から、前記第2のクロック信号s20の周期を有し、かつ第1の論理レベルから第2の論理レベルへの変化のタイミングが前記第1のクロック信号s10の当該タイミングと同じである第3のクロック信号s50を生成する。

(もっと読む)

半導体集積回路のクロックツリー形成方法およびプログラム。

【課題】製造ばらつきの影響の小さいクロックツリーを生成するクロックツリー形成方法を提供する。

【解決手段】クロックツリー回路のFF対のフリップフロップ間の経路に対して、クロックスキューがない状態でタイミング解析を行い、ホールドエラーが発生する基準値に対しての余裕度としてホールドスラック値を求めるホールドスラック計算処理22と、クロックツリー回路の分岐点となるバッファからFF対ごとのフリップフロップ入力間の経路に対して、経路の遅延の最小値、最大値を計算し記憶するバッファ遅延計算処理23と、経路ごとにホールドスラック値と最大値から最小値を減算した結果を比較して、ホールドスラック値より大きいと判断された場合はFF対をグループ化するFF対集合操作処理24と、同一グループのFF対の経路ごとに、FF対が同一のバッファで駆動するようにバッファを挿入するバッファ挿入処理25を行う。

(もっと読む)

電子装置を調整または設定するための方法および装置

【課題】外部入力信号用の少なくとも1つの入力と、入力信号用の少なくとも1つの出力とを有し、出力信号の値または状態が入力信号の値または状態の関数である、電子装置1を調整または設定するための方法および装置を提供する。

【解決手段】調整信号の値のためのメモリ回路9は電子装置を調整するための入力に接続される。回路11は前記メモリ回路内に保存された前記調整値を増加/減少させる。切換回路12は電子装置の前記入力を所定の状態に切換え、電子装置の前記出力を、前記増加/減少回路を介して、前記メモリ回路に接続する。前記増加/減少回路11は前記信号の値を前記所定の状態に調整するように構成され、前記出力信号の前記値または状態は、所定の値または所定の状態に近づくまたは到達する。

(もっと読む)

二値化回路及び二値化方法

【課題】入力信号を二値化するための二値化回路及び二値化方法に関し、ノイズに対して適切な二値化が行なえる二値化回路及び二値化方法を提供することを目的とする。

【解決手段】本発明は、入力信号を二値化する二値化回路であって、入力信号を微分し、全波整流した波形に整形する波形整形回路(111、112)と、波形整形回路(111、112)で整形された信号の最大値をホールドするホールド回路(113)と、ホールド回路(113)にホールドされた最大値に応じて閾値を生成する閾値生成回路(114)と、波形整形回路(111、112)で整形された信号と閾値生成回路(114)で生成された閾値とを比較する比較回路(115)と、比較回路(115)の比較結果に応じて入力信号を二値化した信号を生成する出力回路(116)とを有することを特徴とする。

(もっと読む)

シングルイベント耐性のラッチ回路及びフリップフロップ回路

【課題】シングルイベント現象が発生しにくく、シングルイベントトランジェント(SET)現象が発生してもそれの回路への影響を排除することができるラッチ回路及びフリップフロップ回路を提供する。

【解決手段】形成される強電界領域を狭くするために、ラッチ回路をデュアルポートインバータと、トランスミッションゲートを含まないデュアルポートクロックドインバータとから構成する。SET現象の影響をクロックに遅延時間を設けることにより排除するが、その遅延時間によってホールド時間が増加させられることを防止するために、一方の記憶ノードへは、その記憶ノード及び全体のラッチモードからスルーモードへの移行が遅延させられるような前縁エッジ遅延クロックが入力される。

(もっと読む)

ノイズフィルタ回路

【課題】 遅延時間以上の幅のノイズパルスが入力されたために完全にノイズが除去しきれなかった場合においても、ノイズパルスを後段へと通過させず、正規の信号パルスのみをクロック信号に同期させて出力させることができるノイズ除去回路を提供する。

【解決手段】 前記課題を解決するために、本発明によるノイズフィルタ回路は、遅延回路を用いたノイズ除去回路の後段にフリップフロップを追加する構成とし、そのフリップフロップへ入力されるクロック信号をノイズ除去回路とは別時間遅延させた正規の信号パルスとし、これに同期させる構成とした。

(もっと読む)

パルス整形回路

【課題】 伝搬ノイズや外来ノイズによる異常パルスがいかなるタイミングで発生しても、立ち上がりおよび立ち下がりを時間差無く検出し、波形を整形することを目的としている。

【解決手段】 入力信号の立ち上がり部分のマスク信号を発生する回路と、前記入力信号の立ち下がり部分のマスク信号を発生する回路と、前記入力信号の最初の立ち上がりをラッチし前記立ち下がり部分のマスク信号によりリセットされる回路と、前記入力信号の最初の立ち下がりをラッチし前期立ち上がり部分のマスク信号によりリセットされる回路を有し、前記立ち上がり部分のマスク信号と前記立ち下がり部分のマスク信号のマスク幅は整形するパルス幅と同等に設定できるようにしたパルス整形回路。

(もっと読む)

周波数逓倍装置

【課題】出力信号の精度を維持することが可能な高精度の周波数逓倍装置を低コストに提供する。

【解決手段】基準信号PREFの1周期分の時間内に生成された出力クロックRCKをカウント(計時)し、そのカウント値を表すデジタルデータDL1〜DL12をラッチ(確定)し、そのデジタルデータをクリアする、という動作を基準信号PREFの2周期毎に繰り返す結果、基準信号PREFの2周期毎にラッチされたデジタルデータDL1〜DL12である周波数制御データCD1〜CD12が新たに生成される。この新たに生成される周波数制御データ[2]は、基準信号PREFの2周期前に生成された周波数制御データ[1]を補正したものといえる。そのため、出力クロックRCKのカウント値が周波数制御データに反映され、新たな周波数制御データ[2]が生成されるまでに要する時間である補正遅延時間tは基準信号PREFの2周期分の時間になる。

(もっと読む)

共鳴トンネルダイオードを有するコンパレータ

【解決手段】 コンパレータは、コンパレータのラッチ素子の抵抗(R301、R302)に直列な2つの共鳴トンネルダイオード(RTD、RTD301、RTD302)を用いる。2つのRTDダイオード(RTD301、RTD302)を抵抗(R301、R302)と直列に挿入することによって、第1、第2RTDダイオードの負抵抗が、抵抗およびラッチの実効的なRD時定数を減じて、コンパレータのラッチモードの間、別の設計によって実現される場合よりも高速の再生につながる。 (もっと読む)

121 - 140 / 163

[ Back to top ]