Fターム[5J039KK04]の内容

Fターム[5J039KK04]の下位に属するFターム

Fターム[5J039KK04]に分類される特許

141 - 160 / 163

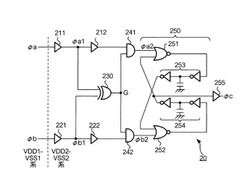

ノイズ除去回路

【課題】 電源系の異なる2つの回路間で信号の授受を行う装置において外乱により発生するノイズが後段の回路に取り込まれないように効果的に除去することができるノイズ除去回路を提供する。

【解決手段】 ANDゲート241および242は、ゲート信号Gに応じて、前段の回路から出力される相互に逆相関係のタイミング信号を通過させ、または遮断する。XORゲート230は、タイミング信号φa1およびφb1のレベルが一致していないとき、これらを通過させるゲート信号Gを出力し、レベルが一致しているとき、これらを遮断させるゲート信号Gを出力する。双安定回路250は、ANDゲート241および242を通過したタイミング信号φa2およびφb2を保持し、保持状態を示すタイミング信号φcを後段の回路に出力する。

(もっと読む)

クロック回路のための方法及びシステム

【課題】半導体に与えるクロック信号の一部の周波数を低減出来る回路を提供すること。

【解決手段】1組の時間インターバルを有するカウンタ信号122を出力するように動作するカウンタ回路120と、出力クロック信号114を発生するように動作するゲート回路110とを具備し、前記出力クロック信号114は、第1の動作モードにおいては、入力クロック信号112と実質的に同一であり、第2の動作モードにおいては、1組の時間インターバルのうちの少なくとも1つの時間インターバル中に、前記入力クロック信号112に実質的に等しくされている。

(もっと読む)

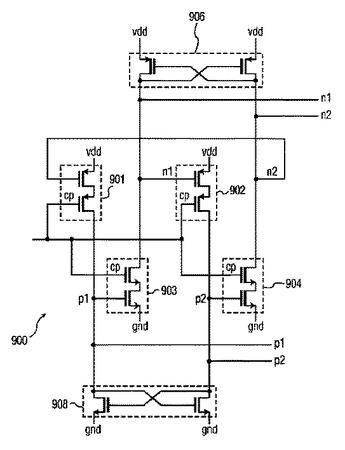

多相分周器

本発明の多相分周器はリングに接続された複数のダイナミックインバータを具え、リング全周上の中間ノードが交差結合ラッチで安定化されている。クロック入力パルスが各ダイナミックインバータの出力をイネーブルし、対応する状態変化をクロスラッチに生じさせる。多相出力がすべてのラッチに並列に与えられる。  (もっと読む)

(もっと読む)

容量結合を利用したCMOSの時系列型AD変換回路及びDA変換回路

【課題】容量結合回路を利用して少ない素子数で論理回路,AD変換回路等を提供する。

【解決手段】アナログ入力が与えられる入力端子と、2値の出力が与えられるN(Nは複数)ビットの出力端子とを有するアナログ・デジタル変換回路において、一方の電極が入力端子に接続される入力容量と、入力容量の他方の電極が入力される第一のインバータと、該第一のインバータに接続される第二のインバータとを有する単位回路が、N個並列に設けられ、その単位回路の第二のインバータの出力がそれぞれの出力端子に与えられ、更に、各単位回路に対応する出力の反転出力が、それぞれ下位ビットに対応する単位回路の前記第一のインバータの入力に帰還容量を介して帰還され、最上位ビットからM(Mは整数)番目の単位回路の反転出力に対応する前記帰還容量の容量値は、帰還される単位回路の入力容量の1/2M 倍であることを特徴とするアナログ・デジタル変換回路。

(もっと読む)

回路のジッタを計算する方法、論理装置及びシステム並びに回路のクロックツリーを合成する方法、論理装置及びシステム

【課題】チップレベルの設計に関する問題に対処し、クロストークカップリングが存在する場合でも正確な経路遅延を計算すること。

【解決手段】一実施例でのクロックツリーにてジッタを計算する方法は、クロックツリーを複数のステージに分割し、クロックツリーに関連する回路の少なくとも一部分のモデルに従って、1以上のステージのジッタを算出する。モデルは回路のジッタのソース各々の表現を含む。本方法は、クロックツリー中の経路又は経路対に関するジッタを計算するため、クロックツリー中の経路又は経路対の各ステージのジッタを互いに統計的に合成するステップを含む。一実施例では、ジッタを効率的に計算し且つクロックスキューゼロを達成するため、モデルは回路の対称的なクロックツリーを合成し、そのツリーでは区六浮くツリーのルートからクロックツリーのシンクに至る全てのパス中の関連するステージは、近似的に電気的に互いに等価な性質を示す。

(もっと読む)

容量結合を利用したCMOSのAD変換回路

【課題】容量結合回路を利用して少ない素子数で論理回路,AD変換回路等を提供する。

【解決手段】アナログ入力が与えられる入力端子と、2値の出力が与えられるN(Nは複数)ビットの出力端子とを有するアナログ・デジタル変換回路において、一方の電極が入力端子に接続される入力容量と、入力容量の他方の電極が入力される第一のインバータと、該第一のインバータに接続される第二のインバータとを有する単位回路が、N個並列に設けられ、その単位回路の第二のインバータの出力がそれぞれの出力端子に与えられ、更に、各単位回路に対応する出力の反転出力が、それぞれ下位ビットに対応する単位回路の前記第一のインバータの入力に帰還容量を介して帰還され、最上位ビットからM(Mは整数)番目の単位回路の反転出力に対応する前記帰還容量の容量値は、帰還される単位回路の入力容量の1/2M 倍であることを特徴とするアナログ・デジタル変換回路。

(もっと読む)

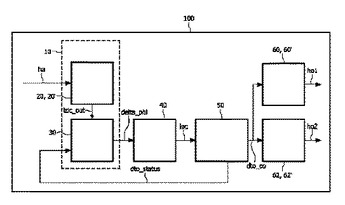

位相ロックループ回路装置及びこれを利用したクロック信号発生方法

回路装置(100)、特にサブクロックまたはサブピクセルの正確な位相測定及び位相発生用の位相ロックループ、並びにこれに対応する方法を、クロック乗算器位相ロックループを時間−ディジタル変換器の後方に設けず、アナログ遅延線も信号除算器ユニットも、ディジタルランプ発振器または離散時間発振器とディジタル−時間変換器との間に設けず、ディジタル環境におけるノイズ及び接地バウンスの影響を受け易いアナログ回路がより少ない方法でさらに発展させるために、少なくとも1つの位相測定ユニット(10);少なくとも1つの位相検出器ユニット(30)の少なくとも1つの出力信号(delta_phi)を供給される少なくとも1つのループフィルタユニット(40, 40’);ループフィルタユニット(40, 40’)少なくとも1つの出力信号、特に少なくとも1つの増分(inc)を供給される少なくとも1つのディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)を設け、ディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)の少なくとも1つのレジスタユニット(54, 54’)の状態信号(dto_status)は位相検出器ユニット(30)に入力信号として供給され、さらに、少なくとも1つのディジタルランプ発振器ユニットまたは離散時間発振器ユニット(50, 50’)の少なくとも1つの出力信号(dto_co)を供給されて少なくとも1つの出力信号(ho1, ho2)発生する少なくとも1つのディジタル−時間変換器ユニット(60, 62, 60’, 62’)を設けることを提案する。  (もっと読む)

(もっと読む)

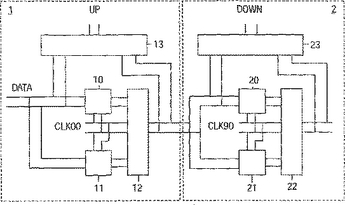

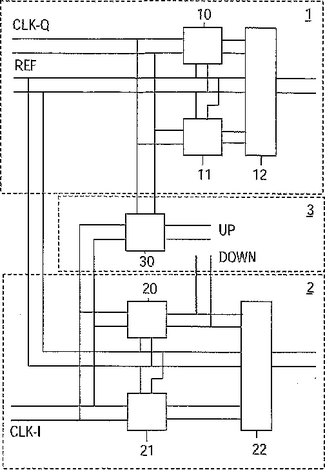

多重送信用ラッチ付き線形位相検出器

線形位相検出器は、クロック抽出器およびデータ再生器内で使用するために、第1および第2クロック信号(CLKOO,CLK90)を受信して第1および第2制御信号(UP,DOWN)を生成する回路(1,2)を備え、これらの回路は、入力および出力との間の長い経路の長さと多くの動作により大きな遅延を有する(洞察)。これらは、それぞれの回路(1,2)に2つの並列のラッチ(10,11,20,21)と、これらのラッチの出力信号を多重送信するマルチプレクサ(12,22)を与えることにより、より速くさせることが可能である(基本概念)。データ信号は第1回路(1)に供給され、第1回路出力信号は第2回路(2)に供給される。それぞれがまた2つのラッチとマルチプレクサを備える第3および第4回路(3,4)を導入することにより、高速線形位相検出器は、多数のトランジスタから独立した、データ信号におけるゲインを有するように構成されており、これは長所である。それぞれの回路(1,2,3,4)の論理回路(13,23)は、加算器/減算器(5)に結合される。  (もっと読む)

(もっと読む)

高速線形位相検出器

第1および第2(位相)制御信号(UP、DOWN)を生成するために基準信号(REF)および第1および第2クロック信号(CLK−Q、CLK−I)を受信する回路を備える乗算器回路、復調器および受信機用の線形位相検出器は、長い経路長および入力と出力との間の多くの動作のために大きな遅延を有する(洞察)。各回路(1、2)に2個の並列ラッチ(10、11、20、21)およびラッチ出力信号を多重化するための多重化装置(12、22)を備えることによって、線形位相検出器をより高速にすることができる(基本概念)。前記多重化装置は、周波数検出器に供給されるべき(周波数制御)信号を生成し、第3回路(3)が前記(位相)制御信号(UP、DOWN)のうちの少なくとも1つを生成している。前記第3回路(3)は、前記第1(位相)制御信号(UP)を生成するラッチ(30)を備え、第2回路(2)のラッチの1つ(20)が第2(位相)制御信号(DOWN)を生成している。または、前記第3回路(3)は、4個のEXORゲート(31〜34)を備える論理回路(31〜34)を備える。第5EXORゲート(35)が、第3回路(3)を平衡させるために使用される。  (もっと読む)

(もっと読む)

コンパレータ回路

【課題】応答速度の速いコンパレータ回路を提供する。

【解決手段】 差動増幅回路とラッチ回路からなり、等化(イコライズ)トランジスタを有するコンパレータ回路において、イコライズトランジスタに入力される制御信号のHighレベルの電位をクロック信号のHighレベルの電位よりも低下したものとする。増幅・ラッチ停止時から増幅・ラッチ活性時に移行するときにイコライズトランジスタから発生するスイッチングノイズが低減されるので、出力端子からHigh/Low信号がすばやく出力される。

(もっと読む)

デューティ測定回路及びデューティ測定方法

【課題】 外部信号を用いずにクロック信号のデューティを正確に測定する。

【解決手段】 半導体装置20には、第1の回路ブロック1、第2の回路ブロック2、PLL部3、第1のデューティ測定回路4a及び4b、第2のデューティ測定回路5a及び5b、セレクタ6、及びI/Oレジスタ7が設けられている。第1の回路ブロック1に隣接して設けられた第1のデューティ測定回路4aは、第1の回路ブロック1に入力されるPLL信号の“High”レベル期間(TH)を測定する。第1の回路ブロック1に隣接して設けられた第2のデューティ測定回路5aは、第1の回路ブロック1に入力されるPLL信号の“Low”レベル期間(TL)を測定する。測定されたPLL信号の“High”レベル期間(TH)及びPLL信号の“Low”レベル期間(TL)から、第1の回路ブロック1に入力されるPLL信号のデューティを高精度に算出できる。

(もっと読む)

半導体装置の遅延調節回路、及び遅延調節方法

【課題】動作条件の変化による遅延時間を検出し、この遅延時間を一定範囲内に入るように調節可能な遅延調節回路が開示される。

【解決手段】遅延調節回路は、遅延検出回路、第1パルス発生器、カウンタ制御回路、及びnビットカウンタを備える。遅延検出回路は、出力信号に応答して入力信号を第1時間遅延させ、入力信号と遅延した入力信号とを互いに比較し、第1信号を発生させる。第1パルス発生器は、入力信号に応答して第2信号を発生させる。カウンタ制御回路は、第1信号と第2信号とに応答してカウントアップ信号とカウントダウン信号とを発生させる。nビットカウンタは、カウントアップ信号とカウントダウン信号に応答して第1時間を2n(nは自然数)区間に分けるためのデジタル出力信号を発生させる。従って、遅延調節回路は、半導体製造工程、温度、電圧などの条件が変化しても遅延時間を一定範囲内に入るように調節することができる。

(もっと読む)

A/D変換器

【課題】サンプリングホールド回路のサンプリングタイミングとのスキュー差が極めて少ない比較器を有してなるA/D変換器を提供する。

【解決手段】サンプルホールド回路のサンプルホールドに用いられるスイッチ素子と同等の機能を有する2つのスイッチ素子11,12がA/D変換器を構成する比較器において用いられており、サンプルホールドに用いられるスイッチ素子と同一のクロック信号で駆動されることで、比較器のラッチングタイミングとサンプリングタイミングとのスキュー差を極めて小さくでき、信頼性の高いA/D変換器が提供される。

(もっと読む)

絶縁型電圧検出回路

【課題】回路構成が単純で、廉価な部品のみにより構成される、簡易的な絶縁型電圧検出回路を提供する。

【解決手段】レジスタ1に設定されたデータに比例したパルス幅の第1のPWM信号を出力するパルス幅変調回路2と、その出力を絶縁して第2のPWM信号として出力する第1の絶縁手段3と、第2のPWM信号をアナログ電圧信号aに変換する変換回路4と、アナログ電圧信号aと検出対象であるアナログ電圧信号bを比較し、2つの極性をもつ比較信号を出力する比較器5と、その比較信号を絶縁して2つの極性を有する第2の比較信号cとして出力する第2の絶縁手段6とを備え、第2の絶縁手段6から出力される第2の比較信号cの結果を所定の周期で検出し、アナログ電圧信号aと検出対象であるアナログ電圧信号bが等しくなるように、レジスタ1に設定するデータをCPU7により増減させるようにした絶縁型電圧検出回路。

(もっと読む)

画像転送調整アダプタ

【課題】画像転送インターフェースにおける画像データとクロック信号との同期を実用状態と同じ条件で簡単に評価できると共に、表示装置側の位相調整にも利用可能な画像転送調整アダプタを提供することを目的とする。

【解決手段】ビデオコントローラと表示装置との間を接続するコネクタにクロック信号を遅延させる遅延器を設け、遅延器の遅延量を外部から可変可能にすることで、画像データとクロック信号との位相調整を行い、表示装置側で受信される画像データ信号のセットアップ時間及びホールド時間を確保出来るようにした。

(もっと読む)

半導体集積回路装置のタイミング制御回路

【課題】半導体集積回路装置の制御対象回路に与える制御信号が製造プロセスや電源電圧、周囲温度などの変動によって変動するのを抑制すること。

【解決手段】外部クロックextCLKに基づき基準信号actCLKを生成する中央制御回路2側に、遅延値を制御するディジタル値DCTRL[n:0]からなる遅延制御信号を生成する遅延制御回路6を設け、中央制御回路2からローカル制御回路3に対して基準信号と遅延制御信号とを供給する。ローカル制御回路3に設けた可変遅延回路7は、遅延値がディジタル値で制御される単位遅延回路を多段に接続して構成され、メモリセルアレイ1に供給する各種の制御信号を、前記基準信号を前記遅延制御信号のディジタル値が示す所定の遅延値だけ遅延したタイミングで生成する。

(もっと読む)

電圧比較回路

【課題】

消費電力がより少ない電圧比較回路を提供する。

【解決手段】

入力端子IN1がゲートに接続されるFETQ1と、入力端子IN2がゲートに接続されるFETQ2と、双安定回路と、AND回路Gと、FETQ11を備える。双安定回路は、比較のストローブ信号となるパルス信号φが供給され、パルス信号φがローレベルにある時に出力端子OUT1、OUT2の論理値がハイレベルとなり、AND回路Gの出力がハイとなってFETQ11をオンとする。パルス信号φがローレベルからハイレベルに変化した時に、入力電圧の比較がなされ、FETQ1、Q2のドレイン電流の大小関係に対応して出力端子OUT1、OUT2の一方がローレベルに変化してAND回路Gの出力がローレベルとなってFETQ11をオフとする。比較動作を行う短い期間にのみFETQ1、Q2のソース電流が流れるので低消費電力化が実現される。

(もっと読む)

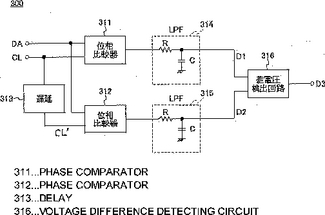

位相比較利得検出回路、誤同期検出回路及びPLL回路

PLLの位相比較利得検出回路において、データ信号DAとクロック信号CLとの間の位相を比較すると共に、データ信号DAとクロック信号CLを所定の遅延量だけ遅延したクロック信号CL’との間の位相を比較し、それぞれの位相比較結果どうしの差と上記所定の遅延量とに基づいて位相比較利得を検出する位相比較利得検出回路。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】 エッジトリガで動作するレジスタ回路に簡単なハードウェアを付加してノイズ等の影響によるレジスタへの誤書き込み防止をはかる。

【解決手段】 書き込み制御回路が、レジスタ回路1に対する新しいデータの書き込み時、レジスタ回路1に記憶されたデータを読み出し、先にラッチ回路3に保持されたデータと一致検出回路2で一致が検出されたときのみその書き込みを許可して、狭パルス状のノイズに対するプロテクトを行う。

(もっと読む)

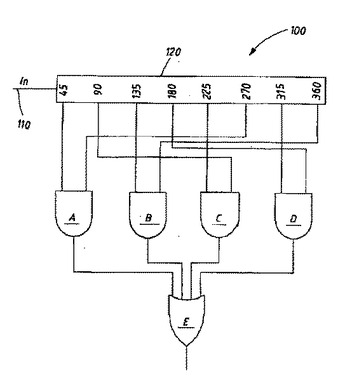

周波数逓倍器

本発明は、信号用の入力手段と、ポイント間に所定の位相差をもつ複数のポイントで信号にアクセスするための手段とを備える、パルス列である信号のパルス周波数を逓倍するためのデバイスを開示する。このデバイスは、アクセスされた信号ペアを結合するための第1のレベルにある手段を更に備え、すべての結合されるペア内で同一の位相距離があり、各第1のレベルの結合手段からの出力はパルス列である。このデバイスは、第1のレベルからのパルス列を結合するための第2のレベルにある結合手段を更に備え、第1のレベルにある結合手段は、出力パルス列中のパルスが、結合されるアクセスされた信号ペア中の第1の信号の立上り側腹部に常に一致する立上り側腹部と、前記ペア中の第2の信号の立下り側腹部に常に一致する立下り側腹部とを有する手段である。  (もっと読む)

(もっと読む)

141 - 160 / 163

[ Back to top ]