Fターム[5J039KK04]の内容

Fターム[5J039KK04]の下位に属するFターム

Fターム[5J039KK04]に分類される特許

1 - 20 / 163

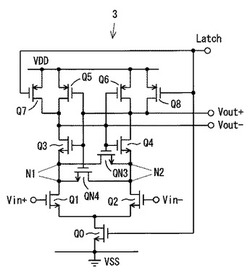

ラッチト・コンパレータ

【課題】差動回路の特性を損なうことなく、高速に信頼性の高いラッチ出力を行うラッチト・コンパレータを提供する。

【解決手段】ラッチト・コンパレータ(1)は、ドレイン・ソース間が、第1の電流経路上の第1のMOSトランジスタ(Q1)と第3のMOSトランジスタ(Q3)との間の第1のノード(N1)と、第2の電流経路上の第2のMOSトランジスタ(Q2)と第5のMOSトランジスタ(Q4)との間の第2のノード(N2)との間に接続されているとともに、ゲートが第1のCMOSインバータの出力に接続された、第7のMOSトランジスタ(QN3)と、ドレイン・ソース間が第1のノード(N1)と第2のノード(N2)との間に接続されているとともに、ゲートが第2のCMOSインバータの出力に接続された、第8のMOSトランジスタ(QN4)と、の少なくとも一方をさらに備えている。

(もっと読む)

半導体装置

【課題】不揮発性メモリを備えた半導体装置において、高速動作の場合と低速動作の場合とに切替え可能にするとともに、低速動作時の消費電力を従来よりも削減する。

【解決手段】半導体装置1において、クロック生成回路40は、高周波モード時には低周波モード時よりも周波数の高いクロックを生成する。中央処理装置20は、データバス11を介して不揮発性メモリ10から読み出された読出データを取得する。クロック遅延部50Aは、縦続接続された複数段のバッファ55を介した第1の経路51と複数段のバッファ55を迂回した第2の経路52とを含む。クロック遅延部50Aは、高周波モード時には、クロック生成回路40からのクロックを第1の経路51を介して中央処理装置20に供給し、低周波モード時には、クロック生成回路40からのクロックを第2の経路52を介して中央処理装置20に供給する。

(もっと読む)

コンパレータ回路

【課題】コンパレータ回路において、従来技術に比較して高速で消費電力を低下させる。

【解決手段】入力される2つの入力電圧に応じて、第1及び第2のMOSトランジスタからなる入力差動対のいずれか1つのMOSトランジスタにおいて、当該1つのMOSトランジスタとスイッチトランジスタとを含むループにより適応バイアス電流を発生する入力差動対及び適応バイアス電流発生回路と、上記適応バイアス電流に対応する電流を検出してラッチ論理を変化させた後、上記スイッチトランジスタをオンからオフに切り換えることにより上記適応バイアス電流を遮断するラッチ回路とを備える。

(もっと読む)

比較回路及びアナログデジタル変換回路

【課題】動作電圧に対して入力電圧範囲を拡大し、低消費電力化を図ること。

【解決手段】比較回路10の電圧制御部12は、キャパシタC11の第1端子に、クロック信号CKに応答して高電位電圧AVDと低電位電圧(グランドGND)を供給する。キャパシタC11の第2端子に接続されたトランジスタT23は、反転クロック信号XCKに応答してオンオフする。入力トランジスタT11,T12のしきい値電圧と等しく設定されたトランジスタT23は、グランドGNDの電圧とノードN21の電圧に応じて反転状態となり、比較部11に供給する制御電圧VCM(ノードN21の電圧)をグランドGNDからトランジスタT23のしきい値電圧低い電圧に安定させる。

(もっと読む)

データ復元回路及びデータ復元方法

【課題】孤立パルスを確実に検出してデータ判定を実行できるデータ復元回路を提供する。

【解決手段】データ復元回路は、デジタルデータの列のうち2つの連続するデジタルデータを用いて、内挿により第1のデータ切り替わり点の位置を算出すると共に、外挿により第2のデータ切り替わり点の位置を算出する位相検出器と、第1のデータ切り替わり点の平均位置と瞬時位置とに基づいてデジタルデータの列からデータ判定値の列を抽出するデータ判定部と、2つの連続するデジタルデータに挟まれた時間軸上の区間の内に、直前の2つの連続するデジタルデータの外挿直線及び直後の2つの連続するデジタルデータの外挿直線からそれぞれ求めた2つの第2のデータ切り替わり点が位置し且つ2つの外挿直線の傾きの符号が互いに異なる場合、データ判定値の列の当該区間に対応するデータ判定値を、外挿により推定されるデータ値で置き換えるデータ選択部を含むことを特徴とする。

(もっと読む)

CDR回路

【課題】前段の光受信装置のスケルチ機能の有無に関係なく汎用的に使用可能なCDR回路を提供する。

【解決手段】CDR回路は、入力データ1に同期した再生クロック2を出力するG−VCO14と、入力データ1の識別再生を再生クロック2に基づいて行うフリップフロップ回路12と、G−VCO14と同一周波数のクロックを出力するサブVCO15と、再生クロック2とサブVCO15の出力クロック4のいずれかを選択する選択回路17と、選択回路17の出力クロック8と参照クロック6とを周波数比較しその周波数差に応じた周波数制御信号5を出力する周波数比較器16とを備える。選択回路17は、少なくとも入力データ1が無信号である期間においてサブVCO15の出力クロック4を選択し、残りの期間において再生クロック2を選択する。

(もっと読む)

半導体集積回路

【課題】クロック信号の立ち下がりエッジで発生する消費電力を低減することができる半導体集積回路を提供することである。

【解決手段】実施の形態の半導体集積回路は、クロック信号生成部と、クロック波形整形部と、複数の機能ブロックとを有する。クロック信号生成部は、所定の周波数のクロック信号を生成する。クロック波形整形部は、クロック信号生成部で生成されたクロック信号と立ち上がりエッジの位相が同一で、かつ立ち下がりエッジの位相が異なる複数のクロック信号を生成する。複数の機能ブロックは、それぞれがクロック波形整形部で生成された複数のクロック信号のいずれかで動作する複数のフリップフロップを有する。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、クロックツリーにおける消費電流を削減しながら、同期回路間の同期動作を行うことが難しかった。

【解決手段】本発明にかかる半導体装置は、動作クロック信号CLKに応じて第1のクロック信号を出力し、第1の応答時間で第1のクロック信号のエッジを変化させる第1のクロックバッファ(VCB11〜VCB14のうちの一つ)と、動作クロック信号CLKに応じて第2のクロック信号を出力し、第2の応答時間で第2のクロック信号のエッジを変化させる第2のクロックバッファ(VCB11〜VCB14のうちの他の一つ)と、第1のクロック信号に同期して動作し、第1の電圧レベルを閾値電圧とする第1の論理回路と、第2のクロック信号に同期して動作し、第2の電圧レベルを閾値電圧とする第2の論理回路と、を有し、第1、第2の論理回路は、動作クロック信号に応じて一のタイミングで動作する。

(もっと読む)

クロックバッファ回路及びこれを用いたクロック分配回路

【課題】小さな回路規模により広帯域のクロック信号に対応できるクロックバッファ回路を提供すること。

【解決手段】本発明の一態様であるクロックバッファ回路100は、ドライバ部11及びLCタンク部21を有する。ドライバ部11は、クロック入力IN及びINBからの入力クロック信号の少なくとも正転出力を、それぞれクロック出力OUT及びOUTBへ出力する。LCタンク部は、ドライバ部11とクロック出力OUT及びOUTBとの間に配置される。ドライバ部11は、入力クロック信号の周波数に対応した制御信号に応じて、ドライバ部11の入力と出力とを短絡させるスイッチSW1及びSW2を有する。

(もっと読む)

周波数判定回路および半導体装置

【課題】長短のパルス幅が混在するデータ信号の周波数を判定することができる技術を提供する。

【解決手段】複数の周波数の異なるデータ信号から周波数を判定する周波数判定回路201において、複数の周波数の異なるデータ信号を取り込み、所定のパルス幅よりも短いパルス幅の信号のカウント数に基づいて周波数を判定する回路を有する。例えば、所定のパルス幅よりも短いパルス幅の信号を検出し、その検出した信号のパルス数をカウントする。予めパルスのカウント数と周波数の対応付けをしておくことで、カウント数に基づいて周波数を判定することができる。

(もっと読む)

半導体装置

【課題】クロック伝送回路3の電流消費量の増大を抑えつつ、リードデータのジッタを軽減する。

【解決手段】半導体装置10は、アクティブ期間内に内部クロック信号LCLKよりも周期の長い長周期クロック信号を供給し、アクティブ期間に続くリード期間内に内部クロック信号LCLKを供給するクロック出力制御回路73と、クロック出力制御回路73から出力された内部クロック信号LCLK及び長周期クロック信号を伝送するクロック伝送回路3と、データ入出力端子14と、クロック伝送回路3によって伝送された内部クロック信号LCLKに同期して、データ入出力端子14にリードデータを出力する入出力回路64とを備える。

(もっと読む)

高速量子化器

【課題】高速量子化器および最適化された時間遅延を提供する。

【解決手段】高速量子化器コンパレータの装置と方法は、3部を含む:プリアンプ部、再生ラッチ部、およびデータラッチ部。時間遅延は、再生ラッチ出力の最初の電圧を変えることによって減少される。電流源はコンパレータの底部に提供され、時間遅延最適化を可能にする。PMOS同等化スイッチが停止されたとき、クロック信号をフィードスルーにし、出力に電荷の注入を提供する。これらの電荷によって、コンパレータの時間遅延が可変となる。リセット時間が比較時間より長いために、非常に低い電流が出力電圧を決定する。

(もっと読む)

時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システム

【課題】測定精度および分解能を向上させることができる時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システムを提供すること。

【解決手段】時間デジタル変換器は、開始信号と停止信号との間の遅延時間に対応する第1の値を生成する第1遅延列回路を備える。時間デジタル変換器は、また、遅延開始信号と停止信号との間の遅延時間に対応する第2の値を生成する少なくとも一つの第2遅延列回路を備える。少なくとも一つの遅延素子は開始信号に所定の遅延を与えることにより遅延開始信号を生成し、合成回路は、第1の値および第2の値に基づく出力値を生成する。実施形態に係る時間デジタル変換器では、出力値は開始信号と停止信号との間の遅延時間に対応する。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

スケルチ回路

【課題】消費電流を低減しつつ、回路面積の縮小を図ることが可能なスケルチ回路を提供する。

【解決手段】差動入力される差動入力信号と閾値とを比較して、スケルチ信号を出力するスケルチ回路は、差動入力信号が入力され、前記差動入力信号と前記閾値とを比較して得られた第1のデジタル信号を出力する第1のコンパレータ回路を有する。また、デジタル回路で構成され、前記第1のコンパレータ回路の出力を平滑化し前記スケルチ信号として出力するデジタル平滑化回路を有する。また、第1のコンパレータ回路は、第1のクロック信号により動作が制御され、前記差動入力信号と前記閾値とを比較して得られた第1の差動比較信号を出力する第1のクロックト・コンパレータと第1の差動比較信号が入力され、前記第1の差動比較信号の論理を保持して前記第1のデジタル信号として出力する第1のデータ保持回路を有する。

(もっと読む)

ダイナミック増幅器

【課題】従来のコンパレータは、入力オフセット電圧を高精度に調整することができなかった。

【解決手段】本発明のダイナミック増幅器は、差動対を構成するトランジスタMN1、MN2と、イネーブル状態のリセット制御信号CLKに応じてトランジスタMN1、MN2のドレインの電圧を第1の電圧とするのリセットトランジスタMP5、MP6と、ディスイネーブル状態のリセット制御信号に応じて前記差動対の動作電流を生成する電流源と、トランジスタMN1、MN2のソース間に設けられる抵抗10、11と、トランジスタMN1のソースとトランジスタMN2のソースとの少なくとも一方に接続される容量20、21と、を有し、抵抗10、11の抵抗値及び容量20、21の容量値の少なくとも一方は、オフセット調整信号FL、FRに基づき変更される。

(もっと読む)

分周回路、分周装置及び電子機器

【課題】位相同期した出力信号及びその反転信号を生成・出力できる分周回路の実現。

【解決手段】分周回路1は、クロック信号生成部10と、分周信号生成部20と、出力信号生成部30とから構成される。出力信号生成部30からは、共通のクロック信号CLOCKによって動作/不動作が切り替えられるクロックドインバーターX15,X19によって、位相がほぼ完全に一致した出力信号OUT,XOUTが生成・出力される。

(もっと読む)

誤り検出回路及び集積回路

【課題】メモリ等の入力対象に入力される信号の誤判定を行うのに好適な誤り検出回路を提供する。

【解決手段】集積回路1を、誤り検出回路2A〜2Cとメモリ回路3とを含み、誤り検出回路2A〜2Cを、クロック信号CKの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第1信号IN_A0〜IN_Anを出力するラッチ回路21A0〜21Anと、クロック信号CKを遅延時間t1だけ遅延させる遅延回路20Aと、遅延クロック信号CK_Aの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第2信号IN_B0〜IN_Bnを出力するラッチ回路21B0〜21Bnと、第1信号IN_A0〜IN_Anと第2信号IN_B0〜IN_Bnとが一致しているか否かを比較判定し、判定結果を示す第3信号COMP0〜COMPnを出力する比較回路24_0〜24_nとを含む構成とした。

(もっと読む)

集積回路及び位相制御方法

【課題】分周クロック信号とクロック信号との位相関係を適応的に制御可能な集積回路を提供する。

【解決手段】集積回路は、第1のクロック信号を分周して第2のクロック信号を生成する分周回路と、第1のクロック信号が伝搬する第1の信号伝搬経路と、第2のクロック信号が伝搬する第2の信号伝搬経路と、第1の信号伝搬経路を伝搬後の第1のクロック信号に第2の信号伝搬経路を伝搬後の第2のクロック信号を少なくとも2回掛け合わせることにより出力信号を生成するミキサ回路と、ミキサ回路の出力信号の直流成分を検出する直流検出回路と、直流検出回路が検出した直流成分に応じて第1の信号伝搬経路及び第2の信号伝搬経路の少なくとも一方の伝搬遅延量を制御する制御回路とを含む。

(もっと読む)

多相クロック生成回路

【課題】

位相ノイズが少ない多相クロック生成回路を提供する。

【解決手段】

多相クロック生成回路は,基準クロックを生成する基準クロック生成器と,リング状に接続された複数の遅延回路を有し,前記複数の遅延回路がそれぞれ位相がずれた出力クロックを出力する多相クロック発振器と,前記複数の遅延回路のいずれかの出力端子に前記基準クロックを供給する基準クロック注入回路とを有する。多相クロック発振器のクロックの位相ノイズを低減し周波数変動が抑制できる。

(もっと読む)

1 - 20 / 163

[ Back to top ]