Fターム[5J039KK07]の内容

Fターム[5J039KK07]に分類される特許

1 - 5 / 5

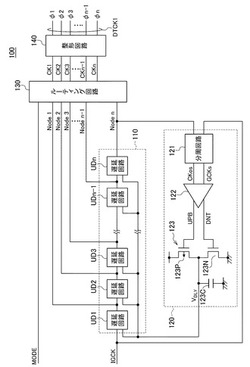

半導体装置及びこれを用いた情報処理システム

【課題】遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成する。

【解決手段】縦列接続された遅延回路UD1〜UDnからなり、入力クロック信号IGCKをk周期遅延させるディレイラインと、遅延回路UD1〜UDnからそれぞれ出力される出力クロック信号Node1〜Nodenに基づいて互いに位相の異なる多相クロック信号DTCK1を生成するルーティング回路130とを備える。nとkの最大公約数をGCM、入力クロック信号IGCKの1サイクルをGCK、多相クロック信号DTCK1の相間隔をUIとした場合、相間隔UIの長さは、UI=GCK×GCM/nで与えられる。これにより、1個の遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成することが可能となる。

(もっと読む)

クロック生成回路

【課題】広帯域の周波数範囲におけるどの周波数の基準クロックを受けてもロックする時間を短くできるクロック生成回路を簡易な回路構成で実現。

【解決手段】基準クロックを第1の個数の電圧制御遅延素子12−1〜12−Nで遅延させて第1の遅延クロックを生成し、第2の個数の電圧制御遅延素子12−1〜12−Kで遅延させて第2の遅延クロックを生成する遅延部11と、前記基準クロックの位相と前記第1の遅延クロックの位相とを比較する位相比較部21と、遅延制御電流を出力するチャージポンプ22と、遅延制御部23と、前記基準クロックの位相と前記第2の遅延クロックの位相とを比較し、前記基準クロックと前記第1の遅延クロックとの位相差を判定する判定部13aと、前記位相差が閾値より大きい場合、前記遅延制御電流が第1の値になり、前記閾値以下の場合、前記第1の値より小さい第2の値になるように制御するチャージ制御部13bとを備える。

(もっと読む)

A−D変換装置

【課題】電圧−周波数変換方式のA−D変換装置の精度を向上する。

【解決手段】2つの等価な鋸波発生回路18Aおよび18Bと、その2つの鋸波発生回路18Aおよび18Bを交互に切り替えるスイッチ回路19と、を含む電圧制御型発振器24を有する、電圧−周波数変換回路を備える。好ましくは、第1の周期の周期信号を出力する第1の電圧制御型発振器と、第1の周期と異なり、かつ第1の周期と一定の比を保つ第2の周期の周期信号を出力する第2の電圧制御型発振器とを備え、サンプリング周期内に含まれる第1の周期信号の波数に基づいて、入力であるアナログ信号に対応するディジタル信号の上位ビットを算出し、サンプリング信号の活性化時点から第1および第2の周期信号の位相が一致する時点までの間に含まれる周期信号の波数に基づいて、デジタル信号の下位ビットを算出する。

(もっと読む)

デジタル方式パルス幅変調装置

【課題】本発明は、上記問題に鑑みてなされたものであって、高い周波数のクロックを使用することなくパルス幅変調の分解能を高めることができるデジタル方式パルス幅変調装置の提供を課題とする。

【解決手段】クロックA(100)を用いて、カウント信号(105)とデジタル信号(107)に従ってパルス幅変調信号(110)のパルス前縁の位置を特定する一方、クロックB(101)を用いて、カウント信号(106)と前記デジタル信号(107)に従ってパルス幅変調信号(110)のパルス後縁の位置を特定することによって、(クロックAの1周期)/Nのパルス幅を単位とするパルス幅変調信号を生成することができる。このため、従来の装置に比べてN倍の分解能を実現することができ、従来と同じ周波数のクロックを用いてもN倍高い分解能を有する高性能な装置を提供できる。

(もっと読む)

可変遅延回路及び半導体集積回路装置

【課題】 高い精度で遅延時間を制御できる可変遅延回路を用いた半導体集積回路装置を提供することを目的とする。

【解決手段】入力クロック信号を遅延させる第1のDLL回路3と、第1のDLL回路よりも高い精度で遅延を制御できる第2のDLL回路10とを有し、第1及び第2のDLL回路の位相比較(31、14)を独立に動作させ、かつ第2のDLL回路の遅延量制御を第1のDLL回路の動作に従属させることで、入力クロック信号に対し所定の位相関係を有する出力クロック信号を出力するように第1及び第2のDLL回路で遅延を与える半導体集積回路装置。

(もっと読む)

1 - 5 / 5

[ Back to top ]