Fターム[5J039KK09]の内容

Fターム[5J039KK09]に分類される特許

61 - 80 / 321

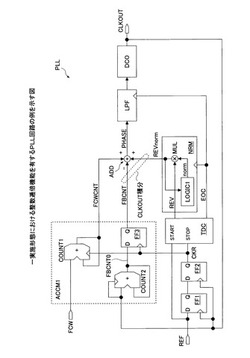

PLL回路、PLL回路の動作方法およびシステム

【課題】 回路規模を増加することなく、PLL回路の精度を向上する。

【解決手段】 時間計測回路は、基準クロックの遷移エッジが現れてから、出力クロックの遷移エッジが2回現れるまでの時間間隔をカウント値として計測する。位相差正規化回路は、計測された時間間隔を出力クロックのクロック数で表される微少位相差に正規化する。また、位相差正規化回路は、PLL回路のロック後に、”1”または”2”を示す微少位相差が連続して現れるときに、”1”と”2”がランダムに現れるまで正規化係数を徐々にずらす。演算回路は、出力クロックの積算値から微少位相差の値を引いた値を、周波数制御語の積算値から差し引いて、基準クロックと出力クロックの位相差を示す位相差信号を生成する。発振回路は、基準クロックと出力クロックの位相を合わせるために、位相差信号に基づいて出力クロック信号の周波数を変更する。

(もっと読む)

半導体装置

【課題】外部クロック信号CL、チップセレクト信号CE等の制御信号のノイズを適切に除去する。

【解決手段】半導体装置内部において生成される内部クロック信号ICLの立ち上がり及び立ち下がりのタイミングに同期して入力信号INの値を複数の異なるタイミングで保持する第1保持回路20及び第2保持回路22を備え、保持された値に応じて入力信号INのノイズを除去するノイズ除去回路を設ける。

(もっと読む)

PWM電力変換装置のデッドタイム補償装置

【課題】デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減することで遅延誤差TDLYを短縮する。

【解決手段】デッドタイム補償部30は、PWMゲート指令Gate_UとPWM出力Vce_Uとの位相差に応じて求めるデッドタイム補償分Vcmp_UでPWM電圧指令Vcmd_Uの電圧値を増減し、この補償後のPWM電圧指令Vcmd_U’をPWM波形発生部20でPWMゲート指令に変換することで、デッドタイム補償前のPWMゲート指令とデッドタイム補償後の相電圧出力との誤差(位相差)を低減する。

(もっと読む)

半導体設計装置

【課題】セットアップ違反やホールド違反を発生させずに、電力を消費するタイミングを分散させることができる半導体設計装置を提供する。

【解決手段】STA部5は、フリップフロップのクロックレイテンシの現在の設計値に基づいて、フリップフロップのセットアップ時間のマージンであるセットアップスラックを算出する。HSLD部6は、算出したセットアップスラックに基づいて、タイミング違反を起こさない範囲で、フリップフロップのクロックレイテンシを現在の設計値よりも早める方向に調整する。PAS部7は、HSLD部6によるレイテンシ制御の結果、クロックレイテンシ分布においてシンク数に閾値以上のピークが残る場合、HSLD部6による再計算後のタイミング情報により、タイミング違反を起こさない範囲で、フリップフロップのクロックレイテンシをスムージングする。

(もっと読む)

デジタル位相差検出器およびそれを備えた周波数シンセサイザ

【課題】高精度で回路面積および消費電力が小さいデジタル位相差検出器を提供する。

【解決手段】デジタル位相差検出器は、第1の信号を累積的に遅延させて各遅延量の信号を生成する遅延回路(10)と、第2の信号に同期して各遅延量の信号をラッチするフリップフロップ群(20)と、フリップフロップ群の出力から、第1の信号の立ち上がりと第2の信号の立ち上がりおよび立ち下がりのいずれか一方との第1の位相差、および第1の信号の立ち下がりと第2の信号の立ち上がりおよび立ち下がりのいずれか一方との第2の位相差を検出するエッジ検出器(30)と、第1および第2の位相差を記憶する記憶回路(40)と、記憶回路が記憶している過去の第1および第2の位相差の差分およびエッジ検出器が新たに検出した第1および第2の位相差の差分から第1の信号の周期を算出し、当該周期を基準にして第1および第2の信号の位相差を正規化する正規化回路(50)とを備えている。

(もっと読む)

TDC回路

【課題】検出可能範囲の拡大と分解能の向上とを両立可能なTDC回路を提供する。

【解決手段】2n個の遅延量の異なる反転遅延素子を直列接続して形成されたループをそれぞれ含む第1の遅延回路および第2の遅延回路に、第1パルス信号駆動回路および第2のパルス信号駆動回路により、第1の遅延回路および第2の遅延回路にそれぞれ検出対象エッジとリセットエッジを有するパルス信号伝搬させる構成を持つバーニアディレイに、第1の遅延回路の反転遅延素子のいずれかと第2の遅延回路の反転遅延素子のいずれかに対して、伝搬されるリセットエッジの入力に対応する論理反転を選択的に遮断する操作をそれぞれ行う遮断回路と、第1の遅延回路および第2の遅延回路に含まれる遮断対象の反転遅延素子に対して、伝搬された検出対象エッジの入力に応じて反転した論理をリセットする操作をそれぞれ行うリセット回路とを備える。

(もっと読む)

半導体装置および制御回路

【課題】実動作時における内部クロック信号のジッタ量を検出し、検出したジッタ量を外部で利用可能に出力できる半導体装置を得ること。

【解決手段】クロック生成回路が出力しているクロック信号と、該クロック信号を少なくとも1周期遅延した遅延クロック信号との位相差に基づき前記クロック信号に含まれるジッタ成分を検出するジッタ検出部と、前記検出されたジッタ成分を電圧信号に変換する増幅回路を有する増幅部と、前記変換された電圧信号を外部へ出力するためのジッタ出力端子とを備えたことを特徴とする。

(もっと読む)

デジタルPLL

【課題】位相差情報をデジタル値で出力するデジタルPLLにおいて、消費電力を抑えたデジタルPLLを提供することにある。

【解決手段】デジタルPLL100は、発振器10、整数位相算出部20、小数位相算出部30、位相差算出部40、位相差変化量モニタ部50、および発振器制御部60を有する。PLLにおいては発振器の出力周波数が、分周比により設定された所望の周波数に近づく、即ちロック状態に近づくにつれ位相差の変化量は減少していくことから、位相差変化量モニタ部50にて位相差の変化量をモニタし、変化量が整数位相算出部20の1LSB未満である「1」未満になった時点で整数位相算出部20におけるカウンタ動作を停止する。

(もっと読む)

局部発振器

【課題】デジタル制御発振器の出力と参照信号とが非同期であっても、安定したPLL動作を確立できる局部発振器を提供することを目的とする。

【解決手段】デジタル制御発振器の発振信号と前記参照信号との位相差を発振器分数位相として出力し、また、前記発振信号の位相が、前記参照信号の位相に対して、前記発振信号の半周期よりも位相が遅れている場合に「−1」、遅れていない場合に「+1」の補整情報を出力する時間デジタル変換器と、|前記補整情報−予測位相情報|>|前記補整情報+前記第1位相情報−前記予測位相情報|の場合に、前記第1位相情報に前記補整情報を加算したものを第2位相情報として出力し、|補整情報−発振器予測位相|>|補整情報+第1位相情報−発振器予測位相|でない場合に、前記第1位相情報を第2位相情報として出力する補正部と、を備えている。

(もっと読む)

発振異常検出回路

【課題】発振回路の発振周波数の異常を検出することができる発振異常検出回路を提供することである。

【解決手段】クロック信号CLKを、直列接続された複数の遅延素子20〜25を用いて遅延させる遅延部2と、遅延素子20〜25の出力信号であるクロック信号CLK0〜CLK5から、全体遅延時間tda内における、クロック信号CLKの変化を示す発振信号パターンD0〜D5を取得する信号パターン取得部3と、期待信号パターンE0〜E5を予め記憶する期待値記憶部4と、発振信号パターンD0〜D5と期待信号パターンE0〜E5とを比較する比較部5と、比較部5による比較結果が一致しない場合、発振回路100に発振異常が生じていると判定する異常判定部6とを備えた。

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

クロック異常検出回路

【課題】クロック異常を検出する精度を向上させる技術を提供する。

【解決手段】被検査クロックを遅延させる第1の遅延回路の出力と第2の遅延回路の出力よりLow期間を決める。定められたLow期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。第1の遅延回路の出力と第2の遅延回路の出力よりHigh期間を決める。定められたHigh期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。Low期間の異常とHigh期間の異常を統合する。

(もっと読む)

DPLL回路

【課題】入力データに混入したノイズの幅がクロック周期程度にまで大きくなり、ノイズ位置が入力データの中間位置に発生した場合にも、入力データからノイズを除去できる。

【解決手段】1ビットを4クロック幅で構成する入力データからノイズフィルタで雑音を除去し、この雑音を除去した入力データと同期したクロックを生成するDPLL回路において、ノイズフィルタは、入力データに対して、4段縦続接続のシフトレジスタを設け、このシフトレジスタのレジスタ11,12,13のクロック同期した出力の一致・不一致状態に応じて最終段のレジスタ16の入力を切り替える入力ロジック17を設ける。

さらに、ノイズフィルタでは除去しきれない入力データの歪みを歪み除去回路で除去する。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

擬似ランダム信号発生装置、通信システム、及び画像形成システム

【課題】放射ノイズを低減する。

【解決手段】N段のDフリップフロップ(DFF)を備え、隣り合う前段のDFFの非反転端子が隣り合う後段のDFFの入力端子に接続され、最終段のDFFの非反転端子及び最終段以外の1つの段のDFFの非反転端子がEXORを介して最初の段のDFFの入力端子に接続され、最終段のDFFの非反転端子から2N−1ビットのビットパターンを繰り返したパターン信号を出力するパターン信号出力回路10、パターン信号が2N−1ビット出力される毎にビットパターン長を示す信号を出力するビットパターン長カウント回路12、ビットパターン長を示す信号に基づきパターン信号出力回路10の非反転端子及び反転端子から複数の端子を複数個ずつ繰り返し選択するための選択信号を出力するM進カウンタ回路14、及び選択信号に応じて該複数の端子から出力された信号を選択し、選択した信号を擬似ランダム信号として出力するタップ出力シフト回路16を含む。

(もっと読む)

PLLロック検出回路、及びPLLロック検出回路を有するPLLシンセサイザ回路

【課題】適切にPLL回路ロックがなされているか否かを検出する。

【解決手段】PLL回路ロックがなされているか否かを検出するPLLロック検出回路を構築する。ここにおいて、そのPLLロック検出回路は、基準発振器から供給される基準発振周波数を示す基準発振周波数信号と、前記基準発振周波数を分周して得られたリファレンス周波数を示し位相比較器に供給されるリファレンス周波数信号と、VCOから供給される電圧制御発振周波数を分周して得られた比較周波数を示し前記位相比較器に供給される比較周波数信号とを受ける、そして、前記リファレンス周波数信号と前記比較周波数信号とに基づいて、前記PLL回路ロックを示すロック検出信号を出力する。

(もっと読む)

電子回路、電子機器、デジタル信号処理方法

【課題】多相クロックを使用してデジタル信号処理を行なう場合に、クロック信号の各位相関係を正しく保ったまま高速動作が要求される各デジタル信号処理部まで多相クロックを分配できるようにする。

【解決手段】基準タイミング生成部110は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低い基準タイミング信号J0を生成して局所タイミング再生部120に供給する。局所タイミング再生部120は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低いクロック信号であって、高速信号処理部140におけるデジタル信号処理の基準となる複数のクロック信号でなる多相タイミング信号J2を生成して高速信号処理部140に供給する。高速信号処理部140と局所タイミング再生部120を1対1で設け、1つの局所タイミング再生部120から複数の高速信号処理部140へ多相タイミング信号J2を分配しないようにする。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】入力クロックの周波数変化に依存して変調プロファイルが変化しないスペクトラム拡散クロックジェネレータを提供する。

【解決手段】スペクトラム拡散クロックジェネレータは、切替信号に応じて入力クロックを遅延し、出力クロックとして出力する遅延ラインと、入力クロックの周期を計測する入力クロック周期計測部と、入力クロック周期計測部の計測結果に応じて、1変調周期当たりの出力クロックのサイクル数、および、あらかじめ設定された変調度に対応する入力クロックの所定サイクル当たりの出力クロックの周期の変調ステップ幅を算出し、算出されたクロックサイクル数および変調ステップ幅に基づいて切替信号を生成する遅延ライン制御部とを備えている。

(もっと読む)

位相周波数比較器およびシリアル伝送装置

【課題】ループ帯域幅を安定させる位相周波数比較器を簡易な回路で提供する。

【解決手段】基準クロック102とフィードバッククロック103とを入力とし、周波数シンセサイザへのアップ信号と周波数シンセサイザへのダウン信号とを出力する位相周波数比較器において、第1位相周波数比較回路106と、第2位相比較回路107と、前記基準クロック102と前記フィードバッククロック103とを入力とし、前記第1位相周波数比較回路106の入力と前記第2位相比較回路107の入力とに、所定の相対的な遅延を与える遅延回路部108とを備え、周波数比較を前記第1位相周波数比較回路106で行い、位相比較を前記第1位相周波数比較回路106とラッチを制御した前記第2位相比較回路107とで行う位相周波数比較器。

(もっと読む)

半導体集積回路の設計方法及びプログラム

【課題】タイミング制約を満たすためにセルの物理的な位置やRTL(Register Transfer Level)を変更する必要がなく、回路の最適化を短時間に行うことができ、半導体集積回路の設計期間を短縮することができる半導体集積回路の設計方法、設計プログラムを提供する。

【解決手段】半導体集積回路のネットリストに対して静的タイミング解析を行うことにより、所定のタイミング制約を満たさないタイミングエラーパスを検出し、前記タイミングエラーパスを含む第1の論理ブロックと、フリップフロップを介して前記第1の論理ブロックに接続され、所定のタイミング制約を満たす第2の論理ブロックとを抽出し、前記第1の論理ブロックと前記第2の論理ブロックとの間のフリップフロップが正相/逆相フリップフロップである場合は、当該正相/逆相フリップフロップを逆相/正相フリップフロップに変更する。

(もっと読む)

61 - 80 / 321

[ Back to top ]