Fターム[5J039KK09]の内容

Fターム[5J039KK09]に分類される特許

141 - 160 / 321

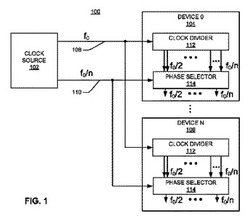

信号の較正方法および装置

信号較正方式において、一連の複数の信号の間で所望の位相関係が維持される。たとえば、いくつかの態様では、高速度の基準クロック信号から発生したクロックツリーの所望の位相を、低速度の基準クロック信号と、クロックツリーの様々な位相に関連付けられた低速度のクロック信号との間の位相差を検出することにより、維持することが可能である。いくつかの態様では、クロックツリーの使用中に発生するフレーミングオフセットを検出することにより、クロックツリーの所望の位相を維持することが可能である。 (もっと読む)

FM信号のノイズキャンセラ回路

【課題】FM信号に含まれるノイズを適切に低減する。

【解決手段】処理対象となるFM信号の復調前の信号の振幅と閾値とを比較してFM信号の欠落を検出する検出回路102と、FM信号の復調後の信号に基づいて閾値を設定する閾値設定回路104と、を備えるFM信号のノイズ検出回路とする。

(もっと読む)

ノイズ除去回路および方法

【課題】デジタルデバイスに入力される周期的パルス信号の一周期にわたってノイズパルスを除去することができるノイズ除去回路および方法を提供する。

【解決手段】周期的パルス信号からノイズパルスを除去するノイズ除去回路は、固定高レベルを入力とし、周期的パルス信号aおよびリセット信号dに従って高レベルと低レベルとの間で回路出力を変化させるフリップフロップ回路10と、周期的パルス信号aのレベルが変化してから一周期内で次にレベル変化するまでは固定高レベルの入力により、それ以後はリセット信号dによりフリップフロップ回路の出力を固定するリセット制御部20と、を有する。

(もっと読む)

信号再生回路向け位相比較回路及び信号再生回路向け位相比較回路を備える光通信装置

【課題】 1/Nレート構成に対応可能な高精度な位相比較回路を得る。

【解決手段】それぞれ、N相クロック信号CLKの各クロック信号を、受信データ信号DINの立ち上がりに同期してトラックホールドするN個のトラックホールド回路を備える。これらのN個のトラックホールド回路の出力から、受信データ信号DINの立ち上がりエッジが、クロック信号CLKの立ち上がりエッジに位置しているクロック信号をトラックホールドしているもののみをセレクタで選択して、位相差信号として出力する。

(もっと読む)

位相比較回路

【課題】D−FFの内部遅延が無視できない高速動作時において位相比較回路の低消費電力化を実現する。

【解決手段】マスタースレーブマスター型D−FF11は、第1のM−FF11−1,S−FF11−2および第2のM−FF11−3が縦続接続され、入力NRZデータ信号をクロック信号に応答して識別し、S−FFおよび第2のM−FFから出力する。遅延回路4は、入力NRZデータ信号をS−FFと同じ時間だけ遅延させる。第1のEXOR回路7は遅延回路の出力とS−FFの出力の排他的論理和演算を行ない、第2のEXOR8はS−FFの出力と第2のM−FFの出力の排他的論理和演算を行なう。加算器9は第1のEXOR回路の出力と第2のEXORの反転出力を加算する。

(もっと読む)

クロックゲーティング回路

【課題】設計工数の増大を防止するために、簡単な回路構成で故障検出を可能にしたクロックゲーティング回路及びマクロセルを提供すること。

【解決手段】本発明に係るクロックゲーティング回路は、入力したクロック信号CLK12に対応するゲーテッドクロック信号GCLK13の出力をクロックイネーブル信号CEN10に応じて制御するクロックゲーティング回路である。また、CEN10の信号値をクロック信号CLK12に同期してラッチするラッチ5を有する。そして、CLK12を入力し、ラッチ5の出力信号に応じて、GCLK13の出力を制御するAND4を有する。さらに、ラッチ5の出力信号の信号値をクロック信号CLK12に同期してラッチし、ラッチした値を出力するラッチ6を備えることを特徴としている。それにより、簡単な回路構成でスキャン試験を実行することができる。

(もっと読む)

半導体集積回路

【課題】クロック信号の位相、デューティー比等の変動に対し耐性の強い、小型の半導体集積回路を提供する。

【解決手段】複数配設される回路部と、クロック信号の立ち上がりエッジから前記クロック信号を逓倍した周期の第1信号を生成する第1カウンタと、前記クロック信号の立ち下がりエッジから前記クロック信号を逓倍した周期の第2信号を生成する第2カウンタと、前記第1信号が転送される第1ラインと、前記第2信号が転送される第2ラインと、前記第1ライン及び前記第2ラインと接続され前記第1信号と前記第2信号との位相差から第3信号を生成し前記回路部に前記第3信号を出力する位相比較器と、を備え、前記位相比較器は、前記第1ライン及び前記第2ライン上に配設され且つ前記第1ライン及び前記第2ラインの末端と前記回路部との間に複数配設される。

(もっと読む)

ジッタ測定回路

【課題】周期信号の周期を測定することなくジッタ量をディジタル出力すること。

【解決手段】本発明に係るジッタ測定回路10は、入力される被測定信号5を当該被測定信号のエッジから所定の時間単位である第1の時間で遅延させることによりエッジ間パルス信号6を生成するエッジ間パルス生成部1と、エッジ間パルス信号6を、所定の時間単位である第2の時間を整数倍した値により除算し、該除算演算による剰余結果を剰余結果信号Mとして出力するパルス幅剰余分割部2と、剰余結果信号Mの値が最小となる場合の整数の値を、エッジ間パルス信号6のサイクルジッタ値信号Dとして出力するワンホットステート部4と、を有する。

(もっと読む)

デジタル位相検出器及びデジタル位相同期回路

【課題】デジタル位相検出器の時間分解能をデジタル制御し、回路規模・消費電力を低減する。

【解決手段】信号S1が入力される直列に接続された第1の遅延素子1011〜101Nと、信号S2が入力される直列に接続された第2の遅延素子1021〜102Nと、各々の第1の遅延素子の出力が与えられ、各々の第2の遅延素子の出力をクロックとするラッチ回路1031〜103Nと、前記ラッチ回路の出力値に基づいて信号S1のパルス幅を示すデジタルコードPWmを算出して出力するデコーダ回路104と、デジタルコードPWmと所定のデジタルコードPWrとを比較し、比較結果を出力する比較器105と、前記比較結果に基づいて前記第1及び第2の遅延素子の少なくともいずれか一方の遅延時間を制御する遅延制御回路106と、を備える。

(もっと読む)

CRC演算回路、シリアルインタフェイス装置、画像形成装置

【課題】本発明は、容易な回路設計で高速データ伝送に対応することが可能なCRC演算回路を提供することを目的とする。

【解決手段】本発明に係るCRC演算回路は、伝送データからシリアル処理でCRC符号を算出する演算過程を解析して導き出される所定の演算式に基づいて、前記伝送データからパラレル処理で前記CRC符号を算出する論理回路を有して成る構成とされている。

(もっと読む)

パワー半導体の駆動回路装置およびそれに用いる信号伝達回路装置

【課題】制御出力信号が制御入力信号を忠実に復元しているか否かを検出、監視する自己診断機能を備えたパワー半導体の駆動回路装置および信号伝達回路装置を提供する。

【課題を解決するための手段】

パワー半導体の駆動回路装置30は、制御入力信号Sinを生成する電子制御装置32と、主経路34と自己診断機能38を有する信号伝達回路装置300と、信号伝達回路装置300からの制御出力信号Soutで駆動されるパワー半導体40とを備える。自己診断機能38は帰還パルス送信回路360、第2信号伝達回路370および第2受信回路380を有する。第2受信回路380では制御出力信号Soutが制御入力信号Sinに一致しているか、または不一致であるかを比較し、比較した結果を比較信号出力端子390に出力する。比較信号出力端子390に出力された信号は電子制御装置32に伝達される。

(もっと読む)

半導体装置

【課題】Loopbackテストの際に電圧振幅マージン不足の半導体装置が次工程へと流出するのを防止する。

【解決手段】シリアライザ17は、テストモード期間にクロック信号CLK1に応じてパタン発生器20が出力するパラレルのテストパタン信号をシリアル信号に変換して出力バッファ16よりテスト治具側の外部ループバックパスへ出力する。CPU21は、遅延制御信号DLC1,DLC2によって一方の可変遅延素子VDL1,VDL2の遅延時間を制御する。入力バッファ10の出力であるテストパタン信号VRxとLSIテスタ等より印加される外部基準電圧Vrefとの差動信号VRx1がCDR12に印加され、クロック信号CLK2が生成される。両信号VRx,CLK2の一方の位相が変更されて、外部基準電圧Vrefの値毎にタイミングマージンがチェックされる。

(もっと読む)

デューティ比補正回路

【課題】デューティ比補正回路のデューティ比検知速度を固定せずに、必要に応じて調整することによって、速いデューティ比の補正が必要な場合はデューティ比検知速度を増加させ、必要でない場合はデューティ比検知速度を減少させるデューティ比補正回路を提供する。

【解決手段】検知速度制御信号によりデューティ比検知速度が調整され、クロックのデューティ比を検知して補正信号を出力するデューティ比検知部と、前記補正信号に応答して前記クロックのデューティ比を調整するデューティ比補正部とを備える。

(もっと読む)

パルス検出装置及びパルス検出方法

【課題】パルス信号を高精度に検出すること。

【解決手段】パルス検出装置1は、所定期間に中間電位を含むパルス信号を検出する。また、パルス検出装置1は、パルス信号の中間電位を、ローレベル又はハイレベルに固定する信号固定手段を備えている。さらに、信号固定手段は、パルス信号が入力される入力信号線に接続されたプルダウン抵抗9又はプルアップ抵抗であるのが好ましい。なお、パルス検出方法は、パルス信号の中間電位を、ローレベル又はハイレベルに固定する信号固定工程を含んでいる。

(もっと読む)

ディジタル位相検出器およびPLL

【課題】従来のディジタル位相検出器は、遅延素子としてインバータ等の遅延時間を使用しているが、遅延素子の配置および配線の固定が必要であることからゲート・アレイやFPGA等ではインプリメントすることが難しい。遅延素子の遅延時間はデバイスの種類やプロセスばらつきにより変動するため位相検出の精度に影響が出る。

【解決手段】2つのクロックが整数比に近い周波数を有している場合において、第1のクロックを入力とするM/N逓倍する逓倍器と、逓倍器の出力クロックを用いて第2のクロックをラッチするF/Fと、F/Fの出力を微分する微分回路と、逓倍器の出力クロックを入力とするカウンタと、微分回路の出力に応じて前記カウンタの出力を保持するラッチ回路と、ラッチ回路の出力を加算する第1の加算器と、第1の加算器の出力を固定値から減算する第2の加算器と、第2の加算器の出力を順次積算する積算器と、を備えるよう構成する。

(もっと読む)

DLL回路、および半導体装置

【課題】DLLクロックが消失した場合に、位相検知における誤判定の結果を基に、遅延量が更新されることを回避し、ロック制御におけるDLLクロックサイクルの短縮化と、DLL回路の動作安定性の向上を図る。

【解決手段】本発明のDLL回路は、入力されるクロック信号の遅延量を制御する遅延信号を出力する遅延制御回路13と、この遅延信号に基づいた遅延量をクロック信号に付加し、DLLクロックとして出力する遅延回路12と、DLLクロック信号のクロッキング動作の有無を検知するDLLクロック検知回路31とを備える。そして、DLLクロック検知回路31は、DLLクロックのクロッキング動作が検知されない場合に、遅延制御回路13による遅延量の更新制御を停止させる。

(もっと読む)

位相比較器、位相同期回路及び位相比較制御方法

【課題】入力断検出部を位相比較器に内蔵することで位相比較器を実装するPLL回路の小型化を図る。

【解決手段】参照信号を入力すると共に、参照信号に基づく被参照信号を帰還入力し、これら入力した参照信号及び被参照信号の立ち上がりエッジを検出し、参照信号の立ち上がりエッジ及び被参照信号の立ち上がりエッジ間の位相差を検出する位相差検出部21と、位相差検出部21にて検出した位相差に基づき、位相差を小さくすべく、定電流出力動作を実行する定電流出力部24と、被参照信号のエッジを検出した後、参照信号のエッジを検出する前に、被参照信号のエッジを再度検出した場合、参照信号の入力断として検出する入力断検出部23とを有している。

(もっと読む)

デューティ補正回路

【課題】伝送速度が異なる複数のマンチェスタ符号化信号のデューティ比を補正可能なデューティ補正回路を得ること。

【解決手段】本発明にかかるデューティ補正回路は、マンチェスタ符号化された受信信号の連続する2つの立上りエッジの間隔または立下りエッジの間隔に基づいて受信信号の伝送速度を判定するシンボル周期判定回路7と、受信信号の“Hレベル”または“Lレベル”の継続時間を観測するエッジ検出回路2およびカウンタ3と、観測結果および判定結果に基づいて波形歪みを検出する波形歪み検出回路4と、波形歪みが検出された場合に波形歪み発生期間、受信信号を反転することにより波形の補正を行うセレクタ5と、を備えることとした。

(もっと読む)

IQ信号発生器のためのスワップ機能を実施するためのシステム及び方法

【課題】IQ信号発生器に対してスワップ機能を実施するためのシステム及び方法を提供する。

【解決手段】IQ信号発生器を実施するためのシステム及び方法は、クロック入力信号に応答してI信号を発生するマスターラッチ、及び反転クロック入力信号に応答してQ信号を発生するスレーブラッチを含む。マスターセレクタが、マスターラッチからスレーブラッチへの通信経路を形成するように構成され、スレーブセレクタが、スレーブラッチからマスターラッチへのフィードバック経路を形成するように構成される。上述のI及びQ信号は、いかなる介在電子回路もなしにそれぞれマスター及びスレーブラッチから直接出力される。

(もっと読む)

デジタル位相ロックループ(DPLL)における電力消費を制御するシステム及び方法

【解決手段】相異なる周波数クロックの組から選択された参照クロックを生成するように適合されたプログラマブル周波数デバイスを備えた装置であって、プログラマブル周波数デバイスは更に、相異なる周波数クロック間での切り替えの際に、参照クロックのトリガエッジの同じ時間的関係を維持するように適合される。装置は更に、入力信号と出力信号との間の所定の位相関係を確立するために選択された参照クロックを使用する、デジタルPLL(DPLL)のような位相ロックループを備える。相異なる周波数クロック間の切り替えの際に参照信号の同じ時間的関係を実質的に維持することで、参照クロックが変化しても、位相ロックループ(PLL)の連続且つ有効な動作は、大きくはディスターブされない。これは、装置の電力消費を制御するために使用され得る。 (もっと読む)

141 - 160 / 321

[ Back to top ]