Fターム[5J039KK13]の内容

Fターム[5J039KK13]に分類される特許

201 - 220 / 417

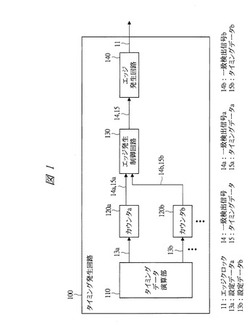

タイミング発生回路、半導体試験装置および半導体試験方法ならびに半導体デバイス

【課題】1つのエッジ発生回路で複数のエッジクロックの出力を行うことを可能とするタイミング発生回路を提供する。

【解決手段】エッジクロック11を出力するタイミング発生回路100であって、複数のカウンタと、複数のカウンタにそれぞれ個別の設定データを出力するタイミングデータ演算部110と、複数のカウンタから出力された一致検出信号に基づいて、複数のカウンタから出力されたタイミングデータを選択し、1系統の一致検出信号14とタイミングデータ15として出力するエッジ発生制御回路130と、エッジ発生制御回路130から出力された一致検出信号14とタイミングデータ15に基づいてエッジクロック11を発生するエッジ発生回路140とを有し、1つのエッジ発生回路140によって複数のエッジクロック11を出力する。

(もっと読む)

ジッタ印加回路、パターン発生器、試験装置、および、電子デバイス

【課題】高周波のタイミングジッタを有するジッタ重畳信号を容易に生成する。

【解決手段】ジッタを有するジッタ重畳信号を生成するジッタ印加回路であって、与えられる基準信号を並列に受け取り、それぞれ予め設定される遅延量で遅延させる複数の遅延回路と、それぞれの遅延回路が出力する信号のタイミングに応じて、ジッタ重畳信号のそれぞれのエッジを生成する信号生成部と、それぞれの遅延回路に、ジッタ重畳信号の各エッジに印加すべきジッタに応じた遅延量をそれぞれ設定する遅延設定部とを備え、少なくとも一つの遅延回路の遅延量が、ジッタ重畳信号が有するべき平均周期の整数倍とは異なる値に設定されるジッタ印加回路を提供する。

(もっと読む)

ジッタ印加回路、パターン発生器、試験装置、および、電子デバイス

【課題】高周波数かつ大振幅のジッタを生成する。

【解決手段】ジッタを有するジッタ重畳信号を生成するジッタ印加回路であって、与えられる基準信号を、それぞれ予め設定される遅延量で順次遅延させる、縦続接続された複数の遅延回路と、それぞれの遅延回路が出力する信号のタイミングに応じて、ジッタ重畳信号のそれぞれのエッジを生成する信号生成部と、ジッタ重畳信号の各周期に印加すべきジッタに応じた遅延量をそれぞれ設定する遅延設定部とを備え、少なくとも一つの遅延回路の遅延量が、ジッタ重畳信号の平均周期の整数倍とは異なる値に設定されるジッタ印加回路を提供する。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の駆動方法

【課題】ヒステリシス特性を示すインバータ回路の構成を簡素化しながら消費電力を低減する。

【解決手段】インバータ回路Q1は、Pチャネル型のトランジスタTR1とNチャネル型のトランジスタTR2とで構成される。トランジスタTR1およびトランジスタTR2の各々のバックゲートには閾値制御信号C1が供給される。閾値制御信号C1は、インバータ回路Q1からの出力信号SOUT1のレベルが低下し始める時点にてローレベルに設定されるとともに当該時点の経過後にハイレベルに設定され、かつ、出力信号SOUT1のレベルが上昇し始める時点にてハイレベルに設定されるとともに当該時点の経過後にローレベルに変化する。

(もっと読む)

ジッタ増幅回路、信号発生回路、半導体チップ、及び試験装置

【課題】入力信号に含まれるジッタを増幅するジッタ増幅回路150。

【解決手段】入力信号に含まれるジッタを増幅するジッタ増幅回路であって、入力信号を受け取り、入力信号の波形を歪ませることにより、入力信号の高調波成分を生じさせる歪回路と、歪回路が出力する歪信号を、ジッタを増幅すべき増幅率に応じた次数の高調波成分以外の成分を除去して通過させるフィルタとを備えるジッタ増幅回路。

(もっと読む)

半導体装置

【課題】第1電源で動作する第1回路および第1電源とは異なる第2電源により動作する第2回路を有する半導体装置において、第1回路から第2回路に供給する信号におけるジッタの発生の抑制を図る。

【解決手段】第1電源線5(AVD)および第2電源線6(AVS)に接続された第1回路1と、第3電源線7(VDD)および第4電源線8(VSS)に接続された第2回路4(3)と、前記第1回路から出力される第1信号を受け取って前記第2回路に第2信号を供給するバッファ11と、前記第1電源線と前記第3電源線との電位差に応じて前記バッファの遅延時間を制御する制御部10と、を備えるように構成する。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の駆動方法

【課題】ヒステリシス特性を示すインバータ回路の構成を簡素化しながら消費電力を低減する。

【解決手段】インバータ回路Q1は、Pチャネル型のトランジスタTR1と、Nチャネル型のトランジスタTR2とで構成される。信号供給点R1とトランジスタTR1のチャネルコンタクト領域Aとの間には容量C1が介在し、信号供給点R1とトランジスタTR2のチャネルコンタクト領域Aとの間には容量C2が介在する。信号供給点R1には閾値制御信号SC1が供給される。閾値制御信号SC1は、インバータ回路Q1からの出力信号SOUT1のレベルが低下し始める時点にてローレベルに設定されるとともに当該時点の経過後にハイレベルに設定され、かつ、出力信号SOUT1のレベルが上昇し始める時点にてハイレベルに設定されるとともに当該時点の経過後にローレベルに変化する。

(もっと読む)

位相調整回路および試験装置

【課題】被測定信号の位相を、基準信号の位相に精度よく合わせることができる位相調整回路を提供する。

【解決手段】被測定信号の位相を調整する位相調整回路であって、トリガ信号を生成するトリガ発生部と、基準信号を受け取り、共通の前記トリガ信号のタイミングで、被測定信号および基準信号を測定し、被測定信号および基準信号のそれぞれの信号レベルの差分に応じた測定結果を出力するレベル比較部と、レベル比較部が出力する信号レベルの差分が略零となるように、被測定信号の位相を調整する信号位相調整部とを備える位相調整回路を提供する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】遅延セルの遅延時間がターゲットの遅延時間からずれた場合であっても、出力クロックの変調度のがたつきを軽減することができるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】スペクトラム拡散クロックジェネレータは、直列に接続された複数のファインセルを有し、第1の信号に応じて選択されたファインセルの段数分の時間入力クロックを遅延するファインセルの選択回路と、直列に接続された複数のコースセルを有し、第2の信号に応じて選択されたコースセルの段数分の時間ファインセルの選択回路の出力信号を遅延し出力クロックとして出力するコースセルの選択回路と、ファインセルの選択回路の出力信号に応じて、第1および第2の信号を生成し出力する制御回路とを備える。制御回路は、累積遅延が増加する期間は、1クロック毎に、コースセルの段数差の変化分がマイナスの値とならないように制御し、累積遅延が減少する期間は、1クロック毎に、コースセルの段数差の変化分がプラスの値とならないように制御する。

(もっと読む)

速度判定方法、速度判定回路および速度判定装置

【課題】伝送速度の判定を高速に行う。

【解決手段】入力端子1への入力信号に含まれるプリアンブル信号のパターン周期の整数倍に相当する遅延差をもつ2つの信号を生成する遅延素子2,3と、該遅延素子2,3から出力する前記2つの信号の論理を比較する一致検出回路4と、該一致検出回路4の出力信号を積分する積分回路6と、該積分回路6で得られた信号を閾値Vrefと比較して判定結果を出力する比較回路7とを備える。

(もっと読む)

ポートからポートへの遅延を実装することにより雑音を減らす方法

【課題】

ポートからポートへの遅延を実装することにより雑音を減らす。

【解決手段】

雑音を減らす方法は、次を含む:電源供給網をオンにする時に、高速データリンクの最大の雑音の周波数を特定すること;その最大の雑音を最小化する、第1のポートと第2のポートの間の遅延時間を特定すること;及び、第1のポートをオンにした時から、その遅延時間後に、第2のポートをオンにすること。他の実施例も開示し請求する。

(もっと読む)

クロック伝搬回路

【課題】クロックスキューをより確実に抑制することが可能なクロック伝搬回路を提供する。

【解決手段】クロック伝搬回路10内のクロック伝搬ドライバ11及び12は、クロック停止制御信号SCSに応じてクロック信号CLKの伝搬を停止する。経時劣化検出回路20は、クロック伝搬ドライバ11及び12の内で動作状態にある一方のクロック伝搬ドライバ11から伝搬されたクロック信号CLKにより動作して自分自身の遅延劣化を検出する。動作状態切替部30は、経時劣化検出回路20による遅延劣化の検出に応じて、クロック伝搬ドライバ11に代えてクロック伝搬ドライバ12を動作状態とし、クロック信号CLKの論理回路ユニット2内の各回路への伝搬を継続する。

(もっと読む)

モニタ回路及び電力低減システム

【課題】LSIテスト時においても選別用のモニタリングを行うことができると共に、小さな面積で簡便な構成によりモニタ可能なモニタ回路を提供すること。

【解決手段】モニタ回路は、クロック信号39に同期して入力信号を取り込むフリップフロップ回路32と、クロック信号40に同期して入力信号を取り込むフリップフロップ回路34と、フリップフロップ回路34の出力信号を受ける論理回路37と、クロック信号40に同期して論理回路37の出力信号を取り込むフリップフロップ回路35とを含み、クロック信号40の立ち上がりエッジ位置を調整し、フリップフロップ回路32の出力信号とフリップフロップ回路35の出力信号とが所定の組合せとなったときの、調整したクロック信号40の立ち上がりエッジ位置とクロック信号39の立ち上がりエッジ位置とに基づいてチップの性能を判別する。

(もっと読む)

PLL回路

【課題】ハイブリッド制御方式PLL回路の定常状態における位相ジッタを低減する。

【解決手段】ハイブリッド制御方式PLL回路内の位相比較回路PHASE_COMPの出力S_PHが頻繁に変化しているか否かを判定する定常状態検出回路CONV_DETを設け、位相比較回路の出力S_PHが暫く変化していない時は定常状態に達していないと判定し、頻繁に変化している時は定常状態に達したと判定し、その判定結果に基づいて、電圧制御発振回路VCOの発振周波数をデジタル制御信号S_DGによって制御する制御幅を変更し、もしくは(および)、アナログ制御信号S_AGを変化させる頻度を変更する。これにより、定常状態に達する前の収束性を損なうことなく、定常状態に達した後のデジタル制御信号による発振周波数の制御幅を小さくできる。よって、定常状態における位相ジッタを低減できる。

(もっと読む)

パルス信号遅延回路及びLED駆動回路

【課題】 LED回路を精度良く時差駆動できるように、デューティー比を維持して入力パルス信号を一定の遅延時間で正確に遅延可能なパルス信号遅延回路を提供する。

【解決手段】 入力パルス信号Sinの立ち上がりエッジを検出し、該検出タイミングを一定の遅延時間ずつ所定の遅延回数遅延させた第1エッジ検出遅延タイミングを順次出力する第1遅延タイミング信号Sdt1を生成する第1パルスエッジ遅延回路10、入力パルス信号Sinの立下りエッジを検出し、該検出タイミングを一定の遅延時間ずつ所定の遅延回数遅延させた第2エッジ検出遅延タイミングを順次出力する第2遅延タイミング信号Sdt2を生成する第2パルスエッジ遅延回路20、第1及び第2遅延タイミング信号から、夫々同じ回数遅延した第1及び第2エッジ検出遅延タイミングで立ち上がり、立ち下がる遅延パルス信号を各別に出力する遅延パルス信号生成回路30を備える。

(もっと読む)

クロック生成回路およびその使用方法

【課題】基準信号の周波数を逓倍又は分周したクロック信号を生成するクロック生成回路において、一つの基準信号から任意周波数のクロック信号を発生可能とする。

【解決手段】クロック生成回路1は、リング状に連結したm個の遅延素子DUからなるパルス遅延回路10と、各遅延素子DUから順次出力される通過信号P1〜Pmに基づき、基準信号CKIの周期を遅延素子DUでの遅延時間を単位として表した周期データDTを生成する周期測定部20と、除数又は乗数として使用される設定値MNを格納する設定値レジスタ50と、周期データDTに、設定値MNを乗・除してクロック信号の出力周期を表す制御データCDを生成する制御部30と、制御データCDと通過信号P1〜Pmとに基づき、基準信号CKIを分周又は逓倍したクロック信号CKOを出力する出力部40とを備え、実数で表された設定値MNを用いる。

(もっと読む)

クロック信号生成回路、及びクロック信号生成回路の使用方法

【課題】リングオシレータを利用して基準クロック信号の周波数を逓倍した逓倍クロック信号を生成するクロック信号生成回路において、逓倍クロック信号のジッタを抑制する。

【解決手段】高速クロック発生回路2の主要部であるリングオシレータへの電源供給を時定数がτに設定されたローパスフィルタ23を介して行い、高速クロック信号CKrで基準クロック信号CKs(周波数fs)の周期をカウントする周期カウンタ4のカウント値(周期カウント値)DGを、基準クロック信号CKsに従って動作する逓倍クロック生成回路5が、nクロック周期で、逓倍クロック信号CKoに反映させる。そして、基準クロック発生回路3は、周波数fsがτ>n/fsを満たす基準クロック信号CKsを発生させる。

(もっと読む)

信号伝達回路

【課題】新たな構成で複数種類の入力信号を1つのトランスを介して入力側から出力側へ伝達することが可能な信号伝達回路を提供することを目的とする。

【解決手段】温度入力信号が立ち上がると、トランス4の1次側コイルに第1のパルス電圧を発生させ、温度入力信号が立ち下がると、1次側コイルに第2のパルス電圧を発生させる1次側回路2と、トランス4の2次側コイルに第1のパルス電圧に対応するパルス電圧が発生すると、温度出力信号を立ち上がらせ、2次側コイルに第2のパルス電圧に対応するパルス電圧が発生すると、温度出力信号を立ち下がらせる2次側回路3とを有して信号伝達回路1を構成し、FAIL入力信号が立ち上がると、1次側コイルに第3又は第4のパルス電圧を発生させ、2次側コイルに第3又は第4のパルス電圧に対応するパルス電圧が発生すると、FAIL出力信号を立ち上がらせる。

(もっと読む)

ノイズフィルタ回路、デッドタイム回路、遅延回路、およびその方法、ならびに、サーマルヘッドドライバ、サーマルヘッド、制御回路、電子機器、および印刷システム

【課題】 簡易な構造を有するノイズフィルタ回路等を提供する。

【解決手段】 ノイズフィルタ回路(10;60;80;100)は、入力信号(IN)に基づく信号を入力する第1のインバータ回路(12;62;82;102)と、入力信号(IN)に基づく信号を入力する第2のインバータ回路(14;64;84;104)と、第1および第2のインバータ回路(12、14;62、64;82、84;102、104)からの信号に基づく信号を、セット信号(S)及びリセット信号(R)として入力するラッチ回路(16;66;86;106)と、を備える。第1および第2のインバータ回路(12、14;62、64;82、84;102、104)のそれぞれは、第1および第2の導電型のトランジスタを含み、第1および第2の導電型のトランジスタの一方の能力は、第1および第2の導電型のトランジスタの他方の能力より低い。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】従来型のクロック信号生成回路は回路規模が大きく製造コストが高くなる。

【解決手段】遅延同期ループ型のクロック信号生成回路を、第1のクロック信号を遅延して第2のクロック信号を生成するディジタル型の遅延線路と、ディジタル型の遅延線路の遅延時間長を、各段のフリップフロップ出力により設定するリング型シフトレジスタと、第1のクロック信号と前記第2のクロック信号の位相関係に基づいて、リング型シフトレジスタに対するシフトクロックの供給を制御する遅延量制御部とで構成する。

(もっと読む)

201 - 220 / 417

[ Back to top ]