Fターム[5J039KK13]の内容

Fターム[5J039KK13]に分類される特許

141 - 160 / 417

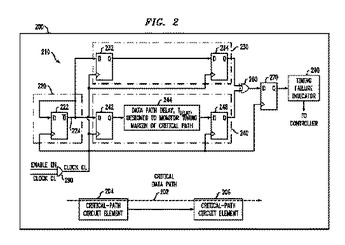

性能監視用クリティカルパス回路

目標タイミング・マージンを有する、クリティカルパス中のタイミングを監視する監視回路を含む集積回路が、開示される。監視回路は、2つのシフト・レジスタを含み、シフト・レジスタの1つは、受領信号に遅延値を加える遅延素子を含む。2つのシフト・レジスタの入力部は、入力信号を受領することができる信号入力ノードを形成する。監視回路は、出力部および少なくとも2つの入力部を有する論理ゲートも含み、各入力部は、2つのシフト・レジスタの出力部の対応する1つに接続される。論理ゲートの出力部は、目標タイミング・マージンが満足されるか、または満足されないかを示す。  (もっと読む)

(もっと読む)

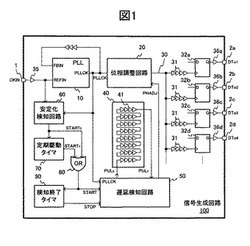

信号生成回路

【課題】 プロセス要因で生じるクロック信号の位相バラツキを抑える。

【解決手段】 信号生成回路100は、クロック信号PLLCKが通るクロック信号線30に1以上のクロックバッファ31が配置され、1以上のクロックバッファ31によりクロック信号PLLCKを遅延させ、遅延したクロック信号に基づき所定の信号を生成する。この信号生成回路100は、前記クロックバッファ31と同一チップ上に形成された複数のクロックバッファ41を有して構成される参照用クロックバッファ40と、参照用クロックバッファ40の遅延量を検知し、この遅延量と予め定められた遅延量との差に基づく位相調整信号PHADJを出力する遅延検知回路50と、位相調整信号PHADJに応じて、クロック信号PLLCKの位相を変える位相調整回路20と、を備える。

(もっと読む)

クロック生成回路

【課題】広帯域の周波数範囲におけるどの周波数の基準クロックを受けてもロックする時間を短くできるクロック生成回路を簡易な回路構成で実現。

【解決手段】基準クロックを第1の個数の電圧制御遅延素子12−1〜12−Nで遅延させて第1の遅延クロックを生成し、第2の個数の電圧制御遅延素子12−1〜12−Kで遅延させて第2の遅延クロックを生成する遅延部11と、前記基準クロックの位相と前記第1の遅延クロックの位相とを比較する位相比較部21と、遅延制御電流を出力するチャージポンプ22と、遅延制御部23と、前記基準クロックの位相と前記第2の遅延クロックの位相とを比較し、前記基準クロックと前記第1の遅延クロックとの位相差を判定する判定部13aと、前記位相差が閾値より大きい場合、前記遅延制御電流が第1の値になり、前記閾値以下の場合、前記第1の値より小さい第2の値になるように制御するチャージ制御部13bとを備える。

(もっと読む)

スイッチトキャパシタ回路を含む装置

【課題】スイッチトキャパシタ回路の各接続状態におけるセトリング時間の相違に応じたクロック(スイッチのオン/オフ信号)を生成することを可能とすること。

【解決手段】本発明による装置1は、第1及び第2のスイッチのオン/オフ切替により第1及び第2の接続状態を形成するスイッチトキャパシタ回路20と、クロック信号に基づいて、前記スイッチトキャパシタ回路の前記第1及び第2のスイッチのそれぞれ用に、互いにオーバラップしない第1及び第2のオン/オフ信号を生成するノンオーバーラップクロック発生器10とを備え、前記ノンオーバーラップクロック発生器は、前記第1及び第2のオン/オフ信号が互いに異なる第1及び第2のデューティを有するように、前記第1及び第2のオン/オフ信号を生成することを特徴とする。

(もっと読む)

パルス発生装置

【課題】良好な信号レベルのパルス信号を効率よく発生するのに好適なパルス発生装置を

提供する。

【解決手段】パルス発生装置100を、CLK信号の入力に応じて起動開始信号D0と、

D0を反転したXD0とを出力する起動開始信号生成回路20と、起動開始信号の入力に

応じてパルス信号を発生する、各々の信号出力部が独立した第1〜第Nのパルス発生回路

21_1〜21_Nと、第1〜第Nのパルス発生回路21_1〜21_Nのうちパルス信

号を出力する予定の一部の回路の信号出力部を順次選択して、該選択した信号出力部を共

通の信号出力線に接続し、残りのパルス発生回路の信号出力部を共通の信号出力線から電

気的に切断する選択回路22とを含む構成とした。

(もっと読む)

周波数シンセサイザ

【課題】不要波成分の出力を抑圧することができる周波数シンセサイザを得ることを目的とする。

【解決手段】不要波抑圧回路10が、クロック信号源1により生成されたクロック信号に同期して、デジタル振幅データ生成回路2により生成された振幅信号A2に応じた波形のアナログ信号B2を生成して、そのアナログ信号B2をクロック周波数fckで90度の位相量だけシフトし、位相シフト後のアナログ信号B2とMN−DAC3から出力されたアナログ信号B1を合成する。

(もっと読む)

クロック生成装置、集積回路装置、電子機器及びクロック生成方法

【課題】故障検出率の向上を図る一方で、通常動作時において低消費電力化を実現できるクロック生成装置、集積回路装置、電子機器及びクロック生成方法を提供する。

【解決手段】複数のFFと、前記FFを構成する2つのFFの間に挿入された組み合わせ回路と、該組み合わせ回路の所定のノードをプローブする1又は複数のプローブ用FFとを含む回路ブロックに対し、クロックを生成するクロック生成装置は、基準クロックの位相を調整して位相調整クロックを生成する位相調整回路と、第1の動作モードにおいて、前記位相調整回路への前記基準クロックの入力を停止するクロック停止制御回路とを含み、前記第1の動作モードにおいて前記基準クロックを前記FFに出力し、第2の動作モードにおいて前記基準クロックを前記FFに出力すると共に、前記位相調整クロックを前記1又は複数のプローブ用FFに出力する。

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

半導体集積回路装置

【課題】DLL回路においてロックはずれが発生しても、短時間で確実に正常ロック状態に復帰させる。

【解決手段】遅延回路13の遅延時間が1周期より小さくなると、遅延検出回路15から最小遅延時間検出信号K2が出力される。さらに位相周波数比較器11がUPパルスを出力していると、最小遅延時間検出信号K2とUPパルスとの2NOR論理(否定論理和回路21)によりクロックがUPパルスカウンタ19に伝達し、Hレベルのロックはずれ検出信号K3が出力され、リセット期間保持カウンタ17にLレベルが入力される。これにより、リセット期間保持カウンタ17がカウンタ動作を開始し、所定の期間、リセット信号をLレベルにして制御電圧CNTLを電源電圧にショートし、かつ位相周波数比較器11をリセットする。

(もっと読む)

位相比較器、PLL回路、及び位相比較器の制御方法

【課題】電圧制御発振器VCOの出力信号と参照信号との位相差をデジタル信号として高精度に検知できる位相比較器、PLL回路、及び位相比較器の制御方法を提供する。

【解決手段】各々複数段縦列接続され、基準信号および対象信号が入力される遅延回路と、各々の段の遅延時間の差により、基準信号と対象信号との位相差を出力する保持回路と、その出力結果を元に、遅延素子の時間差及び大小を変更する論理回路とを備えた。

(もっと読む)

半導体集積回路装置および遅延路の制御方法

【課題】電力効率を向上させる。

【解決手段】クロック信号CLKに同期して動作する2つの同期動作回路11、12間を並列形態で接続して信号伝送可能とされる複数の遅延路13a、13b、・・13nと、複数の遅延路13a、13b、・・13nにおけるそれぞれの遅延時間を検出する遅延検出部14と、遅延検出部14の検出結果に基づいて複数の遅延路13a、13b、・・13nの内の一の遅延路を選択し、選択した一の遅延路以外における信号伝送を阻止するように制御する制御部15と、を備える。

(もっと読む)

DLL回路及びその制御方法

【課題】本発明は、短いロッキングタイムを有する多相DLL回路及びその制御方法を提供する。

【解決手段】本発明のDLL回路は、 基準クロックを遅延させてDLLクロックを生成するが、制御電圧のレベルに応じて遅延量を調整する遅延手段;制御電圧の初期レベルを制御し、検出イネーブル信号を生成する初期動作制御手段;及び、検出イネーブル信号に応じて前記基準クロック及びDLLクロックの位相を比較して、制御電圧を生成する遅延制御手段を含むことを特徴とする。

(もっと読む)

PLL(PHASELOCKEDLOOP)回路内のチャージポンプリークに起因した制御電圧リプルを最小化する技術

【解決手段】位相ロックループ回路を含む装置においてチャージポンプリーク電流の影響を和らげるようループフィルタのサンプリング間隔を適切に制御する技術を提供する。一態様において、装置は電圧制御発振器(VCO)、位相周波数検知部(PFD)、VCOを固定するための制御電圧を提供するループフィルタ、及びUPパルスDOWNパルスの少なくともいずれか1つに応じてループフィルタに出力信号を供給するよう構成されたチャージポンプを含む。ループフィルタの入力とチャージポンプの出力との間で結合されサンプリング間隔によって特徴付けられたスイッチを含む。サンプリングスイッチ制御部は位相比較動作の前にスイッチを閉じ位相比較動作が完了するとスイッチを開くことでチャージポンプからのリーク電流の影響を和らげるようサンプリング間隔幅を適切に制御するよう構成される。 (もっと読む)

デューティ感知回路およびこれを備えるデューティ補正回路

【課題】デューティ補正回路のロッキングタイムを減らし、正確なデューティの補正が可能となり、多様な周波数のクロックについてデューティ補正を可能にするデューティ補正回路を提供すること。

【解決手段】本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、前記出力クロックのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、前記差異値を累積して前記デューティ調節コードを生成する累積部130とを備える。

(もっと読む)

半導体装置、内部信号タイミング回路、及び遅延時間測定方法

【課題】内部信号のタイミングを測定する場合、チップ内に形成されたトランジスタ等の素子における場所依存性によって特性が異なる場合にも、内部信号のタイミングを測定できる測定回路を提供する。

【解決手段】内部で実信号として用いられる第1及び第2の内部回路制御信号を生成する内部回路と、内部回路を通して受信される第1及び第2の内部回路制御信号を遅延時間測定開始信号及び遅延時間測定終了信号として受け、当該遅延時間測定開始信号及び遅延時間測定終了信号間の遅延時間を測定し、出力する遅延時間測定回路を備えた内部信号タイミング回路及び当該回路を含む半導体装置。

(もっと読む)

モード設定回路及びそれを用いたカウンタ回路

【課題】本発明は多種の時短モード設定が可能なモード設定回路及びそれを用いたカウンタ回路を提供することを目的とする。

【解決手段】外部から供給されるパルス信号によりトリガされる縦続接続された複数段のフリップフロップ13,14と、複数段のフリップフロップそれぞれの出力信号を演算して複数種類のモード信号を生成する論理回路15〜19とを有する。

(もっと読む)

半導体装置

【課題】PVT変動による遅延制御回路の遅延量変動を正しく補正する。

【解決手段】互いに動作条件が異なる第1及び第2の遅延素子列121,122と、第1及び第2の遅延素子列121,122に同時に入力されたパルス信号Pの伝搬速度差を検出する検出回路123と、検出回路123による検出結果に基づいて選択信号SELを生成する設定回路124とを備える。選択信号SELは、基準信号を遅延させることによって動作タイミング信号を生成する遅延制御回路130に供給され、その遅延量は選択信号SELによって調整される。これにより、PVT変動を見越して遅延制御回路の遅延量を大きく設計しておく必要がなくなるため、パフォーマンスの低下を防止することが可能となる。

(もっと読む)

電源検出回路

【課題】電源ノイズに起因する誤信号の出力を確実に抑制しつつ回路面積を削減する。

【解決手段】比較回路50は電源出力回路10の出力電圧Aを基準電圧回路20による基準電圧Bと比較し、電源電圧が所定電圧以下の場合は電源未検出信号を出力し、電源電圧が所定電圧よりも高いときは電源検出信号を出力する。基準電圧判別回路60は基準電圧が安定状態にあるか否かを判別し、安定状態にあるときには安定信号を出力し、安定状態にないときには不安定信号を出力する。出力固定回路70は不安定信号を入力したときには比較回路の出力信号を電源未検出時の出力である電源未検出信号に固定化し、安定信号を入力したときには固定化を停止する。ノイズ除去回路80は遅延回路90を内蔵し、その遅延作用により出力固定回路の出力信号に重畳しているノイズを除去する。そして、遅延回路90は、基準電圧回路の内部所定部位の電流値を参照して遅延信号を生成する。

(もっと読む)

低電力非同期カウンタ及び方法

【解決手段】低電力非同期カウンタの設計技術。典型的な実施形態では、複数のフリップフロップのクロック入力及び信号出力が、非同期カウント構造を実現するように直列に連結される。複数のフリップフロップの信号出力は、参照信号の順次遅延されたバージョンによってサンプリングされる。更に、参照信号の順次遅延されたバージョンを生成する設計方法が開示される。典型的な実施形態では、非同期カウント技術は、デジタル位相ロックループ(DPLL)の高速カウンタに使用され得る。 (もっと読む)

同期検出回路、これを用いたパルス幅変調回路、及び同期検出方法

【課題】部品点数の削減、高い検出精度の確保、処理速度低下の防止等を図る。

【解決手段】位相ロックループ回路15により、基準クロック信号に基づいて互いに位相が異なる複数相の多相クロック信号を生成する多相クロック生成回路11と、前記多相クロック信号の中から、同期信号に同期するクロック信号を特定する同期クロック特定回路12とを有する同期検出回路2であって、前記多相クロック生成回路11は、前記基準クロック信号を逓倍した周波数を有する高速多相クロック信号と、前記高速多相クロック信号を分周した周波数を有する低速多相クロック信号とを生成し、前記同期クロック特定回路は、同期信号と前記高速多相クロック信号との比較結果と、前記同期信号と前記低速多相クロック信号から選択された代表クロック信号との比較結果とに基づいて、前記同期信号の同期位置を示す同期位置信号を生成する。

(もっと読む)

141 - 160 / 417

[ Back to top ]