Fターム[5J039KK14]の内容

Fターム[5J039KK14]に分類される特許

1 - 20 / 81

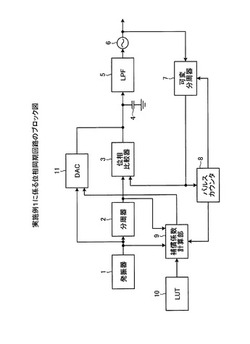

位相同期回路及び位相同期回路制御方法

【課題】少ない分周数を用いた小数点以下の分周における位相の同期を精度良く行う位相同期回路及び位相同期回路制御方法を提供する。

【解決手段】位相比較器3は、基準クロックと比較クロックとの位相差を電流に変換して出力する。キャパシタ4は、位相比較器3から入力された電流に応じて電圧を出力する。VCO6は、キャパシタ4から入力された電圧によって出力周波数を制御し、当該出力周波数を有する信号を出力する。可変分周器7は、VCO6から出力された信号を所定の周期で異なる値に分周することで、小数点以下の値を有する分周を行なった比較クロックを生成する。パルスカウンタ8は、可変分周器7から出力された比較クロックの数をカウントする。補償係数計算部9は、パルスカウンタ8のカウント数を基に、キャパシタ4に対する電流及び電圧の補償値を取得する。DAC11は、前記補償値を基に、キャパシタ4に対して電流を流し補償を行う。

(もっと読む)

位相比較装置

【課題】ステップ応答収束時間だけ待つ必要なく積分値を抽出し、また、入力信号の周波数が既知でなくても抽出した積分値に応じて位相差を演算する位相比較装置を得る。

【解決手段】分周器4が入力信号の周波数を2分周し、積分器5が排他的論理和回路3により生成されたパルスを分周器4により設定された周期分積分し、基準積分器7が既知の一定レベルの基準信号を分周器4により設定された周期分積分し、信号処理部10が積分器5および基準積分器7による積分値に応じて位相差を演算するように構成したので、入力信号の周波数の1/2倍の周波数の整数倍の周波数にヌル点のできるsyncフィルタ特性が形成されることを利用し、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。また、2つの入力信号の周波数が既知でなくても、2つの入力信号の位相差を演算することができる。

(もっと読む)

信号生成装置及び周波数シンセサイザ

【課題】PLLを用いた周波数シンセサイザにおいて、簡素な構成でありかつスプリアス特性が良好であること。

【解決手段】位相比較部に入力する参照周波数信号を、ディジタル信号からなる鋸波のゼロクロスポイントを検出したときのクロックに基づいて生成する。しかしこの場合ディジタル値が飛び飛びの値であることから正負の符号が逆転するときにディジタル値がゼロとなるとは限らない。そこで前記ディジタル値が徐々に変化する領域において正、負の符号が逆転するゼロクロス時の直前のディジタル値及び直後のディジタル値を読み出したクロック信号を夫々P1及びP2とし、クロック信号P2の次のタイミングのクロック信号をP3とすると、P1とP2で読み出されるディジタル値の比率に対応する比率でP1、P3を使用する。

(もっと読む)

エッジ検出回路

【課題】入力信号のパルス幅やタイミングに影響されず、且つ1つのエッジ検出に対し複数個の検出信号が出力される懸念を払拭したエッジ検出回路を提供する。

【解決手段】入力信号の立ち上がりエッジを検出するとノードN1をロウレベルに変化させる初期化機能付きのD型フリップフロップFF1と、ノードN1がロウレベルのときノードN2と電源端子間をオンさせるMP1と、ノードN1がハイレベルのときノードN2と接地との間をオンさせるMN1と、ノードN2に入力側が接続されノードN3に出力側が接続されたインバータINV3と、ノードN3に入力側が接続されノードN4に出力側が接続されたINV4と、ノードN2とN4の間に接続されたC1とを備え、ノードN3がロウレベルになるとD型フリップフロップFF1が初期化され、ノードN1がロウレベルになってからノードN3がロウレベルになるまでのパルス幅のエッジ検出信号を出力する。

(もっと読む)

PLL回路

【課題】 電源起動からロックまでの時間を短くすると共に、電源断時に電荷を速く放電できるPLL回路を提供する。

【解決手段】 位相の進み/遅れを検出器11で検出し、位相の進み/遅れに相当する信号を積分器12で積分し、起動パルス生成部13が、電源起動を検出し、ロックまでの時間に基づいたパルス幅のパルスをLPF5と積分器12に出力し、LPF5と積分器12が、起動パルス生成部13からのパルスによって内部のコンデンサを充電すると共に電源断で内部のコンデンサに蓄積された電荷を放電するPLL回路である。

(もっと読む)

ゲート駆動回路及び半導体装置

【課題】応答性を損なうことなく能動クランプ素子の損失電力を低減できる能動クランプ回路を用いたゲート駆動回路及び半導体装置を提供する。

【解決手段】スイッチ素子Tr7のゲートを駆動するゲート駆動回路であって、制御信号に基づいてスイッチ素子Tr7を駆動する駆動部(トランジスタTr1,Tr2,Tr4,Tr5)と、スイッチ素子Tr7の第1主端子(ドレイン)と第2主端子(ソース)との間に印加される電圧が所定電圧以上の場合に、駆動部によるスイッチ素子Tr7に対する駆動動作を強制的に遮断して、スイッチ素子Tr7の第1主端子と第2主端子との間の電圧がクランプされるようにスイッチ素子Tr7を駆動するアクティブクランプ回路(ダイオードD1、ツェナーダイオードZD1、抵抗R1、トランジスタTr3,Tr6)とを備える。

(もっと読む)

ピークホールド回路のリセット装置

【課題】安価な構成で適切なタイミングにリセット信号を出力させる。

【解決手段】A/D変換回路3からデジタル信号として入力されるホールドコンデンサCのホールド電圧の電圧レベルの増加を検出したときに、増加前後の電圧レベルの差をコンパレータ5aによって求める。そして、求めた差が所定のしきい値以下である場合は、リセット信号を出力する。よって、入力信号Vinの入力に伴うホールドコンデンサCのホールド電圧の増加量が、ホールド電圧の飽和判断に適した所定のしきい値以下になった時点で、初めてホールドコンデンサCをリセットしてホールド電圧を放電させる。これにより、ホールドコンデンサCの1回目のチャージ時点におけるホールド電圧に比べてはるかに、入力信号Vinの反転信号の電圧レベルのピーク値に近い値にホールド電圧が達するまで、ホールドコンデンサCをチャージさせた時点で、リセット信号を確実に出力することができる。

(もっと読む)

故障または異常検出機能を有するパルス増幅装置およびパルス増幅器故障検出方法

【課題】小型化が可能な故障または異常検出機能を有するパルス増幅装置を提供すること。

【解決手段】本実施形態に係る故障または異常検出機能を有するパルス増幅装置は、入力されるパルスを増幅して出力するパルス増幅器11と、パルス増幅器11の入力端子に接続され、パルス増幅器11に入力されるパルスに同期したパルス増幅器11を動作させる制御信号を形成して、この制御信号を入力端子に入力するパルス増幅器制御回路12と、パルス増幅器制御回路12に接続され、制御信号を連続波に変換する平均化回路17と、平均化回路17に接続され、平均化回路17から出力された連続波の電圧Vgaveとしきい値電圧Vsとを比較する比較回路18と、比較回路18に接続され、比較回路18から出力される差分電圧(Vgave−Vs)に基づいて、パルス増幅器11の故障、あるいはパルス増幅器制御回路12の異常を検出する警報装置23と、を具備する。

(もっと読む)

半導体集積回路及びノイズ耐性検査方法

【課題】半導体集積回路のノイズ除去機能の特性を正確に測定することができる半導体集積回路及びノイズ耐性検査方法を提供する。

【解決手段】半導体集積回路1Aは、入力信号IN中のノイズ成分の振幅を減衰させてノイズ除去信号OUTを出力する入力バッファ11と、ノイズ除去信号OUTの論理レベルが変化したときに、この論理レベルの変化に応じて論理信号をラッチする論理回路12,13とを備える。

(もっと読む)

半導体装置および制御回路

【課題】実動作時における内部クロック信号のジッタ量を検出し、検出したジッタ量を外部で利用可能に出力できる半導体装置を得ること。

【解決手段】クロック生成回路が出力しているクロック信号と、該クロック信号を少なくとも1周期遅延した遅延クロック信号との位相差に基づき前記クロック信号に含まれるジッタ成分を検出するジッタ検出部と、前記検出されたジッタ成分を電圧信号に変換する増幅回路を有する増幅部と、前記変換された電圧信号を外部へ出力するためのジッタ出力端子とを備えたことを特徴とする。

(もっと読む)

周波数−電圧変換回路及び半導体集積回路装置

【課題】リニアリティ(直線性)の良好な周波数−電圧変換回路を提供すること。

【解決手段】周波数−電圧変換回路は、クロック信号を受信する微分回路と、微分回路の出力を受けてパルス波として出力するバッファ回路と、バッファ回路から出力されたパルス波を直流電圧に変換する積分回路と、クロック信号をゲート端子で受信するとともに、ソース端子が接地端子に接続され、ドレイン端子が微分回路の出力端子に接続されたMOSトランジスタと、を備えている。

(もっと読む)

発振停止検出回路

【課題】保護継電器や監視制御機器の発振回路が停止したときに、発振停止検出回路を安価に構築する。

【解決手段】本発明の発振停止検出回路は、発振回路がクロックの供給の停止を検出するために、クロック信号の変化を検出する微分回路と、微分回路からの信号を立ち上がりに限定するダイオードと、前記出力信号を整形する、パルス整形回路とインバータ回路と、充放電回路と、充放電回路の出力電圧レベルと所定の基準値を比較して、基準値を超えたときに信号出力をすることを特徴とする。

(もっと読む)

積分回路

【課題】入力電圧に応じて差動増幅回路のチョッピングによるオフセット誤差が悪化していた。

【解決手段】第1のクロック信号をチョッピング用クロック信号に用いることで、差動対を構成するトランジスタのしきい値電圧のオフセットによる入力オフセットを低減する第1の差動増幅器と、前記第1の差動増幅回路の反転入力端子、非反転入力端子に接続される第1、第2の入力端子と、前記第1の差動増幅回路の反転入力端子と、前記第1の差動増幅回路の出力端子との間に接続される第1の容量と、を有する積分回路であって、前記第1、第2の入力端子間の電位差に応じて、前記第1の差動増幅回路に入力する前記第1のクロック信号の周波数を変化させる積分回路。

(もっと読む)

画像形成装置、画像形成方法、及びプログラム

【課題】消費電力増加を抑制した画像形成装置、画像形成方法、及びプログラムを提供する。

【解決手段】上位装置からの印刷データを受信し、印刷する画像形成装置であって、コントローラが省エネ復帰信号を省エネ制御コントローラに出力した際は復帰要因送信ビットに“1”を立て、MAIN CPUが省エネ状態から復帰した後、復帰要因送信ビットが“1”ならば処理は行わず、復帰要因送信ビットが“0”ならば入力された全てのノイズの特性から最適なノイズキャンセル回路の設定値を計算し、設定変更するようにした。

(もっと読む)

電子回路、表示装置、及び電子機器、並びに電子回路の駆動方法。

【課題】順序回路の入力信号及び出力信号の状態を制御し、電子回路の動作不良を抑制する。

【解決手段】順序回路及び制御回路を有する電子回路であり、順序回路は、スタート信号として第1の信号、クロック信号として第2の信号、リセット信号として第3の信号が入力され、入力された第1の信号、第2の信号、及び第3の信号の状態に応じて設定された状態の第4の信号を出力信号として出力し、制御回路は、順序回路に入力される第3の信号の状態を制御する。

(もっと読む)

ピークホールド形検波回路

【課題】RPIが大きく変動しても出力電圧の変動が少ない、ピークホールド形検波回路を提供すること。

【解決手段】本発明の一例のピークホールド形検波回路によれば、検波される高周波パルスが入力される入力端子にアノード端子を接続された検波ダイオードと、この検波ダイオードのカソード端子と接地間に接続されたキャパシタと、前記検波ダイオードのカソード端子に一端を接続されたスイッチ回路と、このスイッチ回路の他端と接地間に接続された放電用抵抗と、前記検波ダイオードのカソード端子に入力端子を接続され入力信号を積分する積分器と、前記高周波パルスに同期してこの高周波パルスよりも幅の広い制御用高周波パルスを前記スイッチ回路に制御信号として入力するスイッチ制御回路と、を有する。

(もっと読む)

サプライレギュレートされたフェイズロックループ(PLL)及び用いる方法

サプライレギュレートされたフェイズロックループ(PLL)が提供される。PLLは、サプライレギュレーティングループ、電圧制御発振器(VCO)、及びVCOのためのプログラマブルデカップリングキャパシタアレイを備える。VCOデカップリングキャパシタアレイのキャパシタンスは、NかけるCUNITに等しくなるように調整可能であり、NはN分周回路の乗算ファクタの現在の値であり、CUNITはデカップリングキャパシタアレイを製造するために選ばれたプロセス技術に対して特徴付けられたユニットキャパシタンスである。PLLが1つの周波数帯から他にスイッチするとき、VCOデカップリングキャパシタによって導入される高次ポールがPLL参照周波数をトラックし、PLLの動作安定性を改善する。  (もっと読む)

(もっと読む)

ブースト回路およびそれを用いたΔΣ変調器、電子機器

【課題】ブースト回路におけるビットエラーを防止する。

【解決手段】ビットストリーム信号BSINを受け、その振幅をブーストして出力するブースト回路100が提供される。第1クロックブースタ10aは、クロック信号CKを受け、その振幅をブーストする。第2クロックブースタ10bは、反転されたクロック信号CK#を受け、その振幅をブーストする。スイッチ22は、クロックブースタ10a、10bの出力信号CK’、CK#’を受け、ハイレベルである一方を選択する。第1キャパシタC1は、スイッチ22の出力端子にカップリングされる。レベルシフタ28は、ビットストリーム信号BSINのハイレベルを、第1キャパシタC1に生ずる電圧レベルにレベルシフトする。

(もっと読む)

信号発生装置

【課題】

積分回路や発振回路に、時間差なく各信号が入力され、さらには、積分回路や発振回路の補正や校正の自由度を高くする。

【解決手段】

複数のアナログ信号を入力し当該アナログ信号をそれぞれ積分した積分信号をそれぞれ出力する積分回路111,112と、各積分信号をそれぞれ入力し、積分信号の大きさを所定のしきい値と比較して比較信号をそれぞれ出力する比較回路121,122と、積分回路のうち少なくとも2つの積分回路の制御端子に接続され、それぞれセットされた時間だけ、他の少なくとも1つの積分回路の積分動作の開始タイミングと異なるタイミングで積分動作を開始させる遅延回路131,132と、比較信号を入力し、これらの入力信号の入力タイミングを比較し、これらの入力タイミングに応じた比較結果信号を出力する信号処理回路14とを備える。

(もっと読む)

デューティ比補正回路及びデューティ比補正方法

【課題】非同期信号のデューティ比を補正可能なデューティ比補正回路を提供すること。

【解決手段】本発明に係るデューティ比補正回路は、第1クロック信号が入力されるクロック用入力バッファと、補正信号に基づいて、前記クロック用入力バッファから出力される第2クロック信号のデューティ比を調整して第3クロック信号を生成するクロック用デューティ調整回路と、第1データ信号が入力されるデータ用入力バッファと、前記補正信号に基づいて、前記データ用入力バッファから出力される第2データ信号のデューティ比を調整して第3データ信号を生成するデータ用デューティ調整回路と、前記第3クロック信号に基づいて、前記補正信号を生成するデューティ比較回路と、を備えるものである。

(もっと読む)

1 - 20 / 81

[ Back to top ]