Fターム[5J039KK18]の内容

Fターム[5J039KK18]に分類される特許

1 - 20 / 237

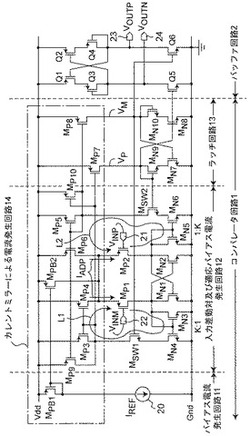

コンパレータ回路

【課題】コンパレータ回路において、従来技術に比較して高速で消費電力を低下させる。

【解決手段】入力される2つの入力電圧に応じて、第1及び第2のMOSトランジスタからなる入力差動対のいずれか1つのMOSトランジスタにおいて、当該1つのMOSトランジスタとスイッチトランジスタとを含むループにより適応バイアス電流を発生する入力差動対及び適応バイアス電流発生回路と、上記適応バイアス電流に対応する電流を検出してラッチ論理を変化させた後、上記スイッチトランジスタをオンからオフに切り換えることにより上記適応バイアス電流を遮断するラッチ回路とを備える。

(もっと読む)

電圧比較回路,A/D変換器および半導体装置

【課題】比較器に対して最適な同相電圧を与えることによって、動作速度の向上を図る。

【解決手段】比較器1と、前記比較器の応答速度を判定する判定器2と、前記判定器の判定結果に従って、前記比較器の応答速度の遅延を低減するように、前記比較器の複数の入力における同相電圧を制御する電圧制御器3と、を有し、電圧比較回路100は、電圧比較器(比較器)1,判定器2および電圧制御器3を有する。比較器1は、差動の入力信号Vip,Vimの高低を比較し、判定器2は、比較器1の動作の遅速を判定して電圧制御器3を制御し、電圧制御器3は、判定器2の出力に従って、入力信号Vip,Vimの同相電圧(コモン電圧)を制御する。なお、クロック発生器200は、電圧比較回路100における比較器1および判定器2に対するクロックを発生する。

(もっと読む)

位相検出回路及び検査方法

【課題】入力信号の位相の同相/反転関係を検出する位相検出回路であって、検出可能な信号速度が制限されることを回避することが可能な位相検出回路を提供する。

【解決手段】ギルバートセルと、このギルバートセル内の下段側に位置する第1の差動対(101、102)に対して並列関係に設けられた第2の差動対(120、121)と、第1の差動対に電流を供給する第1の電流源(100)とは別に設けられ、第2の差動対に電流を供給する第2の電流源(130)と、第1の電流源と第2の電流源とのいずれかのみが動作するように制御する制御回路(140)とを備え、第1の電圧信号は第1の差動対の正側電圧入力端子と第2の差動対の負側電圧入力端子に入力され、第1の電圧信号と相補の関係にある第2の電圧信号は第1の差動対の負側電圧入力端子と第2の差動対の正側電圧入力端子に入力されている位相検出回路。

(もっと読む)

コンパレータ回路

【課題】プルアップ抵抗の抵抗値や接続する外部回路に依存せず、ハイレベル出力電圧を所望の電圧に精度よく設定することが可能なコンパレータ回路を提供する。

【解決手段】オープンドレイン型またはオープンコレクタ型のコンパレータ2と、一端がコンパレータ2の出力端子5に電気的に接続されたプルアップ抵抗RLと、反転入力端子11がコンパレータ2の出力端子5に電気的に接続され、出力端子12がプルアップ抵抗RLの他端に電気的に接続され、非反転入力端子13にハイレベル出力電圧となる基準電圧V0が印加される増幅回路10と、を備えたものである。

(もっと読む)

インターフェイス回路

【課題】ホスト機器とサブ機器との間の双方向データ伝送を行うインターフェイス回路において、待機時の消費電流をゼロにする機能を実現し、かつ安定した起動シーケンスを実現する。

【解決手段】ホスト機器1側で、差動信号の電位は、アイドル/スタンバイ状態においてプルアップ素子4によって電源電位にプルアップされている。ノーマル状態に移行するとき、差動信号が出力されるにつれて、コモンモード電位が電源電位から徐々に低下していく。サブ機器2側では、レベル検知回路10によってコモンモード電位が所定レベルよりも下がったことを検知したとき、ノーマル状態になったと判断し、起動する。レベル検知回路10は、通常状態で消費電流が生じないバッファタイプの回路構成で実現される。

(もっと読む)

電気遅延型光クロック型トランジスタアレイ

【課題】PDの数を減らし、光遅延分岐回路を必要としない電気遅延型OCTAを提供すること。

【解決手段】伝送線路10に入力パラレル電気信号が入力されたスイッチ20−1〜20−Nが並列に取り付けられている。スイッチ20−1〜20−Nは、ノーマリオフ状態に設定されており、光電変換器30から出力され分岐した電気信号によってONされると伝送線路10に出力シリアル電気信号を構成する電気パルスを生成する。光電変換器30は光パルス又は光ラベルトリガーが照射されると電気信号を出力し、分岐回路40−1〜40〜N、遅延回路50−1〜50−(N−1)を介して各スイッチ20−1〜20−Nに入力する。遅延回路50−1〜50−(N−1)は分岐回路40−1〜40〜Nの間に設置されており、出力シリアル電気信号のビット間隔τに相当する時間差でスイッチ20−1〜20−Nに電気信号が到達するように調整されている。

(もっと読む)

信号変換回路、その信号変換回路を備えるアイソレータ回路及び信号変換方法

【課題】高い周波数の差動信号をシングルエンドの信号に変換可能な信号変換回路、当該信号変換回路を備えたアイソレータ回路及び信号変換方法を提供すること

【解決手段】本発明にかかる信号変換回路10は、差動信号である信号D1及び信号D2が入力されるヒステリシスコンパレータ1、2及び変換バッファ3を備える。ヒステリシスコンパレータ1は、信号D1の電位V1と信号D2の電位V2との大小の比較結果を信号E1として出力する。ヒステリシスコンパレータ2は、電位V1と電位V2との大小を比較し、当該比較結果を信号E1の反転信号である信号E2として出力する。変換バッファ3は、信号E1及び信号E2をシングルエンド信号Fに変換する。

(もっと読む)

差動入力インターフェース回路、表示ドライバIC、表示パネルモジュールおよび画像表示装置

【課題】高速に伝送されてくるデータを安定して受信する差動入力インターフェース回路を提供する。

【解決手段】一対の差動信号を受信して正相データ信号PA11を出力する第1の差動アンプ103と、一対の差動信号を受信して負相データ信号NA11を出力する第2の差動アンプ104と、一対の差動クロック信号を受信して正相クロック信号FX11を出力する第3の差動アンプ105と、正相データ信号PA11と負相データ信号NA11とを正相クロック信号FX11に同期してラッチすることにより、ラッチ出力信号PDを出力するデータラッチ回路303と、ラッチ出力信号PDよりシングルエンドのデータ信号L13を生成するデータ生成回路302とを備える。

(もっと読む)

半導体装置

【課題】入力信号と出力信号の位相差の増大を抑制すること。

【解決手段】本発明の半導体装置は、縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、リファレンス電位を基準として生成した出力電圧を、複数の遅延素子に供給する遅延素子用電源回路と、出力電圧がリファレンス電位の一定範囲内にあるか否かを検出し、出力電圧が一定範囲内にない場合、ロック調整動作を停止させるDLL動作信号をDLL回路に出力する検出回路と、を有する。

(もっと読む)

コンパレータ

【課題】安定したヒステリシス特性を有するコンパレータを提供する。

【解決手段】コンパレータ1は、一対の差動入力トランジスタT1,T2を有する差動回路部10と、差動回路部10にヒステリシスを付加するためのセレクタ回路部20と、レベル変換増幅部30とを備える。セレクタ回路部20は、差動入力トランジスタT1,T2のドレインにそれぞれ接続するトランジスタT3,T4を有し、トランジスタT3,T4の一方がオンするときオンしたトランジスタに接続する側のトランジスタT1,T2から一定のバイアス電流Ibを吸引するように接続される。レベル変換増幅部30の2つの増幅回路31,32は、セレクタ回路部20のトランジスタT3,T4に対して並列に接続されており、差動回路部10の出力に応じてトランジスタT3,T4の一方をオンし同時に他方をオフすることでバイアス電流Ibを切り換える。

(もっと読む)

制御回路及びこれを用いたデータ保持装置

【課題】セットの部品点数削減や低消費電力化を実現することが可能な制御回路及びこれを用いたデータ保持装置を提供する。

【解決手段】制御回路10は、トリガ信号TRIGGERに特定の信号パターンが現れたときに制御部11の動作に必要な内部クロック信号LCLKの生成を開始し、少なくとも制御部11において所定の処理が完了するまで内部クロック信号LCLKの生成を継続した後、内部クロック信号LCLKの生成を停止する内部クロック生成部12と、内部クロック信号LCLKを用いて前記所定の処理を実行する制御部11と、を有する。

(もっと読む)

コンパレータ、それを利用したスイッチングレギュレータの制御回路、スイッチングレギュレータ、電子機器

【課題】新規な出力論理を有するコンパレータを提供する。

【解決手段】コンパレータ100は、入力電圧VINを基準電圧VREFと比較する。差動増幅回路10は、その制御端子に基準電圧VREFが印加された第1入力トランジスタMi1と、その制御端子に入力電圧VINが印加された第2入力トランジスタMi2を含む。出力段20は、差動増幅回路10の出力信号Vxを受け、それに応じた信号を比較結果を示す出力信号SOUTとして出力する。フィードバック回路30は、出力段20の出力信号SOUTを受け、出力信号SOUTが第1レベルから第2レベルに遷移すると、出力信号SOUTが第2レベルに戻るように、差動増幅回路10または出力段20にフィードバックする。

(もっと読む)

多入力差動増幅器

【課題】各動作モードにおいてレベルシフト回路を用いることなく所望の入力電圧範囲となる多入力差動増幅器を提供する。

【解決手段】差動部1は、バイアス部2と出力部3との間に設けられ、第一入力部10と第二入力部20とを有する。第一入力部10は、ソースがバイアス部2と接続され、ドレインが出力部3と接続された1個のn型MOSFET(M11)からなる。第二入力部20は、直列接続される2個のn型MOSFET(M21)、(M22)と、直列接続される2個のn型MOSFET(M23)、(M24)とが2列に並列接続される。また、入力端INaはM11のゲートに接続され、入力端INxはM22とM23のゲートに接続され、入力端INyはM21とM24のゲートに接続される。バイアス部2は1つの定電流源21を有し、出力部3は2つのp型MOSFET(Q1、Q2)で構成のカレントミラー回路を有する。

(もっと読む)

ゲート駆動回路及び半導体装置

【課題】応答性を損なうことなく能動クランプ素子の損失電力を低減できる能動クランプ回路を用いたゲート駆動回路及び半導体装置を提供する。

【解決手段】スイッチ素子Tr7のゲートを駆動するゲート駆動回路であって、制御信号に基づいてスイッチ素子Tr7を駆動する駆動部(トランジスタTr1,Tr2,Tr4,Tr5)と、スイッチ素子Tr7の第1主端子(ドレイン)と第2主端子(ソース)との間に印加される電圧が所定電圧以上の場合に、駆動部によるスイッチ素子Tr7に対する駆動動作を強制的に遮断して、スイッチ素子Tr7の第1主端子と第2主端子との間の電圧がクランプされるようにスイッチ素子Tr7を駆動するアクティブクランプ回路(ダイオードD1、ツェナーダイオードZD1、抵抗R1、トランジスタTr3,Tr6)とを備える。

(もっと読む)

ピークホールド回路及びボトムホールド回路

【課題】ピークホールド回路及びボトムホールド回路の検出精度を高め、高温動作における当該回路の検出精度の劣化を抑制すること。

【解決手段】各ゲートに入力端子1と出力端子2が接続される第1の差動入力回路7と、第1のカレントミラー回路10を備える第1の差動増幅回路12と、第1のカレントミラー回路10に流れる電流I1に比例する充電電流I2を生成する第5のトランジスタ13と、ゲートが第1の差動増幅回路12の出力ノード16に接続され、ソースとドレインがそれぞれ第5のトランジスタ13のドレインとキャパシタ17に接続される第6のトランジスタ14と、充電電流I2を充電するキャパシタ17を備え、出力電圧VOUTが入力信号VINのピーク値に近づくに従って充電電流I2を減少させることで、ピークホールド回路の過剰の行き過ぎを抑制し、検出精度を高めた。

(もっと読む)

高速量子化器

【課題】高速量子化器および最適化された時間遅延を提供する。

【解決手段】高速量子化器コンパレータの装置と方法は、3部を含む:プリアンプ部、再生ラッチ部、およびデータラッチ部。時間遅延は、再生ラッチ出力の最初の電圧を変えることによって減少される。電流源はコンパレータの底部に提供され、時間遅延最適化を可能にする。PMOS同等化スイッチが停止されたとき、クロック信号をフィードスルーにし、出力に電荷の注入を提供する。これらの電荷によって、コンパレータの時間遅延が可変となる。リセット時間が比較時間より長いために、非常に低い電流が出力電圧を決定する。

(もっと読む)

ハイサイドスイッチ回路、インターフェイス回路、および電子機器

【課題】ハイサイドスイッチの過電流の検出精度を高めることが可能なハイサイドスイッチ回路、および、そのハイサイドスイッチ回路を含む装置を提供する。

【解決手段】ハイサイドスイッチ回路10は、入力端子11と出力端子12との間に電気的に接続されるスイッチ(MOSトランジスタ15)と、ゲート制御部16と、過電流検出部20とを備える。過電流検出部20は、抵抗素子21と、比較器22とを含む。比較器22は、抵抗素子21の電圧V1がしきい電圧を超える場合に、過電流を検出する。比較器22は、過電流時の検出電圧V1がしきい電圧を上回るように、予め調整される。抵抗素子21の抵抗値の精度が高くない場合にも、比較器22の調整によって、過電流の検出精度が高められる。

(もっと読む)

ルックアップテーブル回路およびフィールドプログラマブルゲートアレイ

【課題】動作速度の速いルックアップテーブル回路およびフィールドプログラマブルゲートアレイを提供する。

【解決手段】ルックアップテーブル回路1は、入力信号に基づいて複数の抵抗変化型素子の中から一つの抵抗変化型素子を選択する抵抗変化回路2と、抵抗変化回路2の最大抵抗値と最小抵抗値との間の抵抗値を有する参照回路4と、抵抗変化回路2の他端にソースが接続された第1のnチャネルMOSFET6と、参照回路の他端にソースが接続された第2のnチャネルMOSFET8と、第1のnチャネルMOSFET6のドレインを通して抵抗変化回路2に電流を供給する第1の電流供給回路10と、第2のnチャネルMOSFET8のドレインを通して参照回路4に電流を供給する第2の電流供給回路12と、第1のnチャネルMOSFET6のドレイン電位と第2のnチャネルMOSFET8のドレイン電位を比較する比較器14と、を備える。

(もっと読む)

ヒステリシスコンパレータ

【課題】ヒステリシスコンパレータの閾値の設定範囲を広げる。

【解決手段】一つの実施形態のヒステリシスコンパレータには、電流源2乃至4、比較増幅部10、基準電圧発生部21、カレントミラー回路23、Nch MOSトランジスタNMT3、Nch MOSトランジスタNMT4、Nch MOSトランジスタNMT6、Nch MOSトランジスタNMT8、Nch MOSトランジスタNMT9、端子Pvd、端子Pv1、端子Pin、端子Pvs、及び端子Poutが設けられる。

(もっと読む)

コンパレータ回路およびそれを用いた試験装置

【課題】コンパレータの遅延時間分散を低減する。

【解決手段】コンパレータ100は、入力電圧VINと基準電圧VREFを比較する。入力段10は、差動増幅器を含む。遅延回路20は、入力段10の出力信号S1を調節可能に遅延させる。遅延補償回路30は、入力段10におけるオーバードライブ電圧VODに応じて、遅延回路20の遅延量を制御する。遅延補償回路30は、差動増幅器の出力電圧をオーバードライブ電圧VODを示す信号として利用し、遅延回路20の遅延量τを制御する。

(もっと読む)

1 - 20 / 237

[ Back to top ]