Fターム[5J039KK19]の内容

Fターム[5J039KK19]に分類される特許

1 - 20 / 72

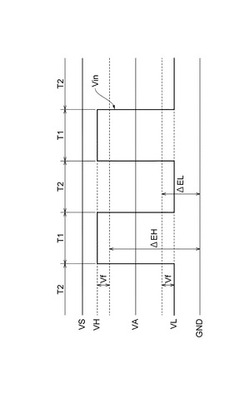

二値化回路

【課題】動作速度の低下を抑えつつ、ハイレベル及びローレベルの判定精度を高めることができる二値化回路を提供する。

【解決手段】二値化回路20は、ダイオード31及びコンデンサ32を有するピークホールド回路部30と、ダイオード41及びコンデンサ42を有するボトムホールド回路部40と、コンデンサ32とダイオード31との間のノードN1の電圧、及びコンデンサ42とダイオード41との間のノードN2の電圧の平均電圧VAと入力信号Vinの電圧とを比較して入力信号Vinを二値化する比較回路部70と、上記平均電圧VAに比例する電圧を出力する基準電圧生成回路部60とを備える。ボトムホールド回路部40は、基準電圧生成回路部60から出力された電圧を基準電位VSとして用いる。

(もっと読む)

パルス電力増幅装置

【課題】熱時定数による増幅利得の時間的な変化を補償でき、良好な直線性を有するパルス増幅装置を提供する。

【解決手段】パルス電力増幅装置10は、高周波信号を変調するパルス信号を入力され、前記パルス信号を入力され第1の増幅器の熱時定数に対応する時定数を有する第1の微分回路と、前記パルス信号を入力され第2の増幅器の熱時定数に対応する時定数を有する第2の微分回路と、励振回路及び最終段増幅器の入力側の負バイアス端子に供給される負バイアス電圧を出力する負バイアス電源18と、この負バイアス電源の出力する負バイアス電圧に前記第1の微分回路の出力を加算して前記第1の増幅器の入力側の負バイアス端子に供給する第1の加算回路と、前記負バイアス電源の出力する負バイアス電圧に前記第2の微分回路の出力を加算して前記第2の増幅器の入力側の負バイアス端子に供給する第2の加算回路と、を有する。

(もっと読む)

ホールド回路

【課題】広い動作電圧範囲で精度よく動作するホールド回路の提供。

【解決手段】入力信号端子と、出力電圧出力端子と、非反転入力端子に入力信号端子が接続された増幅器と、入力端子に増幅器出力端子が接続された反転増幅器と、一端に増幅器反転入力端子が接続され他端に基準電位が接続されたキャパシタと、入力端子にキャパシタの一端が接続されたバッファ回路と、ゲートに増幅器出力端子が接続されソースにバッファ回路出力端子が接続されバルクに電圧源が接続された第1トランジスタと、ゲートに反転増幅器出力端子が接続されソースおよびバルクに電圧源が接続されドレインに第1トランジスタドレイン端子が接続された第2トランジスタと、ゲートに反転増幅器出力端子が接続されソースおよびバルクに第1トランジスタドレイン端子と第2トランジスタドレインとが接続されドレインにキャパシタの一端が接続された第3トランジスタと、を有するホールド回路。

(もっと読む)

半導体装置、電子機器、及び出力波形歪み改善方法

【課題】N本のクロック信号を出力した際に生ずる出力波形歪みを改善した装置構成を提供する。

【解決手段】半導体装置は、所定周波数の入力クロック信号CLK−Iを入力して同一周波数の複数のクロック信号CLK1からCLKNを出力する。前記入力クロック信号は遅延部1_1から遅延部1_N−1により所定の遅延時間差を与えられ、前記複数のクロック信号として出力される。前記複数のクロック信号の立ち上がり及び立ち下がりを分散することで、共通の電源レギュレータ11への負荷が低減する。

(もっと読む)

PLL回路

【課題】 電源起動からロックまでの時間を短くすると共に、電源断時に電荷を速く放電できるPLL回路を提供する。

【解決手段】 位相の進み/遅れを検出器11で検出し、位相の進み/遅れに相当する信号を積分器12で積分し、起動パルス生成部13が、電源起動を検出し、ロックまでの時間に基づいたパルス幅のパルスをLPF5と積分器12に出力し、LPF5と積分器12が、起動パルス生成部13からのパルスによって内部のコンデンサを充電すると共に電源断で内部のコンデンサに蓄積された電荷を放電するPLL回路である。

(もっと読む)

ピークホールド回路のリセット装置

【課題】安価な構成で適切なタイミングにリセット信号を出力させる。

【解決手段】A/D変換回路3からデジタル信号として入力されるホールドコンデンサCのホールド電圧の電圧レベルの増加を検出したときに、増加前後の電圧レベルの差をコンパレータ5aによって求める。そして、求めた差が所定のしきい値以下である場合は、リセット信号を出力する。よって、入力信号Vinの入力に伴うホールドコンデンサCのホールド電圧の増加量が、ホールド電圧の飽和判断に適した所定のしきい値以下になった時点で、初めてホールドコンデンサCをリセットしてホールド電圧を放電させる。これにより、ホールドコンデンサCの1回目のチャージ時点におけるホールド電圧に比べてはるかに、入力信号Vinの反転信号の電圧レベルのピーク値に近い値にホールド電圧が達するまで、ホールドコンデンサCをチャージさせた時点で、リセット信号を確実に出力することができる。

(もっと読む)

時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システム

【課題】測定精度および分解能を向上させることができる時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システムを提供すること。

【解決手段】時間デジタル変換器は、開始信号と停止信号との間の遅延時間に対応する第1の値を生成する第1遅延列回路を備える。時間デジタル変換器は、また、遅延開始信号と停止信号との間の遅延時間に対応する第2の値を生成する少なくとも一つの第2遅延列回路を備える。少なくとも一つの遅延素子は開始信号に所定の遅延を与えることにより遅延開始信号を生成し、合成回路は、第1の値および第2の値に基づく出力値を生成する。実施形態に係る時間デジタル変換器では、出力値は開始信号と停止信号との間の遅延時間に対応する。

(もっと読む)

スイッチトキャパシタ回路、サンプル・ホールド回路、および、A/D変換装置

【課題】CLS技術を用いたスイッチトキャパシタ回路に適用する演算増幅器の動作速度に関する所要水準を抑制しつつ比較的振幅の大きい入力信号にも適合するという優位性を維持したスイッチトキャパシタ回路等を実現する。

【解決手段】コンデンサCclsおよびスイッチSW104、SW105、SW106を含んでCLS回路120を構成する一方、スイッチSW107が介挿された導体部、および、SW104、SW105、SW106により切替え回路130を構成し、この切替え回路130によってレベルシフト用コンデンサCclsを、サンプリングフェーズで、アナログ入力信号Vinで充電されるように接続し、レベルシフトフェーズで、アナログ信号出力端子Vbと演算増幅器110の出力端子との間に介挿されるように接続関係を切替えるように構成する。

(もっと読む)

位相調整回路、検出装置及び電子機器

【課題】信号の位相を高精度に調整可能な位相調整回路、検出装置及び電子機器等を提供すること。

【解決手段】位相調整回路は、位相主調整用のローパスフィルター210と、位相微調整用のハイパスフィルター230を含む。ローパスフィルター210は、周波数finの第1の信号が入力され、その周波数finにおける位相遅れ角度がX度(X≧0)となる周波数特性を有する。ハイパスフィルター230は、ローパスフィルター210からの出力信号LQに基づく第2の信号GQが入力され、周波数finにおける位相進み角度がY度(Y≧0)となる周波数特性を有する。Y度はX度よりも小さい値に設定される。

(もっと読む)

液晶駆動用のソースドライバのオフセットキャンセル出力回路

【課題】液晶駆動用のソースドライバのオフセットキャンセル出力回路を提供する。

【解決手段】基準電圧が非反転入力端に印加されたオペアンプと、反転入力端に各々の一端が接続された入力コンデンサ及び出力コンデンサと、反転入力端とオペアンプの出力端との間に接続された第1の電界効果トランジスタを有し、リセット動作時に入力コンデンサ及び出力コンデンサ各々にオフセット電圧を蓄電させ、通常出力動作時に入力コンデンサの他端に階調電圧を印加しかつ出力コンデンサの他端をオペアンプの出力端に接続するスイッチ素子回路と、を備え、リセット動作時及び通常出力動作時に第1の電界効果トランジスタの基盤に基準電圧に等しい第1の電位を印加し、通常出力動作中の階調電圧の切り替え時に第1の電界効果トランジスタのソース/ドレインから基盤に流れるリーク電流を防止するように基盤に第1の電位とは異なる第2の電位を第1の電位に代えて印加する。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスのチャネル信号が第1、第2信号で構成される場合に第1、第2信号の差分に対応する信号の精度の高いA/D変換を実現する集積回路装置等の提供。

【解決手段】集積回路装置は、センサーデバイスからの第1信号SG1が第1期間において入力され、第1信号SG1とペアーとなってセンサーデバイスのチャネル信号を構成する第2信号SG2が第2期間において入力され、第1信号SG1と第2信号SG2の差分に対応する信号を出力する増幅回路と、増幅回路の出力信号についてのA/D変換を行うA/D変換器を含む。増幅回路は、増幅回路が有する演算増幅器のオフセット電圧をキャンセルするスイッチドキャパシター回路により構成される。

(もっと読む)

スイッチトキャパシタ回路

【課題】システムの性能劣化を避けつつ、システムの消費電力を低減する。

【解決手段】コンデンサC1と、コンデンサC1の入力側及び出力側にそれぞれ設けられたスイッチSW1〜SW4と、コンデンサC1の出力を受ける後段のオペアンプ204とを備え、スイッチSW1〜SW4の少なくとも一つの開閉状態に応じてオペアンプ204へ供給される電流値を切り替える。

(もっと読む)

ダイレクトサンプリング回路

【課題】時分割統合された信号系列に対して、時分割で兼用する場合であっても、各系統間で信号の混ざりを回避するダイレクトサンプリング回路を提供する。

【解決手段】スイッチトキャパシタフィルタ160の前段に系統毎にヒストリキャパシタ153,155を接続し、スイッチトキャパシタフィルタ160の後段に系統毎にバッファキャパシタ173,175を接続し、スイッチトキャパシタフィルタ160のローテーションキャパシタと接続するヒストリキャパシタ及びバッファキャパシタを入力している時分割系統毎に切り替える。

(もっと読む)

電源制御タイミング信号発生回路および電源装置

【課題】 ある波形の電圧値を異なる閾値と比較するので、比較精度によって、不安定であった。

【解決手段】 制御波形発生回路12で発生された台形波形を各チャンネルの増幅器13a〜13cで設定されているゲインで増幅する。すると、高ゲインであるほど増幅器13a〜13cの出力電圧の台形波のエッジ部分の勾配が急であり、各電源回路11a〜11cのオン電圧に早く到達するので、スイッチ12aのオン時は、高ゲインの増幅器13a〜13cほど出力電圧が早いタイミングでオン電圧に達し、低ゲインでは遅いタイミングでオン電圧に達する。この結果、この例では、電源回路11a〜11cの順に起動することになる。逆に、スイッチ12aのオフ時は、低ゲインの増幅器13a〜13cほど出力電圧は早いタイミングでオン電圧以下に下がり、高ゲインでは遅れてオン電圧以下になる。この結果、この例では、電源回路11c〜11aの順に終了することになる。

(もっと読む)

最大・最小電圧検出回路

【課題】複数の被測定電圧の中の最大値又は最小値を検出する為の最大・最小検出回路に関し、最大値検出時と最小値検出時との主要回路部分を共通として切替える。

【解決手段】被測定電圧V1〜Vnをそれぞれ一方の入力端子に印加し、最大電圧又は最小電圧を検出処理する制御処理部CONTに入力される電圧を他方の入力端子に印加して比較出力する複数の演算増幅器OPA1〜OPAnと、これらの演算増幅器OPA1〜OPAnの出力端子と制御処理部CONTとの間に順方向極性のダイオードD12〜Dn2と逆極性のダイオードD11〜Dn1又は寄生ダイオードが順方向と逆方向となるように接続した電界効果トランジスタとについて、何れか一方を選択接続するように切替制御を行う構成を備えている。

(もっと読む)

増幅回路装置並びにそれを用いた比較回路装置および定電圧出力装置

【課題】印刷などによって低温で生成された場合であっても高速駆動が可能でかつ良好な出力特性を得ることができる増幅回路を提供する。

【解決手段】オペアンプ100は、差動増幅回路110、バイアス回路120、電圧レベルをシフトするレベルシフト回路ユニット150と増幅回路ユニット160からなるソース接地増幅回路140を具備し、すべてのトランジスタを同一プロセスにて簡易に製造できるディプレッション型のトランジスタにて構成する。

(もっと読む)

ピークホールド形検波回路

【課題】RPIが大きく変動しても出力電圧の変動が少ない、ピークホールド形検波回路を提供すること。

【解決手段】本発明の一例のピークホールド形検波回路によれば、検波される高周波パルスが入力される入力端子にアノード端子を接続された検波ダイオードと、この検波ダイオードのカソード端子と接地間に接続されたキャパシタと、前記検波ダイオードのカソード端子に一端を接続されたスイッチ回路と、このスイッチ回路の他端と接地間に接続された放電用抵抗と、前記検波ダイオードのカソード端子に入力端子を接続され入力信号を積分する積分器と、前記高周波パルスに同期してこの高周波パルスよりも幅の広い制御用高周波パルスを前記スイッチ回路に制御信号として入力するスイッチ制御回路と、を有する。

(もっと読む)

ドライバ・コンパレータ回路およびそれを用いた試験装置

【課題】双方向伝送において送信信号をキャンセルする。

【解決手段】第1抵抗R1は、その第1端子に第1電圧VH’が印加され、その第2端子が入出力端子P1と接続される。第2抵抗R2は、その第1端子に第1電圧VH’が印加される。テイル電流源12は、所定のテイル電流Ia’を生成する。電流スイッチ10は、第2デバイス102に送信すべきデータPATを受け、その値に応じて第1抵抗R1の第2端子と第2抵抗R2の第2端子の一方を選択し、テイル電流源12と結合する。分圧回路DIV1は、第1抵抗R1の第2端子と第2抵抗R2の第2端子の間に順に直列に設けられた第3抵抗R3および第4抵抗R4を含む。負荷バランサLB1は、その第1端子に第2電圧VLBが印加され、その第2端子が第2抵抗R2の第2端子と接続された第5抵抗R5を含む。

(もっと読む)

パルスディテクタ

【課題】プラズマを発生させるようなQ値の高い負荷が接続され、パルス幅変調において高周波信号が出力される場合、信号レベルの減衰が遅くとも、サンプルホールド信号を発生させ、高周波信号の信号レベルをホールドするパルスディテクタを提供する。

【解決手段】本発明は、高周波信号の電圧の包絡波形の電圧レベル信号を出力する電圧レベル検出部と、電流の包絡波形の電流レベル信号を出力する電流レベル検出部と、電圧と電流の位相差を求める位相差検出部と、包絡波形が一端途切れ、その後出力される包絡波形の立上りを、包絡波形の信号レベルと設定された閾値とを比較して検出し、立上り信号を出力する入力検出部と、立上り信号の入力後にサンプルホールド信号を出力する制御部と、電圧レベル信号、電流レベル信号及び位相差信号の信号レベルをホールドするサンプルホールド回路を有し、閾値は、直前の包絡波形の信号レベルの設定された割合の数値である。

(もっと読む)

サプライレギュレートされたフェイズロックループ(PLL)及び用いる方法

サプライレギュレートされたフェイズロックループ(PLL)が提供される。PLLは、サプライレギュレーティングループ、電圧制御発振器(VCO)、及びVCOのためのプログラマブルデカップリングキャパシタアレイを備える。VCOデカップリングキャパシタアレイのキャパシタンスは、NかけるCUNITに等しくなるように調整可能であり、NはN分周回路の乗算ファクタの現在の値であり、CUNITはデカップリングキャパシタアレイを製造するために選ばれたプロセス技術に対して特徴付けられたユニットキャパシタンスである。PLLが1つの周波数帯から他にスイッチするとき、VCOデカップリングキャパシタによって導入される高次ポールがPLL参照周波数をトラックし、PLLの動作安定性を改善する。  (もっと読む)

(もっと読む)

1 - 20 / 72

[ Back to top ]