Fターム[5J039KK20]の内容

Fターム[5J039KK20]に分類される特許

401 - 415 / 415

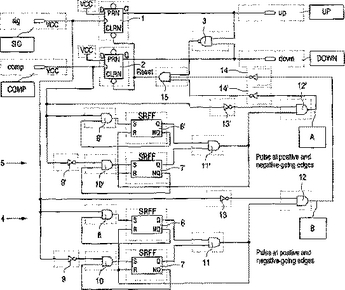

位相比較器

とりわけ、PLLモジュールに対する位相比較器は、入力信号の位相角をそれら入力信号のエッジを評価することで比較し、調節信号を生成する。この調節信号を入力信号についての崩壊或いは干渉に対して強くするために、これら入力信号(SIG、COMP)の更なる異なるエッジを評価し、これらから調節信号(UP、DOWN)に対する追加のリセット信号を生成するための追加の回路(4、5)が提供される。  (もっと読む)

(もっと読む)

ジッタ印加回路、及び試験装置

【課題】広帯域、高分解能、大振幅の位相ジッタ成分を、クロック信号に容易に印加することができるジッタ印加回路を提供する。

【解決部】与えられるジッタデータに応じた位相ジッタ成分を含むクロック信号を生成するジッタ印加回路であって、与えられる基準信号に応じて発振信号を生成するPLL回路と、発振信号を遅延させたクロック信号を出力する可変遅延回路と、ジッタデータの低周波成分に基づいてPLL回路の発振周波数を制御し、発振信号に位相ジッタ成分の低周波成分を印加する低周波印加部と、ジッタデータの高周波成分に基づいて可変遅延回路における遅延量を制御し、クロック信号に位相ジッタ成分の高周波成分を印加する高周波印加部とを備えるジッタ印加回路を提供する。

(もっと読む)

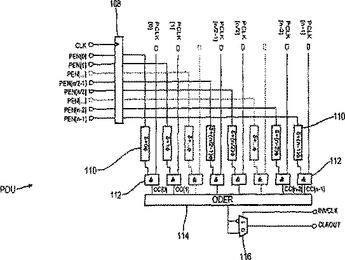

所定のクロック信号特性を有するクロック信号を生成するための方法および装置

所定のクロック信号特性を有するクロック信号(CLKOUT)を生成するための方法および装置であって、まずマスタクロック信号(CLK)に関して本質的に同一の周波数およびそれぞれ異なる位相関係を有する多数のクロック信号(PCLK[n−1:0])を準備し、次いで、準備された多数のクロック信号から(生成されるクロック信号に従って準備された制御信号(PEN[])に基づいて)所定のクロック信号を選択し、選択したクロック信号を組み合わせて所望のクロック信号(CLKOUT)を生成する。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】 エッジトリガで動作するレジスタ回路に簡単なハードウェアを付加してノイズ等の影響によるレジスタへの誤書き込み防止をはかる。

【解決手段】 書き込み制御回路が、レジスタ回路1に対する新しいデータの書き込み時、レジスタ回路1に記憶されたデータを読み出し、先にラッチ回路3に保持されたデータと一致検出回路2で一致が検出されたときのみその書き込みを許可して、狭パルス状のノイズに対するプロテクトを行う。

(もっと読む)

遅延同期ループ回路の良否検査方法及び遅延同期ループ回路の良否検査回路

【課題】

ディジタルデータをもとに良否判定可能な比較的安価な検査装置を用いて遅延同期ループ回路の良否検査を行うことができる遅延同期ループ回路の良否検査方法及び、遅延同期ループ回路の良否検査回路を提供する。

【解決手段】

基準信号を所定時間ずつ遅延させたN個のタップ信号を出力する遅延同期ループ回路の良否検査回路及びこの良否検査回路により行う良否検査方法において、各タップ信号をクロック信号とするN個のフリップフロップといずれかのタップ信号をクロック信号とするフリップフロップとを直列接続することによってシフトレジスタを形成し、このシフトレジスタを基準信号の1周期分動作させて、N個目のフリップフロップの出力信号とN+1個目のフリップフロップの出力信号とに基づいて遅延同期ループ回路の良否を判定することとした。

(もっと読む)

スプレッドスペクトラムクロック生成器及びその変調方法

【課題】製造バラツキ、電源電圧、使用温度、使用周波数が変化しても所望の変調度の周波数変調クロックを供給可能とするスプレッドスペクトラムクロック生成回路を提供する。

【解決手段】制御信号に応じて制御周期間隔で発振周期を可変に制御する第1の遅延制御型発振回路104と、第1の遅延制御型発振回路の出力を分周したクロック信号fo1と、位相比較結果に基づき周波数制御信号Cを出力する制御回路103と、変調最大値Aを決定する変調最大値決定回路106と、変調最大値A内で変調制御信号αを生成する変調信号発生回路107と、出力クロック信号の発振周期を制御信号に応じ制御周期間隔に可変に制御する第2の遅延制御型発振回路108を備えている。

(もっと読む)

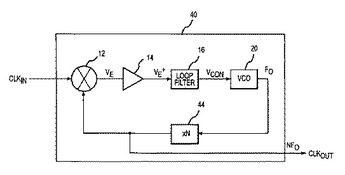

低電力と低いタイミング・ジッタのフェーズ・ロック・ループと方法

フェーズ・ロック・ループは、入力クロック信号から出力クロック信号を生成する。出力クロック信号は、クロック・ツリーを通して結合されて、出力クロック信号の位相を入力クロック信号の位相と比較する位相検出器にフィード・バックされる。出力クロック信号は、位相検出器から出力を受け取るように結合された制御入力を有する電圧制御発振器と、電圧制御発振器の出力に結合された周波数逓倍器とによって生成される。を持っている電圧制御発振器によって生成される。結果として、電圧制御発振器が相対的に低い周波数で動作することによって相対的に小さな電力を使用する一方、周波数逓倍器により生成されたCLKOUT信号は、相対的に高い周波数を持っている。  (もっと読む)

(もっと読む)

進歩した位相等化を用いたDLL位相検出

【解決手段】同期回路(例えば、遅延ロックドループ即ちDLL)の初期化中にクロックのシフトモードを開始及び終了するシステム及び方法が開示されている。初期化の際に、DLLは、ForceSL(Force Shift Left)モード及びOn1xモード(即ち、クロックサイクル毎にレフトシフト)に入る。フィードバッククロックは、(システムクロックから順次供給される)リファレンスクロックの位相をトラックし、コース位相検出ウインドウに与えられる前に、最初にコース位相検出器内で遅延される。フィードバッククロックの2つの遅延バージョンが、リファレンスクロックでサンプリングされて、一組の位相情報信号が生成される。それら信号は、その後、アドバンスド等位相(APHEQ)信号を確立するために使用される。APHEQ信号は、PHEQ(位相等化)位相のオンセットを進め、ForceSLモード及びOn1xモードの終了に使用される。これによって、クロックジッタによる不適切なForceSLの終了、又はOn1xが終了する間におけるフィードバックパスのオーバーシューティングが防止される。不適切なForceSLの終了及びOn1xのオーバーシューティングの問題が避けられることで、DLLのロッキングタイムはより速くなる。 (もっと読む)

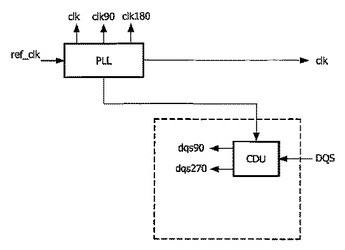

多重データレートRAMメモリコントローラ

多重データレートRAMメモリモジュールのメモリコントローラを備える。前記コントローラは、参照クロック(ref clk)から異なるクロック位相(clk、clk90、clk180)を生成するためのPLLユニット(PLL)を含む。さらに、ストローブ信号(dqs)を遅延させるための制御可能な遅延ユニット(CDU)を備える。  (もっと読む)

(もっと読む)

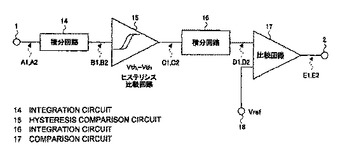

低ビットレート信号に基づくビットレート判定回路

少なくとも第1のビットレートの信号と前記第1のビットレートより高い第2のビットレートの信号のうち、どちらの信号が入力されているかを判定するビットレート判定回路が開示されている。本ビットレート判定回路は、前記第2のビットレートの信号は通過させず、前記第1のビットレートの信号の少なくとも低周波数成分の一部は通過させる周波数選択手段と、前記周波数選択手段の出力に前記第1のビットレートの信号の前記少なくとも低周波数成分の一部が通過しているかどうかを判定する低周波数成分判定手段と、前記低周波数成分判定手段の出力を平滑化する平滑化手段と、前記平滑化手段の出力を論理レベルへ変換するレベル変換手段とを有することを特徴とする。これにより、入力信号に含まれる低周波数成分に基づきそのビットレートを判定することができる。  (もっと読む)

(もっと読む)

監視回路

コンデンサと、前記コンデンサを充電する充電手段と、前記コンデンサを放電する放電手段と、前記コンデンサが充電されることによって一定以上の電圧となった際に、一定のリファレンス電圧と前記コンデンサの充電電圧とを比較することにより監視対象の動作をリセットするための信号を発する電圧比較手段と、前記監視対象の電源電圧の監

視を行い前記監視対象の電源電圧が一定以下となった際に、前記監視対象の動作をリセットする電源電圧判定手段と、を備えたマイコンが誤動作することを防止することを特徴とする監視回路。

(もっと読む)

緊急動作機能を備えたステアリングコラム切換システム

ステアリングコラム切換システムの位置を検出して、ステアリングコラム切換システムが占める切換位置をビットパターンに変換するための機器と、その検知した位置のビットパターンを切換機能に割り付ける復号化機器と、そのビットパターンの検出又は伝送の際の誤りを検出するための機器とを備えており、その場合に、この復号化機器が、誤りを検知した場合に、ビットパターンと始動する切換機能の間の割付を変更する自動車用ステアリングコラム切換システムを記載する。 (もっと読む)

差動位相検出器

【課題】本発明は、完全にデジタルで実装される差動位相検出器と、該差動位相検出器のための補間器に関する。

【解決手段】本発明によると、4つの光検出器のデジタル化された信号(A、B、C、D)からトラッキング誤差信号を生成する差動位相検出器は、デジタル化された信号(A、B、C、D)を時間多重するマルチプレクサと、時間多重されたデジタル化信号(A、B、C、D)からサンプルを同期化するためのデマルチプレクサ/補間器を含む。デマルチプレクサ/補間器は、好ましくは、4個の信号の時間多重信号を受信し、時間多重信号の半分の速度である4チャネルの信号を生成する。

(もっと読む)

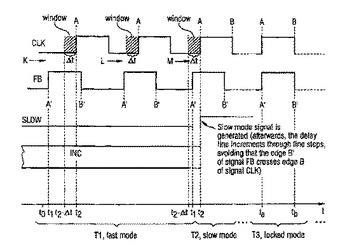

クロック信号を同期化する際に使用する装置、および、クロック信号同期化方法

本発明は、可変制御可能な遅延時間(tvar)を有する遅延手段(2)を備え、クロック信号(CLK)またはこのクロック信号(CLK)から得られる信号が、遅延手段(2)に入力され、可変制御可能な遅延時間(tvar)だけ遅延され、遅延されたクロック信号(DQS)の形状で出力される、クロック信号同期化方法、および、クロック信号(CLK)の同期化に使用する装置(1)に関するものである。本発明は、遅延手段(2)から出力される遅延されたクロック信号(DQS)またはこのクロック信号(DQS)から得られる信号(FB)の上記クロックエッジ(A’)が、上記クロック信号(CLK)またはこのクロック信号(CLK)から得られる信号の対応するクロックエッジ(A)の前の所定の時間窓の内側にあるかどうかを決定するためのデバイス(5)が設けられていることを特徴とする。  (もっと読む)

(もっと読む)

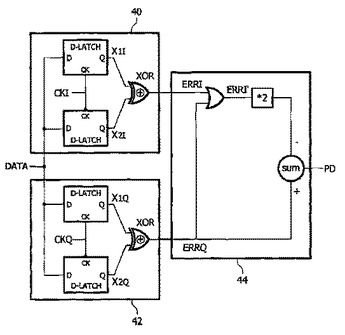

位相検出器

本発明は、データ信号DATAを用いてデータクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を検出する位相検出器に関する。データ信号DATAの遷移は、データクロックDATA-CLKの遷移と同期している。データクロックDATA-CLK及び参照クロックREF-CLKは同じ周波数を持つ。位相検出器は、第1のバイナリ信号ERRQを生成する第1の信号生成器を有する。そのパルス幅は、データ信号DATAの遷移とデータ信号DATAの遷移に隣接する第1の参照クロック信号CKQの遷移との間の第1の時間差ΔT1に等しい。第1の信号生成器は、第1の参照クロック信号CKQを受信する入力と、データ信号DATAを受信する入力とを有する。位相検出器は、第2のバイナリ信号ERRIを生成する第2の信号生成器を有する。第2のバイナリ信号ERRIのパルス幅は、データ信号DATAの遷移とそのデータ信号DATAの遷移に隣接する第2の参照クロック信号CKIの遷移との間の第2の時間差ΔT2に等しい。第2の信号生成器は、第2のバイナリ信号ERRIを受信する入力と、第2の参照信号CKIを受信する入力とを有する。位相検出器は、データクロックDATA-CLKと参照クロックREF-CLKとの間の位相差を表す出力信号を生成する出力信号生成器を有する。出力信号は、ANDが論理AND演算を表すとき、ERRQ-2*(ERRQ AND ERRI)に等しいか、又はXORが論理XOR演算を表すとき、(ERRQ XOR ERRI)-ERRIに等しい。  (もっと読む)

(もっと読む)

401 - 415 / 415

[ Back to top ]