Fターム[5J039KK20]の内容

Fターム[5J039KK20]に分類される特許

141 - 160 / 415

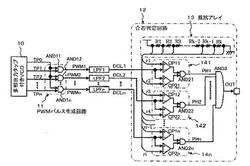

VCO位相テスト回路

【課題】簡便な冶具や計測器を用いて多相出力を有するVCOにおける出力クロック信号間の位相差を容易に測定、評価することができるVCO位相テスト回路を実現する。

【解決手段】本発明のVCO位相テスト回路は、基準となるクロック信号TP0が第1の入力に接続され、TP0と周期が同じで位相が異なるクロック信号TP1〜nが第2の入力に接続され、TP0とTP1〜nとの間のそれぞれの位相差に対応するパルス幅を持ちTP0と周期が同じパルス信号PWM1〜nを生成するPWMパルス生成回路11と、PWM1〜nが入力され、PWM1〜nのパルス幅に対応した電圧のDC電圧DCL1〜nを生成するローパスフィルターLPF1〜nと、DCL1〜nが所定の電圧範囲にある場合に有効となる判定結果信号OUTを生成する合否判定回路12を有する。

(もっと読む)

クロック生成回路

【課題】高速動作するクロック・データリカバリのための正確なクロック信号を生成するクロック生成回路を提供する。

【解決手段】クロック生成回路は、第1入力電圧に応じて第1周波数信号を出力する第1電圧制御発振回路と、第2入力電圧に応じて第2周波数信号を出力する第2電圧制御発振回路と、制御信号を受け取り、第1周波数信号と第2周波数信号との位相差が制御信号に応じた値になるように第1入力電圧と第2入力電圧とを制御する位相調整回路と、第1周波数信号に同期して受信信号を検出して出力する第1判定回路と、第2周波数信号に同期して受信信号を検出して出力する第2判定回路と、第1判定回路の出力と第2判定回路の出力とに基づいて受信信号の位相を検出し、その位相検出の結果に応じて第1入力電圧と第2入力電圧とを制御する位相検出器とを含む。

(もっと読む)

受信回路

【課題】消費電力を低減し誤動作の少ない受信回路を提供する。

【解決手段】プリアンブルを含む変調されたディジタル信号を受信する受信装置210と、検波回路220によるベースバンド信号S1と基準信号Vrefを比較するコンパレータ250と、ベースバンド信号S1の積分回路240と、積分回路240からの平均値信号S2に基づく信号S3を生成する下側ヒステリシス電圧生成回路260と、平均値信号S2に基づく信号S4/S5を生成する上側ヒステリシス電圧生成回路270と、コンパレータ250からのディジタル信号Doutに基づき、信号S3または信号S4/S5を選択しこれを基準信号Vrefとする選択回路280と、コンパレータ250からのディジタル信号のパルス数を計数し信号Qを出力するパルス検出カウンタ290と、信号Qに基づく信号S4/S5の電圧レベルを可変する電圧と、信号を処理するディジタル回路とを有する。

(もっと読む)

半導体装置

【課題】 積層された演算LSI間の通信及び演算を同期化することで、システム全体の性能向上を図る。

【解決手段】 積層されたCOMLSI及びLGLSI1は、水晶発振器クロック信号を逓倍するPLL、クロック信号を分配するクロックパルスジェネレータ、フリップフロップ回路を具備する。LGLSI1は、クロック位相比較器(CMP)、ディレイコントローラ(Delay_CTL)、ディレイチェイン(Delay_Chain)からなるDLL回路を具備する。COMLSIとLGLSI1の通信及び演算を同期させるため、COMLSIから同期用基準クロック信号が貫通電極(TVCLK)を介してLGLSI1に送信される。DLL回路により、LGLSI1の内部クロック信号はCOMLSIから同期用基準クロック信号に同期する。

(もっと読む)

トリガ回路及びトリガ信号発生方法

【課題】高帯域幅且つ低ジッタで、差動信号からトリガ信号を発生する。

【解決手段】差動信号源201からの差動信号が抵抗減衰器219、220を介して比較器211の非反転入力端及び反転入力端に供給される。電圧源203、204からの差動しきい値電圧レベルが終端抵抗器207、208を介して比較器211の非反転入力端及び反転入力端に供給される。比較器211は、非反転入力端及び反転入力端の電圧が交差したときに、トリガ出力端214からトリガ信号を発生する。

(もっと読む)

自走発振器のロックを検出するシステム及び方法

【課題】 自走発振器のロックを検出するシステム及び方法を提供することである。

【解決手段】 FROサンプラー110の出力がサンプルストレージメディア120の入力にカップリングされ、パターン検出ロジックが、サンプルストレージメディアを1つ以上のパターン検出器130に作動上カップリングしてサンプルにアクセスし又はサンプルを入手する。パターン検出器が、保存サンプル1〜Nを、保存サンプル(N+1)〜2Nと比較してその等値性を調べ、サンプル1と4が同値を含み、サンプル2と5が同値を含み、サンプル3と6が同値を含むことを発見すると、サンプル1、2、3がサンプル4、5、6と同じパターンの反復であると見なされる。

(もっと読む)

クロック生成回路

【課題】広帯域の周波数範囲におけるどの周波数の基準クロックを受けてもロックする時間を短くできるクロック生成回路を簡易な回路構成で実現。

【解決手段】基準クロックを第1の個数の電圧制御遅延素子12−1〜12−Nで遅延させて第1の遅延クロックを生成し、第2の個数の電圧制御遅延素子12−1〜12−Kで遅延させて第2の遅延クロックを生成する遅延部11と、前記基準クロックの位相と前記第1の遅延クロックの位相とを比較する位相比較部21と、遅延制御電流を出力するチャージポンプ22と、遅延制御部23と、前記基準クロックの位相と前記第2の遅延クロックの位相とを比較し、前記基準クロックと前記第1の遅延クロックとの位相差を判定する判定部13aと、前記位相差が閾値より大きい場合、前記遅延制御電流が第1の値になり、前記閾値以下の場合、前記第1の値より小さい第2の値になるように制御するチャージ制御部13bとを備える。

(もっと読む)

PLL回路

【課題】感度関数と相補感度関数の両方が低減されたPLL回路を提供する。

【解決手段】本発明のPLL回路10は、一般的なPLL回路の構成を備えた第1ループ50と、相補感度関数を低減するための第2ループ52とを備えて構成されている。第1ループ50では、周波数が高い基準クロック34を用いて比較部14にて位相比較を行うことにより、感度関数を下げている。そして、第2ループ52からの出力により電流補償部16にて電流値を補完することにより、相補感度関数を下げている。

(もっと読む)

ラッチ型コンパレータ及びこれを用いた多値論理復調回路

【課題】製造プロセスのマージンを削ることなく、オフセットの補正が可能なラッチ型コンパレータ、及びこれを用いた、オフセットの補正が可能な多値論理の復調回路を提供する

【解決手段】本発明によるラッチ型コンパレータは、クロスカップルされた2つのCMOSインバータからなるフリップフロップを含み、フリップフロップの4個のトランジスタの各々のソースと電源/接地間には伝達トランジスタを介して抵抗と設定電流可変の定電流源が接続され、フリップフロップの差動出力は各々伝達トランジスタを介して差動入力に接続され、全ての伝達トランジスタのゲートは、差動クロック入力のいずれかに接続されていることを特徴とする。

(もっと読む)

2相カウンタおよびカウンタシステム

【課題】カウント動作を高速でも容易に行えるようにすること。

【解決手段】A相パルスの前パルスエッジとB相パルスの前パルスエッジとのエッジ位相差と、A相パルスの後パルスエッジとB相パルスの前パルスエッジとのエッジ位相差とを検出し、上記両エッジ位相差の比率を演算し、上記エッジ位相差比率に対応して割り当てられたカウント値を演算する2相カウンタ。

(もっと読む)

データ復元回路、データ復元方法、及びデータ受信装置

【課題】安定した動作を容易に実現することができるデータ復元回路を提供する。

【解決手段】データ復元回路は、データ列を表す入力アナログ信号をクロック信号に同期してアナログデジタル変換することにより、前記データ列のデータ間隔より短い間隔でサンプルしたデジタルコードの列を生成するアナログデジタル変換器と、前記デジタルコードが値を取り得る範囲の略中心にある所定のコード値の位置と前記デジタルコードの列を補間して得られる線分とが交差するクロス点の位置を前記デジタルコードの列から算出する位相検出器と、前記クロス点の位置に基づいて前記データ列のデータ中心点の推定位置を求める位相推定器と、前記クロス点の位置と前記データ中心点の推定位置とに基づいて前記デジタルコードの列からデータ判定値の列を抽出するデータ判定部とを含む。

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

デューティ補正回路、及びデューティ補正方法

【課題】本発明は、入力信号のデューティ比や周波数、温度、電源電圧、プロセスによらず、出力信号のデューティ比を補正することが出来るデューティ補正回路、及びデューティ補正方法を提供することを課題とする。

【解決手段】コモンモード比較回路13からのフィードバック信号により、レベルシフト回路11はレベルを補正する。またコモンモード比較回路15からのフィードバック信号により、TrTf制御回路12は、信号のエッジの角度を補正する。

(もっと読む)

レベルシフト回路

【課題】外的要因による誤動作を防止して確実な信号伝達を行うレベルシフト回路。

【解決手段】第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、第2電圧レベルの論理電圧状態をセットするセット信号を送信するセットレベル回路21と、第2電圧レベルの論理電圧状態をリセットするリセット信号を送信するリセットレベル回路22と、第2電圧レベルでセット信号及びリセット信号を検出するための基準値を設定する基準レベル回路C3とを有し、セットレベル回路とリセットレベル回路と基準レベル回路との各々は、それぞれコンデンサC1〜C3を介して第1電圧レベルから第2電圧レベルに信号を伝達する。

(もっと読む)

ジッタ発生装置

【課題】ジッタ信号に対応したジッタ付加信号を出力できるジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、ジッタ信号を増幅する増幅回路と、基準信号が入力され、増幅回路の出力によりジッタを付加する第1のPLL回路と、基準信号が入力される第2のPLL回路と、第1、第2のPLL回路の出力を位相比較する位相比較回路と、ジッタ信号を平滑する第1の平滑回路と、位相比較回路の比較結果を入力し、平滑する第2の平滑回路と、第1、第2の平滑回路の出力を比較し、増幅回路の増幅を制御する電圧差比較回路とを備えたことを特徴とするものである。

(もっと読む)

半導体集積回路装置および遅延路の制御方法

【課題】電力効率を向上させる。

【解決手段】クロック信号CLKに同期して動作する2つの同期動作回路11、12間を並列形態で接続して信号伝送可能とされる複数の遅延路13a、13b、・・13nと、複数の遅延路13a、13b、・・13nにおけるそれぞれの遅延時間を検出する遅延検出部14と、遅延検出部14の検出結果に基づいて複数の遅延路13a、13b、・・13nの内の一の遅延路を選択し、選択した一の遅延路以外における信号伝送を阻止するように制御する制御部15と、を備える。

(もっと読む)

デューティ感知回路およびこれを備えるデューティ補正回路

【課題】デューティ補正回路のロッキングタイムを減らし、正確なデューティの補正が可能となり、多様な周波数のクロックについてデューティ補正を可能にするデューティ補正回路を提供すること。

【解決手段】本発明に係るデューティ補正回路は、デューティ調節コードC<1:5>に応答して入力クロックCLK、CLKBのデューティを調節した出力クロックCLK_OUT、CLKB_OUTを生成するデューティ調節部110と、前記出力クロックのハイパルス幅とローパルス幅の差異を測定してその差異値S<1:4>を出力するデューティ感知部120と、前記差異値を累積して前記デューティ調節コードを生成する累積部130とを備える。

(もっと読む)

プログラマブルデュアルエッジトリガードカウンター

【課題】出力クロック信号のジッターを低減し、デューティサイクル分解能を改善するための回路の提供。

【解決手段】最小のジッターを備えたクロック信号を合成するためのカウンターは、出力クロックの立ち上がりエッジを入力クロック信号の立ち上がりエッジまたは立ち下がりエッジによりトリガーしなければならないかどうかを決定するために、さらに、出力クロックの立ち下りは、入力クロック信号の立ち下りの立ち上がりエッジまたは立ち下りによりトリガーしなければならないかどうかを決定するために進行中のカウントを分析する。カウンターはM/N:Dカウンターとして実施してもよい。このカウンターにおいて、位相アキュムレーターは所定の値と比較され、出力クロック信号の立ち上がりエッジおよび立ち下りを選択する。

(もっと読む)

DLL回路及びその制御方法

【課題】本発明は、短いロッキングタイムを有する多相DLL回路及びその制御方法を提供する。

【解決手段】本発明のDLL回路は、 基準クロックを遅延させてDLLクロックを生成するが、制御電圧のレベルに応じて遅延量を調整する遅延手段;制御電圧の初期レベルを制御し、検出イネーブル信号を生成する初期動作制御手段;及び、検出イネーブル信号に応じて前記基準クロック及びDLLクロックの位相を比較して、制御電圧を生成する遅延制御手段を含むことを特徴とする。

(もっと読む)

ラッチ回路を有する信号処理装置

【課題】 ラッチ回路がノイズによって誤動作することがある。

【解決手段】

信号処理装置は、セットパルス発生回路3と、リセットパルス発生回路5と、ラッチ回路4との他に補正セットパルス形成回路30を有する。補正セット信号形成回路30は、セットパルスからリセットパルスまでの時間幅にほぼ対応する補正セット信号を形成してラッチ回路4に送る。ラッチ回路4はノイズによってリセットされても補正セット信号によって再びセットされる。

(もっと読む)

141 - 160 / 415

[ Back to top ]