Fターム[5J039KK20]の内容

Fターム[5J039KK20]に分類される特許

161 - 180 / 415

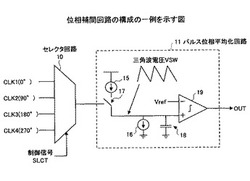

位相補間回路

【課題】線形領域での信号重ね合わせを行なうことなく所望の位相のクロック信号を生成可能な位相補間回路を提供する。

【解決手段】位相補間回路は、一定の周波数及び位相を有する基準タイミング信号のパルスの位相と同一の位相の第1のパルスと前記基準タイミング信号のパルスの位相からずれた位相の第2のパルスとを含むパルス列を生成するパルス列生成回路と、前記第1のパルスの位相と前記第2のパルスの位相との重み付け平均に応じた一定の位相位置にパルスを有する出力パルス信号を前記パルス列に基づいて生成するパルス位相平均化回路とを含み、前記重み付け平均の重みは、所定期間内において前記パルス列に含まれる前記第1のパルスの数と前記第2のパルスの数との比率に応じた重みである

(もっと読む)

半導体装置、内部信号タイミング回路、及び遅延時間測定方法

【課題】内部信号のタイミングを測定する場合、チップ内に形成されたトランジスタ等の素子における場所依存性によって特性が異なる場合にも、内部信号のタイミングを測定できる測定回路を提供する。

【解決手段】内部で実信号として用いられる第1及び第2の内部回路制御信号を生成する内部回路と、内部回路を通して受信される第1及び第2の内部回路制御信号を遅延時間測定開始信号及び遅延時間測定終了信号として受け、当該遅延時間測定開始信号及び遅延時間測定終了信号間の遅延時間を測定し、出力する遅延時間測定回路を備えた内部信号タイミング回路及び当該回路を含む半導体装置。

(もっと読む)

受信回路、電子機器、及び受信回路の制御方法

【課題】 直前の数サイクルに依存して波形が劣化する信号に対して正しく受信することができない。

【解決手段】 本発明の受信回路10は、入力信号を基準電圧と比較して比較結果をハイレベル又はローレベルで出力する比較回路12と、比較回路12の出力レベルを次の1サイクル間保持する第1の記憶回路13と、第1の記憶回路13の出力レベルを次の1サイクル間保持する第2の記憶回路14と、第1の記憶回路13と第2の記憶回路14の出力レベルに応じて前記基準電圧のレベルをサイクル毎に制御する電圧制御回路11を有する。

(もっと読む)

半導体装置

【課題】PVT変動による遅延制御回路の遅延量変動を正しく補正する。

【解決手段】互いに動作条件が異なる第1及び第2の遅延素子列121,122と、第1及び第2の遅延素子列121,122に同時に入力されたパルス信号Pの伝搬速度差を検出する検出回路123と、検出回路123による検出結果に基づいて選択信号SELを生成する設定回路124とを備える。選択信号SELは、基準信号を遅延させることによって動作タイミング信号を生成する遅延制御回路130に供給され、その遅延量は選択信号SELによって調整される。これにより、PVT変動を見越して遅延制御回路の遅延量を大きく設計しておく必要がなくなるため、パフォーマンスの低下を防止することが可能となる。

(もっと読む)

基準クロック周波数の決定および/またはループ発振器のロックを行うための方法、アルゴリズム、回路、およびシステム

【解決手段】 基準クロックの周波数を決定する装置、方法、システム、アルゴリズム、および回路を開示する。一実施形態によると、基準クロックの周波数を検出する回路であって、周波数が既知であり、精度は所定の値であるスリープクロックの所定の部分の間、基準クロックのサイクル数をカウントして、基準クロックサイクルカウント値を得るクロックカウンタと、基準クロックサイクルカウント値および既知であるスリープクロックの周波数に基づいて、基準クロックの周波数を推定する周波数推定部と、複数の許容周波数から、推定された基準クロックの周波数に最も近い周波数を選択する周波数選択部とを備える回路が提供される。 (もっと読む)

FM信号のノイズキャンセラ回路

【課題】FM信号に含まれるノイズを適切に低減する。

【解決手段】処理対象となるFM信号の復調前の信号の振幅と閾値とを比較してFM信号の欠落を検出する検出回路102と、FM信号の復調後の信号に基づいて閾値を設定する閾値設定回路104と、を備えるFM信号のノイズ検出回路とする。

(もっと読む)

2値化回路と位相差判別装置

【課題】 入力電圧を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と第1出力端子26と第2出力端子28とピークホールド回路30とボトムホールド回路40と閾値演算回路50と第1比較回路60と第2比較回路70と第1選択回路80と第2選択回路90と第3選択回路100と第4選択回路110を備えている。第1選択回路80は2値化信号を出力し、第2選択回路90は遅れ2値化信号を出力する。ピークホールド回路30は遅れ2値化信号に基づいてピーク電圧を減少させ、ボトムホールド回路40は遅れ2値化信号に基づいてボトム電圧を増加させる。そのため、遅れ2値化信号を2値化信号に対して確実に遅延させることが可能となる。

(もっと読む)

信号処理装置及び信号処理方法

【課題】ロック状態を維持したまま、発振周波数のVCO制御電圧特性を粗調整する。

【解決手段】VCO63は、トランジスタを内蔵し、入力されたVCO制御電圧に対応する発振周波数を発生させ、LPF131a乃至131dは、VCO63が内蔵するトランジスタのゲートに、予め決められた変化率でトランジスタのゲート電圧を変化させる入力電圧を入力し、VCO制御電圧に対する、発振周波数のVCO制御電圧特性を粗調整する。本発明は、例えばPLL回路やCDR回路に適用することができる。

(もっと読む)

FM信号のノイズキャンセラ回路

【課題】FM信号に含まれるノイズを適切に低減する。

【解決手段】処理対象となるFM信号の復調前の信号の振幅と閾値とを比較してFM信号の欠落を検出し、検出信号を欠落が発生している期間出力する検出回路102と、検出信号を受けた時点におけるFM信号の復調後の信号を保持するホールド回路40と、検出信号が出力されていない間はFM信号の復調後の信号を選択して出力し、検出信号が出力されている間はホールド回路40の出力を選択して出力するセレクタ回路42と、を備えるノイズキャンセラ部106を含む。

(もっと読む)

同期信号検出回路および半導体集積回路

【課題】水平方向の描画開始位置を決定する同期信号の検出精度を向上させることができる同期信号検出回路および半導体集積回路を提供する。

【解決手段】同期信号検出回路は、単位検出回路のうちの偶数番目の単位検出回路からなり、偶数番目の単位検出回路による単位検出結果にもとづいた偶数側検出結果を出力する偶数側検出回路と、奇数番目の単位検出回路からなり、奇数番目の単位検出回路による単位検出結果にもとづいて奇数側検出結果を出力する奇数側検出回路と、偶数側検出結果と奇数側検出結果とを比較し、比較の結果に応じて、偶数側検出結果と奇数側検出結果とのいずれかにもとづいて、有効エッジのタイミングを判定する判定回路とを有し、同期信号の有効エッジの多相クロック信号のクロックエッジに対するタイミングを判定する。

(もっと読む)

電圧比較器

【課題】消費電流を増加することなく高速化することが可能な電圧比較器の提供。

【解決手段】この発明は、差動増幅回路11、微分回路12、および出力増幅回路13を備えている。差動増幅回路11は、差動入力された信号を差動増幅して出力する。微分回路12は、差動増幅回路11の出力を微分し、この微分出力を出力増幅回路13の定電流トランジスタM7のバイアス電圧に加算する。

(もっと読む)

同期検出回路、これを用いたパルス幅変調回路、及び同期検出方法

【課題】部品点数の削減、高い検出精度の確保、処理速度低下の防止等を図る。

【解決手段】位相ロックループ回路15により、基準クロック信号に基づいて互いに位相が異なる複数相の多相クロック信号を生成する多相クロック生成回路11と、前記多相クロック信号の中から、同期信号に同期するクロック信号を特定する同期クロック特定回路12とを有する同期検出回路2であって、前記多相クロック生成回路11は、前記基準クロック信号を逓倍した周波数を有する高速多相クロック信号と、前記高速多相クロック信号を分周した周波数を有する低速多相クロック信号とを生成し、前記同期クロック特定回路は、同期信号と前記高速多相クロック信号との比較結果と、前記同期信号と前記低速多相クロック信号から選択された代表クロック信号との比較結果とに基づいて、前記同期信号の同期位置を示す同期位置信号を生成する。

(もっと読む)

プログラマブルロジックデバイス、カード及び伝送装置

【課題】 冗長構成とすることなく、デバイスの運用を中断せずに機能の更新が可能となると共に、冗長分のコスト及び消費電力を削減できるプログラマブルロジックデバイス、カード及び伝送装置を提供する。

【解決手段】 FPGA10は、入力される入力信号を複数に分配し、論理ブロックに既に構成された論理回路1及び論理ブロックに新規に構成される新規な論理回路11に対して、分配された信号を出力する分配回路部2と、論理回路1及び新規な論理回路11からの各出力信号のうちいずれかを選択するセレクタ回路部3と、新規な論理回路11に出力信号を出力するように分配回路部2を制御すると共に、新規な論理回路11からの出力信号を出力するようにセレクタ回路部3を制御する切り替え制御部4と、を備える。

(もっと読む)

ノイズ除去回路および方法

【課題】デジタルデバイスに入力される周期的パルス信号の一周期にわたってノイズパルスを除去することができるノイズ除去回路および方法を提供する。

【解決手段】周期的パルス信号からノイズパルスを除去するノイズ除去回路は、固定高レベルを入力とし、周期的パルス信号aおよびリセット信号dに従って高レベルと低レベルとの間で回路出力を変化させるフリップフロップ回路10と、周期的パルス信号aのレベルが変化してから一周期内で次にレベル変化するまでは固定高レベルの入力により、それ以後はリセット信号dによりフリップフロップ回路の出力を固定するリセット制御部20と、を有する。

(もっと読む)

信号再生回路向け位相比較回路及び信号再生回路向け位相比較回路を備える光通信装置

【課題】 1/Nレート構成に対応可能な高精度な位相比較回路を得る。

【解決手段】それぞれ、N相クロック信号CLKの各クロック信号を、受信データ信号DINの立ち上がりに同期してトラックホールドするN個のトラックホールド回路を備える。これらのN個のトラックホールド回路の出力から、受信データ信号DINの立ち上がりエッジが、クロック信号CLKの立ち上がりエッジに位置しているクロック信号をトラックホールドしているもののみをセレクタで選択して、位相差信号として出力する。

(もっと読む)

コンパレータ回路

【課題】

MOSトランジスタの閾値電圧の差によって発生するオフセット電圧の影響を軽減させ、比較精度の高いコンパレータ回路を提供する。

【解決手段】

各スイッチがオンにされているキャリブレーションモードにおいて、第1のキャパシタCaおよび第2のキャパシタCbに、出力部5におけるプラス側とマイナス側の出力電圧を記憶させる。各スイッチがオフに切り替わり比較モードに移行すると、第1のMOSトランジスタM6および第2のMOSトランジスタM7のゲートに、キャパシタCaおよびCbが記憶したそれぞれの電圧が印加されて補正電圧を基準としたラッチ動作の準備が整う。電流ラッチ回路2は、入力電圧と基準電圧の差を増幅させてHIGHまたはLOWを出力する判定を行う。出力部5では、HIGHまたはLOWに応じた電圧差が生じ、これに応じた電流が流れる。

(もっと読む)

コンパレータ回路及びそれを有するアナログデジタルコンバータ

【課題】判定時間を短くしたコンパレータ回路と,それを有するADCを提供する。

【解決手段】コンパレータ回路は,入力信号が判定値より大きいか小さいかを示す判定信号を出力する。そして,コンパレータ回路は,入力信号と第1の比較値とを比較し判定結果を有する第1の判定信号を生成する第1のコンパレータと,入力信号と,第1の比較値と異なる第2の比較値とを比較し判定結果を有する第2の判定信号を生成する第2のコンパレータと,第1及び第2の判定信号のうちいずれが先に生成されたかを検出し,先に生成された信号を選択して判定信号として出力する出力選択回路とを有する。

(もっと読む)

位相同期回路及びその制御方法、通信装置

【課題】

安定した周波数の出力信号を出力できるようにした位相同期回路及びその制御方法、通信装置を提供する。

【解決手段】

位相同期回路は、入力される制御電圧に応じた周波数の信号を出力信号として出力する電圧制御発振回路と、入力信号と電圧制御発振回路の出力信号との位相を比較する比較手段と、位相の比較に基づく電圧を異なるタイミングでそれぞれ保持する2つ以上のサンプル/ホールド回路と、2つ以上のサンプル/ホールド回路のいずれかを選択し、該選択したサンプル/ホールド回路からの出力を制御電圧として電圧制御発振回路に入力する切換手段と、入力信号の異常を検出する異常検出手段とを具備し、切換手段は、異常検出手段による異常の検出結果に基づいて2つ以上のサンプル/ホールド回路のいずれかの出力を選択する。

(もっと読む)

周波数検出回路

【課題】回路構成が簡単で、省電力化および小面積化を図りながら、確実に周波数を検出することが可能な周波数検出回路を提供する。

【解決手段】入力クロック信号の周波数に応じて等価抵抗が変更するものとなされたスイッチトキャパシタ回路と抵抗素子とを直列に接続し、電源電圧を前記スイッチトキャパシタ回路の等価抵抗と抵抗素子の抵抗とで分圧し、その分圧された電圧をシュミット回路に入力する。シュミット回路は、入力された分圧電位がしきい値電位を超えると高電位信号を出力し、しきい値電位未満であると低電位信号を出力する。これにより、入力クロック信号の周波数に応じて高電位信号または低電位信号が出力され、周波数を検出することができる。

(もっと読む)

比較演算増幅回路、AD変換回路、電子機器

【課題】比較演算増幅回路やAD変換回路において、回路規模や消費電力のさらなる低減を図る。

【解決手段】サンプルホールド回路503では、複数のサンプルホールド回路と信号選択回路により、AD変換対象の差動アナログ信号対について、ホールドモード時の出力信号対を時分割で出力するようにする。フォールディング方式を採らないAD変換においては、比較演算増幅回路501は、時分割で供給される複数の出力信号対について、信号選択回路により複数の差動基準信号対を時分割で扱うように切り替えながら、各出力信号対と各差動基準信号対の差を各差動増幅回路で増幅することで複数の増幅出力信号対を時分割で出力するようにする。デジタルデータ取得部6は、時分割で供給される複数の増幅出力信号対の差をそれぞれ2値化することでデジタルデータを取得する。

(もっと読む)

161 - 180 / 415

[ Back to top ]