Fターム[5J039KK21]の内容

Fターム[5J039KK21]に分類される特許

1 - 20 / 26

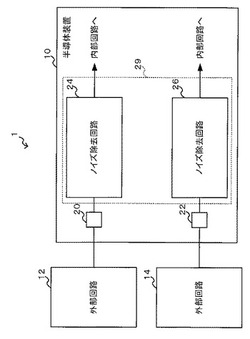

半導体装置及びノイズ除去装置

【課題】電源電圧の変動を伴うノイズに対して、入力される信号に応じた入力端子の種別によってそれぞれ異なる手法を用いることによりノイズ耐性が装置内で向上する。

【解決手段】外部回路12から入力端子20を介してノイズ除去回路24に発振信号が入力される。電源ノイズにより電源電圧が変動した場合は、ノードBにLレベルパルスのグリッチが発生し出力信号が反転する。OR回路48には、当該出力信号と、遅延回路46により遅延されてグリッチ(反転)のタイミングがずれた遅延信号と、が入力されるため出力信号は、反転せずHレベルを保つ。一方、外部回路14から入力端子22を介してノイズ除去回路26に遅延に関する制限が厳しい高周波の発振信号が入力される。シュミット回路52の入力と出力との間に接続された容量素子C7により、ノードAが電源電圧に追従して変動するため、ノードBにグリッチが発生せず、反転せずにHレベルを保つ。

(もっと読む)

コンパレータ回路

【課題】コンパレータ回路において、従来技術に比較して高速で消費電力を低下させる。

【解決手段】入力される2つの入力電圧に応じて、第1及び第2のMOSトランジスタからなる入力差動対のいずれか1つのMOSトランジスタにおいて、当該1つのMOSトランジスタとスイッチトランジスタとを含むループにより適応バイアス電流を発生する入力差動対及び適応バイアス電流発生回路と、上記適応バイアス電流に対応する電流を検出してラッチ論理を変化させた後、上記スイッチトランジスタをオンからオフに切り換えることにより上記適応バイアス電流を遮断するラッチ回路とを備える。

(もっと読む)

制御回路及びこれを用いたデータ保持装置

【課題】セットの部品点数削減や低消費電力化を実現することが可能な制御回路及びこれを用いたデータ保持装置を提供する。

【解決手段】制御回路10は、トリガ信号TRIGGERに特定の信号パターンが現れたときに制御部11の動作に必要な内部クロック信号LCLKの生成を開始し、少なくとも制御部11において所定の処理が完了するまで内部クロック信号LCLKの生成を継続した後、内部クロック信号LCLKの生成を停止する内部クロック生成部12と、内部クロック信号LCLKを用いて前記所定の処理を実行する制御部11と、を有する。

(もっと読む)

ヒシテリシス装置

【課題】簡易な構成でヒシテリシス特性を付与する。

【解決手段】ヒシテリシス装置1000は、複数の閾値に対応するオフセット電圧を入力信号Vinに付加した調整信号Vxを出力する入力信号調整部300と、調整信号Vxに基づいて2値化した第1信号10aを出力するコンパレータ10と、入力信号調整部300を制御して複数の閾値ごとにオフセット電圧を切り替えるとともに、オフセット電圧の切り換えごとに第1信号10aを取得し、複数の閾値に対応する第1信号10aと前回の出力信号DETとに基づいて今回の出力信号DETを生成する判定部200とを備える。

(もっと読む)

半導体集積装置における遅延回路及びインバータ

【課題】静電気放電に対する耐性が強く且つ低消費電力にて、遅延時間のバラツキを抑えることが可能な遅延回路及びインバータを提供する。

【解決手段】遅延回路のインバータとして、低電位部は、夫々のソース端子及びドレイン端子が第1共通接続点にて接続されている一対のFETを有し、高電位部は、夫々のソース端子及びドレイン端子が第2共通接続点にて接続されている一対のFETを有する。インバータ出力L2が高電位状態となった場合には、上記第1共通接続点に電源電位VDDを印加する一方、低電位状態となった場合には、上記第2共通接続点に接地電位GNDを印加することによりヒステリシス特性を持たせる。更に、製造上のバラツキ又は環境温度の変化に伴う遅延時間の変動を抑制させるべく、上記した電源電位VDD又は接地電位GNDの供給元となり、かつ常時オン状態のFETを設ける。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

遅延回路

【課題】矩形波を入力される遅延回路において、入力信号にノイズパルスが存在すると、出力信号のジッターが生じる。

【解決手段】シュミットコンパレータ102からの出力信号VdoでスイッチSW3を制御し、コンデンサCstへの充電電流を供給する電流源I1と、放電電流を供給する電流源I2とのいずれかを選択する。入力信号VdiでスイッチSW1,SW2を制御することで、選択された電流源からの電流供給がオン/オフされる。シュミットコンパレータ102はコンデンサCstの電圧Vstに応じてVdoを切り替える。Vdiの立ち上がり時には、VdiのHレベル期間にてコンデンサCstへ充電電流を供給し、Vdiの立ち下がり時には、VdiのLレベル期間にてコンデンサCstへ放電電流を供給する。

(もっと読む)

ヒステリシスコンパレータ

【課題】 差動対に入力信号とオフセット電圧を入力し、この差動対に接続される負荷MOSトランジスタのゲートとドレインをたすき掛け接続する構成のヒステリシスコンパレータは、MOSトランジスタのサイズを調整することにより任意のヒステリシス幅を得ることができるが、ヒステリシス幅の1/2のオフセット電圧を与えなければならず、かつヒステリシス幅が半導体プロセスのばらつきによって変動してしまうという課題を解決する。

【解決手段】 差入力信号Vinと閾値Vthが入力される差動対30と負荷部31で構成され、ヒステリシス特性を有する第1のコンパレータ部と、負荷部32と差動対30で構成され、ヒステリシス特性を有さない第2のコンパレータ部の動作を、ヒステリシスコンパレータの出力Voutによって切り替えるようにした。第2のコンパレータ部が動作するときは、出力Voutが遷移する電圧は閾値Vthのみで決まるので、半導体プロセスの影響を受けない。

(もっと読む)

周波数検出回路

【課題】回路構成が簡単で、省電力化および小面積化を図りながら、確実に周波数を検出することが可能な周波数検出回路を提供する。

【解決手段】入力クロック信号の周波数に応じて等価抵抗が変更するものとなされたスイッチトキャパシタ回路と抵抗素子とを直列に接続し、電源電圧を前記スイッチトキャパシタ回路の等価抵抗と抵抗素子の抵抗とで分圧し、その分圧された電圧をシュミット回路に入力する。シュミット回路は、入力された分圧電位がしきい値電位を超えると高電位信号を出力し、しきい値電位未満であると低電位信号を出力する。これにより、入力クロック信号の周波数に応じて高電位信号または低電位信号が出力され、周波数を検出することができる。

(もっと読む)

発振検出回路

【課題】低電力化を可能とし、リーク電流による誤動作の発生を無くした発振検出回路を提供する。

【解決手段】発振検出回路は、基準電圧源に接続された第1の入力端子と発振回路出力端に接続された第2の入力端子とを有しており、複数のバイポーラトランジスタにより構成される差動回路を採用し、差動回路の出力端に接続され出力端の電位に応じて充電または放電を行う容量素子と、容量素子の電位に基づいて発振信号端の所望の発振状態を検出する検出回路を有する。

(もっと読む)

逆ヒステリシス回路

【課題】入力信号の周波数に変化が生じた場合であれ、確実に動作することの逆ヒステリシス回路を提供する。

【解決手段】逆ヒステリシス回路1は、第1インバータ10の出力信号である第1出力信号OUT1の電圧レベル及び第2インバータ20の出力信号である第2出力信号OUT2の電圧レベルの双方に基づいて、逆ヒステリシス回路1としての入力端子に入力される入力信号の立ち上がり時における閾値電圧レベルを第1閾値電圧レベルとし、入力信号の立ち下がり時における閾値電圧レベルを第2閾値電圧レベルとする出力信号を生成する出力信号生成部を備える。出力信号生成部30は、第1出力信号OUT1の電圧レベルに応じて動作する第1フリップフロップ32と、第2出力信号OUT2の電圧レベルに応じて動作する第2フリップフロップ35とを含んで構成されている。

(もっと読む)

高速シリアルインターフェース回路及び電子機器

【課題】トランジスタの経時変化による信頼性の劣化等を防止できる高速シリアルインターフェース回路及びこれを含む電子機器を提供すること。

【解決手段】高速シリアルインターフェース回路は、データレシーバ回路10、クロックレシーバ回路20、シリアル/パラレル変換回路40を少なくとも有するロジック回路ブロック30、自走クロック生成回路70、クロック検出回路80を含む。クロック検出回路80は、差動クロック信号線を介してクロックが転送されているか否かを検出する。クロックレシーバ回路20は、自走クロック生成回路70から自走クロックOSCKを受け、差動クロック信号線を介してクロックが転送されていないことが検出された場合には受信クロックCKINの代わりに自走クロックOSCKをロジック回路ブロック30に出力する。

(もっと読む)

ノイズ除去回路

【課題】少ない素子数のノイズ除去回路で、入力信号のノイズ除去を行う。

【解決手段】ノイズ除去回路30には、信号処理部1及びシュミットトリガ回路2が設けられる。信号処理部1には、2入力NOR回路NOR1、インバータINV1、Pch MOSトランジスタPT1、及びNch MOSトランジスタNT1が設けられ、クロック信号CLK及びイネーブル信号ENbを入力する。シュミットトリガ回路2には、インバータINV2、Pch MOSトランジスタPT2、Pch MOSトランジスタPT3、Nch MOSトランジスタNT2、及びNch MOSトランジスタNT3が設けられ、クロック信号CLK及び信号処理部1から出力される2つの信号を入力し、ノイズが除去されたクロック信号CLKを出力信号Soutとして出力する。

(もっと読む)

入力回路

【課題】入力レベルに対してヒステリシス特性を持たせる。

【解決手段】第1トランジスタM1は、ソースが接地端子P2に接続され、ゲートに入力デジタル信号S1が入力される。第2トランジスタM2は、ソースが電源端子P1に接続され、そのドレインが第1トランジスタM1のドレインに接続される。第2トランジスタM2はデプレッション型で構成する。第1インバータ12は、第1トランジスタM1、第2トランジスタM2の接続点P3、すなわちドレイン電位Vxを反転し、第2トランジスタM2のゲートに出力する。入力回路10は、接続点P3のドレイン電位Vxに応じたレベルを出力する。

(もっと読む)

高ヒステリシス幅入力回路

【課題】従来のヒステリシス入力回路は等価的にP型MOSFETとN型MOSFETのインバータ回路のβ比を変えて、ロジックレベルのヒステリシスを作っていたが、この方式では電源電圧が低下するとヒステリシス幅が極端に小さくなった。また、電源電圧の広範囲の変動に対してヒステリシス幅を確保することは難しかった。また、ロジックレベルを形成するのにP型とN型MOSFETを用いるので形状比の設定にやや無理があり、また製造工程でのバラツキの影響を受けやすかった。

【解決手段】入力回路2個と正極の電源にP型、N型MOSFET、負極の電源にN型、P型MOSFETと、及び前状態を記憶するラッチ回路を設け、前状態により、前記各MOSFETをオン・オフすることにより、ヒステリシス特性を得る。電圧特性が異なるMOSFETを使い分けることにより、前述の課題が解消できた。

(もっと読む)

インバータアンプ

【課題】パワーダウン時のリーク電流が抑制されるインバータアンプの提供。

【解決手段】入力端子とバイアス供給回路との間にパワーダウン時リーク電流抑制用トランジスタを設ける。

(もっと読む)

短時間信号検出回路

【課題】回路技術による対策が困難であるようなノイズが入力された場合に備えて、そのようなノイズの存在を検知する。

【解決手段】信号のレベルが第1レベルと第2レベルとの間で変動する信号について所定時間以上信号値が継続しない短時間信号を検出する短時間信号検出回路であり、前記第2レベルから第1レベルの方向に遷移する信号が入力されたときに起動され、前記第1レベルの信号が第2レベルの方向に遷移を開始するまでの第1レベルの信号の継続期間に計時を続行するタイマ3と、前記第1レベルの信号の継続期間が所定時間未満か否かを判定する判定手段13と、前記第1レベルの信号の継続期間が所定時間未満のときに、その旨を報知する報知信号を生成する第1生成手段4と、を備える。

(もっと読む)

比較回路、および赤外線受信機

【課題】誤動作防止能力を有しつつ、休止期間の短い入力パルスの周期と同一の周期を有するパルスを出力する能力を向上することができる比較回路を提供する。

【解決手段】比較回路10は、入力パルス信号の切り替わりに応じて、充放電電流により容量105を交互に充放電する充放電回路100と、容量105の容量電圧(Csig)と、第1の閾値電圧(Vth1)、および第1の閾値電圧よりも大きい第2の閾値電圧(Vth2)とをそれぞれ比較することによって、比較結果に応じたパルス信号を生成し、該パルス信号を出力パルス信号のレベルを切り替える信号として出力信号生成回路550に出力するコンパレータ回路200と、上記生成されたパルス信号から、充放電回路100の充放電電流の電流値を調整する信号を生成して充放電回路100に出力することにより、充放電電流の電流値を調整する論理処理回路300とを備える。

(もっと読む)

シュミットトリガ回路及びそれを具備する半導体集積回路

【課題】無駄な電流を減少させると共に入出力特性のヒステリシス幅の調整範囲を広くすることが可能なシュミットトリガ回路を提供する。

【解決手段】このシュミットトリガ回路1は、入力信号を反転して出力する第1のインバータ2と、第1のインバータ2の出力信号を反転して出力する第2のインバータ3と、入力信号及び第2のインバータ3の出力信号に基づいて、第1のインバータ2の出力ノードと高電位側の電源電位との間及び/又は第1のインバータ2の出力ノードと低電位側の電源電位との間のインピーダンスを調整するインピーダンス調整回路4とを具備する。

(もっと読む)

発振検知回路

【課題】トランジスタ特性のバラツキに影響されることなく、発振回路の発振を安定的に検知することが可能な発振検知回路を提供すること。

【解決手段】電源VDDとグランドVSSとの間に電流源IS11,IS12が直列に接続される。電流源IS11と電流源IS12との接続点P1にはコンデンサC1が接続され、この接続点P1に現れる信号を積分する。電流値の大きな電流源IS11と接続点P1との間にはスイッチSW1が設けられる。シュミットトリガーST1は、積分された信号を入力して2値信号を出力する。この2値信号は論理積回路ANに入力され、検知信号OSCSTPが出力される。ここで、発振回路の出力信号NCKMに基づきスイッチSW1が開閉すると、電流I11が断続的にコンデンサC1に供給される。この結果、接続点P1の信号レベルが上昇し、検知信号OSCSTPがハイレベルとなって発振が検知される。

(もっと読む)

1 - 20 / 26

[ Back to top ]