Fターム[5J039KK22]の内容

Fターム[5J039KK22]に分類される特許

1 - 20 / 39

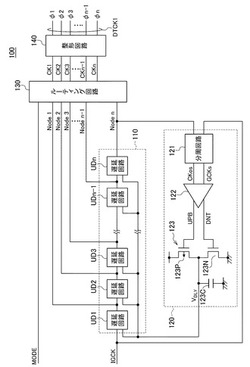

半導体装置及びこれを用いた情報処理システム

【課題】遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成する。

【解決手段】縦列接続された遅延回路UD1〜UDnからなり、入力クロック信号IGCKをk周期遅延させるディレイラインと、遅延回路UD1〜UDnからそれぞれ出力される出力クロック信号Node1〜Nodenに基づいて互いに位相の異なる多相クロック信号DTCK1を生成するルーティング回路130とを備える。nとkの最大公約数をGCM、入力クロック信号IGCKの1サイクルをGCK、多相クロック信号DTCK1の相間隔をUIとした場合、相間隔UIの長さは、UI=GCK×GCM/nで与えられる。これにより、1個の遅延回路の遅延量の最小値よりも短い相間隔を有する多相クロック信号を小さな回路規模で生成することが可能となる。

(もっと読む)

クロック生成回路、クロック生成方法および半導体集積回路

【課題】占有面積や定常位相誤差の増大、並びに、クロックが安定するまでに長時間を要することなく、スペクトラム拡散クロックを生成してEMI対策を図る。

【解決手段】基準信号CK1を受け取って、立ち上がりエッジの傾き、または、立ち下がりエッジの傾き、または、立ち上がりエッジおよび立ち下がりエッジの傾きを、周期的に変化させた第1信号CK2を生成する第1回路4と、前記第1信号を受け取って、周期的に周波数が変化するクロックを生成する第2回路5と、を有する。

(もっと読む)

クロック生成回路および撮像装置

【課題】シュミットトリガー回路と同様な機能を有し、シュミットトリガー回路と比較して貫通電流を低減する。

【解決手段】インバータ回路INV1は、前段回路の回路閾値よりも低い第1の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第1の回路閾値に応じた第1の出力信号を出力する。インバータ回路INV2は、前段回路の回路閾値よりも高い第2の回路閾値を有し、前段回路から出力された入力クロックが入力され、入力クロックの論理状態および第2の回路閾値に応じた第2の出力信号を出力する。スイッチ回路SWは、第1の出力信号および第2の出力信号が入力され、第1の出力信号および第2の出力信号の論理状態が、異なる状態から同じ状態に変化したときに、異なる論理状態に対応した第1の電圧および第2の電圧のいずれか一方を出力クロックとして出力する。

(もっと読む)

信号発生装置および試験装置

【課題】エッジの位相を固定して、信号のデューティ比を変更する。

【解決手段】指定されたデューティ比の出力信号を出力する信号発生装置であって、入力信号と出力信号との位相差を検出する位相検出器と、位相検出器により検出された位相差をフィルタリングして、発振器に供給するループフィルタと、位相差に応じた周波数の発振信号を出力する発振器と、指定値に応じて発振信号のデューティ比を変更して出力信号として出力するとともに位相検出器に供給するデューティ変更部と、を備える信号発生装置を提供する。

(もっと読む)

デジタル信号入力装置

【課題】動作が安定するとともに、後段に接続されるCMOSのLSIの安定な動作を実現するデジタル信号入力装置を提供する。

【解決手段】外部から入力された信号を増幅する増幅部と、前記増幅部で増幅された信号を波形整形する波形整形部と、オフセット電圧を保持するコンデンサと、前記波形整形部の出力をハイレベル状態に固定するように、前記コンデンサの充電と放電を制御して前記オフセット電圧を決定する制御部とを備える。

(もっと読む)

半導体集積回路

【課題】入力信号の立ち上がり時と立ち下がり時で遷移時間差の少ないレベルシフト回路を提供する。

【解決手段】同じ回路構成のVDD 電源系の第1、第2のレベルシフタ11、12と、VEXTQ 電源系のインバータ13と、VDD 電源系のインバータ15を具備し、第1のレベルシフタ11内の2個の入力用NMOSトランジスタTN1 、TN2 のゲート端子には、VEXTQ 電源系の入力信号INとインバータ13の出力信号を入力し、第2のレベルシフタ12内の2個の入力用NMOSトランジスタTN3 、TN4 のゲート端子には、第1のレベルシフタ11の出力ノードA2の信号とインバータ13の出力信号を入力し、第2のレベルシフタ12の出力ノードA4の信号をインバータ15により波形整形して出力信号OUT を得る。

(もっと読む)

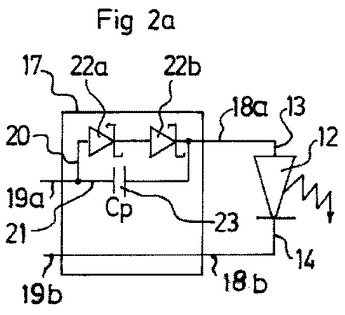

光電素子の超高速駆動用受動素子回路

本発明は、光電素子の超高速駆動回路において、時間400ps以下のエッジを有する電圧矩形波の発生器、ならびに、光電素子の電源端子(13)に直列に接続するように適合された出力、および、電圧矩形波発生器に接続され、そこで形成される電圧矩形波を受け取る入力を備える制御パルス成形回路(17)を含み、前記入力端子と前記出力端子の間に、ゼロでない閾値電圧を有する受動整流回路(22a、22b)からなる第1の分岐(20)であって、その受動整流回路(22a、22b)が第1の分岐内において直列をなし、光電素子の前記電源端子(13)に対して順方向をなす第1の分岐(20)と、第2の容量性分岐(21)とが互いに並列につながれていることを特徴とする駆動回路に関する。  (もっと読む)

(もっと読む)

波形合成回路と該回路を備えたデューティ補正回路及びデューティ補正方法

【課題】デューティ制御バッファの出力信号のパルスが消滅してしまうという問題を回避する回路を提供する。

【解決手段】入力信号IN1、INB1を受けるデューティ制御バッファ10と、デューティ制御バッファの出力OUT1、OUTB1を受け、デューティの誤差を検出して制御信号VCNT1、VCNTB1を生成するデューティ制御電圧発生部20を備える。デューティ制御バッファ10は、入力信号を差動で受ける第1の差動対と第2の差動対を備えた差動段と、第1の差動対の出力対と第2の差動対の出力対がそれぞれ接続され、前記第1、第2の差動対の出力対と電源との間に接続された負荷素子対と、第1、第2の差動対にそれぞれ駆動電流を供給する電流源段とを備え、第1の差動対のトランジスタ対の電流駆動能力が異なり、第2の差動対のトランジスタ対の電流駆動能力が異なる不平衡差動対よりなる。

(もっと読む)

デューティ補正回路、及びデューティ補正方法

【課題】本発明は、入力信号のデューティ比や周波数、温度、電源電圧、プロセスによらず、出力信号のデューティ比を補正することが出来るデューティ補正回路、及びデューティ補正方法を提供することを課題とする。

【解決手段】コモンモード比較回路13からのフィードバック信号により、レベルシフト回路11はレベルを補正する。またコモンモード比較回路15からのフィードバック信号により、TrTf制御回路12は、信号のエッジの角度を補正する。

(もっと読む)

パルス幅補正装置およびパルス幅補正方法

【課題】二値化のコンパレートレベルを調整することなく、データが誤って取り込まれるのを防止すること。

【解決手段】デューティー比検出回路3は、二値化信号DIのデューティー比の基準値からのずれを検出し、遅延回路5は、二値化信号DIを所定の遅延量だけ順次遅延させた遅延信号DLを生成し、セレクタ6は、デューティー比検出回路3にて検出された二値化信号DIのデューティー比のずれに対応した遅延信号DLnを遅延信号DLから選択し、パルス幅補正回路7は、セレクタ6にて選択された遅延信号DLnを用いることにより、二値化信号DIのパルス幅を補正する。

(もっと読む)

海中通信システム

【課題】海中におけるxDSL通信など、海中での高速データ通信の実現に好適な海中通信システムおよび海中通信方法を提供する。

【解決手段】海中通信システムは、海中に投下される海中投下型センサと、海上に位置する計測処理装置と、海中投下型センサと計測処理装置とを接続する海中通信ケーブル6と、海中投下型センサと計測処理装置との間で海中通信ケーブル6を介して信号を送受信する通信処理手段TEとを備えるものとし、上記通信処理手段TEは、海中通信ケーブル6を介して海中投下型センサから計測処理装置へ信号を送信するときに、海中の通信外乱をキャンセルする。

(もっと読む)

半導体回路および試験装置

【課題】電源電圧のリップルが信号処理回路に及ぼす影響を低減する。

【解決手段】第1信号処理回路10は、第1信号S1に所定の信号処理を施し、その特性値に変化を与えて第2信号S2を出力する。第2信号処理回路12は、第2信号S2に所定の信号処理を施し、その特性値に変化を与えて第3信号S3を出力する。第1、第2スイッチング電源20、22はそれぞれ、第1、第2信号処理回路10、12に対し電源電圧Vdd1、Vdd2を供給する。第1信号処理回路10が第1信号S1の特性値に与える変化量と、第2信号処理回路12が第2信号S2の特性値に与える変化量はそれぞれ、電源電圧Vdd1、Vdd2に対する依存性を有する。第1、第2スイッチング電源20、22の位相はそれぞれ、第1信号S1の特性値の変化量とその目標値との誤差と、第2信号S2の特性値の変化量とその目標値との誤差がキャンセルするように設定される。

(もっと読む)

ジッタ増幅回路、信号発生回路、半導体チップ、及び試験装置

【課題】入力信号に含まれるジッタを増幅するジッタ増幅回路150。

【解決手段】入力信号に含まれるジッタを増幅するジッタ増幅回路であって、入力信号を受け取り、入力信号の波形を歪ませることにより、入力信号の高調波成分を生じさせる歪回路と、歪回路が出力する歪信号を、ジッタを増幅すべき増幅率に応じた次数の高調波成分以外の成分を除去して通過させるフィルタとを備えるジッタ増幅回路。

(もっと読む)

インターフェイス回路およびそれを備える表示装置

【課題】波形整形回路の周波数特性の測定を可能にする。

【解決手段】波形整形回路11は、入力差動信号INN,INPを波形整形する。出力切換回路12は、通常モードのときには、波形整形回路11からの整形差動信号SP,SNを2値化して出力する。一方、出力切換回路12は、テストモードのときには、波形整形回路11からの整形差動信号SN,SPを正弦波信号として出力する。

(もっと読む)

高電圧、高速、高パルス繰返し数のパルス発生器

【課題】RF電力増幅器と関連する高パルス繰返し数の制限を解決する高電圧、高速、および高繰返し数パルス発生器(30)を提供する。

【解決手段】パルス発生器(30)は共振技術を利用して、短絡および開回路の双方の負荷状態中に、パルス発生器(30)の機能障害なしに、パルス発生器(30)の継続的な高電圧、高速、および高繰返しパルス数動作を可能にする電流制限特徴をもたらす。本発明の好適な実施例において、パルス発生器(30)は、DC電圧を高周波AC電圧に変換するように構成されているインバータ(40)と、前記AC電圧に応答して、AC電流源として動作するように構成されているコンバータ(50)と、前記AC電流源によって発生するAC入力電流に応答して、高電圧、高速、高繰返し数電圧パルスを発生させるように構成されているパルス整形部分(60)とを備える。

(もっと読む)

スイッチング回路

【課題】 装置に依存することなく良好なノイズ特性と損失特性を実現することができるスイッチング回路を提供すること。

【解決手段】 フィードバック回路部41を備える規範電圧波形追従駆動部4によりスイッチング素子を駆動して負荷を作動させるスイッチング回路1において、フィードバック回路部41を備える規範電圧波形追従駆動部4へ入力する信号波形を、予めノイズ特性と損失特性を設定した波形にして出力する規範電圧波形生成部3を備えた。

(もっと読む)

レファレンス電圧発生回路とそれを用いた電圧増幅器

【課題】高速応答性に優れたレファレンス電圧回路を用いて、種々の信号振幅を持つ入力信号を一定の振幅まで増幅できる電圧増幅器を提供する。

【解決手段】レファレンス電圧発生回路7において、第1の期間ではスイッチSW1のみをOFFにして、入力信号Inの最大ピーク値Vmaxが第1の容量1のノードAに保持される。次の第2の期間では、スイッチSW2、SW3も開放されて、前記最大ピーク値Vmaxと最小ピーク値Vminとの差電圧が容量列4のノードCに保持される。この時、第1の容量1の保持電圧に容量列4の第2の容量2の保持電圧が加算されて、ノードBの電圧がレファレンス電圧Vrefとして出力される。差動増幅回路6の一方の入力端子には入力信号Inが与えられ、他方の入力端子には前記レファレンス電圧Vrefが与えられる。前記ノードA、Cの保持電圧が安定した時点でレファレンス電圧Vrefが発生する。

(もっと読む)

波形整形回路及び無線受信装置

【課題】波形整形特性の低下を抑制しつつ、立ち上り特性を向上させることができる波形整形回路を提供すること。

【解決手段】入力信号Vinを基準信号Vrefに基づいて二値波形に整形した出力信号Voutを生成する波形整形回路1において、基準信号Vrefを生成する基準信号生成器2と、入力信号Vinと基準信号Vrefとの比較結果に応じて出力信号Voutを生成する比較器COMP1とを備え、基準信号生成器2は、入力信号Vinにおけるピークホールド値(Vp)とボトムホールド値(Vb)の中間電圧Vcを基準信号Vrefとして比較器COMP1に出力した後、入力信号Vinを積分した電圧を基準信号Vrefとして比較器COMP1に出力する。

(もっと読む)

データ保持回路および信号処理回路

【課題】設計が容易でグリッチノイズを発生させることなくクロック信号の立ち上がりと立ち下がりの両エッジを用いて入力信号をラッチする。

【解決手段】排他的論理和回路XOR3の入力端には、排他的論理和回路XOR1の出力信号とフリップフロップXDF1の出力信号とが入力され、フリップフロップDF1の入力端子Dには、排他的論理和回路XOR2の出力信号が入力されてクロック信号CLKの立ち上がりタイミングで入力データDが出力されて保持され、また、フリップフロップXDF1の入力端子Dには、排他的論理和回路XOR3の出力信号が入力されてクロック信号CLKの立ち下がりタイミングで入力データDが出力されて保持され、排他的論理和回路XOR4の入力にはフリップフロップDF1の出力信号とフリップフロップXDF1の出力信号が入力され、排他的論理和回路XOR4の出力が最終出力結果OUTとして出力される。

(もっと読む)

パルス幅検出回路、直流成分キャンセル回路及び受信回路

【課題】受信電流のパルス幅に応じたほぼ正確なパルス幅を持つ受信信号を出力する受信回路を提供すること。

【解決手段】第1フィルタ回路24は、電圧信号VA1を高域通過フィルタを通した第1の成分と、前記電圧信号VA1の低周波成分もしくは直流成分に基づく第2の成分を含む第1の処理信号S1を生成する。第2フィルタ回路25は、第1の処理信号S1を増幅した電圧信号VA2を高域通過フィルタを通した成分からなる第2の処理信号S2を生成する。そして、2値化回路26は、第2の処理信号S2を増幅した電圧信号VA3を2値化して受信信号RXを生成する。

(もっと読む)

1 - 20 / 39

[ Back to top ]