Fターム[5J039KK23]の内容

Fターム[5J039KK23]の下位に属するFターム

リングカウンタ (3)

アップダウンカウンタ (37)

Fターム[5J039KK23]に分類される特許

1 - 20 / 259

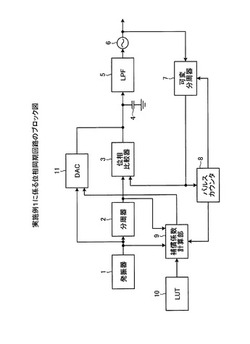

位相同期回路及び位相同期回路制御方法

【課題】少ない分周数を用いた小数点以下の分周における位相の同期を精度良く行う位相同期回路及び位相同期回路制御方法を提供する。

【解決手段】位相比較器3は、基準クロックと比較クロックとの位相差を電流に変換して出力する。キャパシタ4は、位相比較器3から入力された電流に応じて電圧を出力する。VCO6は、キャパシタ4から入力された電圧によって出力周波数を制御し、当該出力周波数を有する信号を出力する。可変分周器7は、VCO6から出力された信号を所定の周期で異なる値に分周することで、小数点以下の値を有する分周を行なった比較クロックを生成する。パルスカウンタ8は、可変分周器7から出力された比較クロックの数をカウントする。補償係数計算部9は、パルスカウンタ8のカウント数を基に、キャパシタ4に対する電流及び電圧の補償値を取得する。DAC11は、前記補償値を基に、キャパシタ4に対して電流を流し補償を行う。

(もっと読む)

デジタルPLL回路、半導体集積回路装置

【課題】デジタルPLL回路の追従可能な周波数レンジを拡大する。

【解決手段】第1カウンタ(21)は、第1クロック信号をカウントして第1カウント値を出力し、第2カウンタ(22)は、第2クロック信号を分周して生成される第3クロック信号をカウントして第2カウント値を出力する。位相検出器(23)は、第1クロック信号と、第3クロック信号との位相差をデジタル値で示す出力値を出力する。位相誤差演算回路(26)は、第1カウント値と、第2カウンタ値と、出力値とに基づいて、位相誤差を演算して出力する。デジタルフィルタ回路(107)は、位相誤差を平滑化して発振周波数を示すコードを出力する。デジタル制御発振器(108)は、コードに応答して第2クロック信号を出力する。キャリブレーション制御回路(112)は、分周比と、第2クロック信号と第1クロック信号との比較結果とに基づいてデジタル制御発振器の発振周波数を調整する。

(もっと読む)

遅延ロックドループを内蔵する半導体集積回路およびその動作方法

【課題】擬似ロックを防止するための論理回路の回路規模を低減する。

【解決手段】遅延ロックドループ(DLL)は、複数の可変遅延回路DL0〜8の電圧制御遅延回路1と位相周波数比較器2とチャージポンプ3を具備する。初段の出力PH[0]と最終段の出力PH[8]は、比較器2に供給される。比較器2のアップ信号とダウン信号は、チャージポンプ3に供給される。擬似ロック防止回路4は、第M段の出力PH[1]と第M+1段の出力PH[2]に応答して、可変遅延リセット信号RST_VDL_T、Bを生成する。初段の回路DL0から第M+1段の回路DL2に、クロック入力信号CLKとクロック反転入力信号がリセット信号RST_B、Tとして供給される。第M+2段の回路DL3から最終段の回路DL8に、可変遅延リセット信号RST_VDL_T、Bがリセット信号RST_B、Tとして供給される。

(もっと読む)

クロック出力回路

【課題】クロック出力回路1にて電流消費を抑えつつ、周波数が安定したクロックを出力する。

【解決手段】 発振回路10から出力される発振信号を論理否定するNOTゲート21A、22Aと、NOTゲート21Aの出力信号を論理否定するNOTゲート23と、NOTゲート22A、23の出力信号を入力信号とするRSフリップフロップ回路24とを備え、NOTゲート21Aの第1の閾値Th1はNOTゲート22Aの第2の閾値Th2よりも大きく、発振信号の周波数が高くなるほど第1の閾値Th1が大きくなり、発振信号の周波数が高くなるほど第2の閾値Th2が小さくなる。発振回路10の発振子11の発振が安定化する前では、RSフリップフロップ回路24が源クロックの出力を待機し、周波数が低くなるとRSフリップフロップ回路24が源クロックを出力する。

(もっと読む)

集積回路

【課題】集積回路において電力消費量を容易に低減する。

【解決手段】集積回路は、クロック分配回路、同期動作回路、論理回路、および、電源供給部を備える。クロック分配回路は、所定のタイミングを指示するクロック信号を分配する。同期動作回路は、クロック信号に同期して動作する。論理回路は、同期動作回路の動作結果に基づいて所定の論理演算を実行する。電源供給部は、クロック分配回路を駆動させるクロック分配回路駆動電圧より低い電圧を論理回路に論理回路駆動電圧として供給する。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】主クロック分配回路は、タイミング信号を複数の主タイミング信号に分岐して分配する。副クロック分配回路は、タイミング信号の分配が指示された場合にはタイミング信号を複数の副タイミング信号に分岐して分配する。最小遅延タイミング信号出力部は、複数の主タイミング信号のいずれかと複数の副タイミング信号のいずれかとのうち先に分配された信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。測定部は、複数の主タイミング信号のいずれかの遅延のばらつきを示す値を測定する。クロック分配回路制御部は、測定された値の示す前記ばらつきが前記所定値以上であるときに副分配回路に前記タイミング信号の分配を指示する。

(もっと読む)

オンダイターミネーション制御装置

【課題】較正正確度が改善されたオンダイターミネーション制御装置を提供する。

【解決手段】オンダイターミネーション抵抗値を外部抵抗値と同一に調整するオンダイターミネーション制御部と、第1パルス信号の活性化時にオンダイターミネーション制御部の出力電圧から比較器のオフセット電圧値を検出してキャパシタに保存し、第2パルス信号の活性化時にオフセット電圧値を相殺した後、出力電圧と既に設定された基準電圧とを比較して出力するオフセット補償部と、第3パルス信号の活性化時にオフセット補償部の出力を一定時間保存するラッチと、ラッチの出力をカウントしてコード信号を増加又は減少させるカウンタとを含み、オフセット補償部は、第2パルス信号の活性化時に保存されたオフセット電圧値を相殺して基準電圧と比較し、ラッチ及びカウンタは、第2パルス信号の活性化区間内において活性化状態に制御される第3パルス信号に応じて活性化制御される。

(もっと読む)

半導体装置

【課題】サンプル間、温度等の変位に伴い発生するロック位相の変動を補正し、ロック位相を一定とすることができるDLLを備えた半導体装置を提供する。

【解決手段】位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を変更するPDバックゲート電位変更回路106と、温度センサ107と、サンプル別閾値電圧(Vt)情報を記憶したFuse(ヒューズ)108を備える。温度センサ107の温度情報、Fuse(ヒューズ)108に記憶されたサンプル別閾値電圧(Vt)情報は、PDバックゲート電位変更回路106に読み出され、閾値電圧を制御し、ロック位相の変動を補正する。

(もっと読む)

位相比較装置

【課題】ステップ応答収束時間だけ待つ必要なく積分値を抽出し、また、入力信号の周波数が既知でなくても抽出した積分値に応じて位相差を演算する位相比較装置を得る。

【解決手段】分周器4が入力信号の周波数を2分周し、積分器5が排他的論理和回路3により生成されたパルスを分周器4により設定された周期分積分し、基準積分器7が既知の一定レベルの基準信号を分周器4により設定された周期分積分し、信号処理部10が積分器5および基準積分器7による積分値に応じて位相差を演算するように構成したので、入力信号の周波数の1/2倍の周波数の整数倍の周波数にヌル点のできるsyncフィルタ特性が形成されることを利用し、ローパスフィルタが不要になり、ステップ応答収束時間だけ待つ必要なく積分値を抽出することができる。また、2つの入力信号の周波数が既知でなくても、2つの入力信号の位相差を演算することができる。

(もっと読む)

クロック生成回路、クロック生成方法および半導体集積回路

【課題】占有面積や定常位相誤差の増大、並びに、クロックが安定するまでに長時間を要することなく、スペクトラム拡散クロックを生成してEMI対策を図る。

【解決手段】基準信号CK1を受け取って、立ち上がりエッジの傾き、または、立ち下がりエッジの傾き、または、立ち上がりエッジおよび立ち下がりエッジの傾きを、周期的に変化させた第1信号CK2を生成する第1回路4と、前記第1信号を受け取って、周期的に周波数が変化するクロックを生成する第2回路5と、を有する。

(もっと読む)

同期信号処理装置

【課題】回路の小面積化、低消費電力化を図ることが可能であり、しかも温度依存性の影響を受けない安定した位相比較が可能な同期信号処理装置を提供する。

【解決手段】水平同期信号を同期クロックで同期させ、当該同期クロックのタイミングでデジタルデータとして出力する時間デジタル変換器(TDC)と、同期クロックをカウントして参照クロックを生成する参照クロック生成部と、TDCによるデジタルデータと参照クロックの位相比較を行うことにより位相差情報を得るデジタル位相比較器と、デジタル位相比較器の位相差情報に応じて上記参照クロックとTDCによる水平同期信号のデジタルデータの位相が一致するように周波数が制御される同期クロックを生成する同期クロック生成装置と、を有する。

(もっと読む)

位相比較回路

【課題】入力信号の周波数比が整数でない場合にも、±180度の範囲で位相差検出ができる位相比較回路を得る。

【解決手段】RF信号と基準信号との立ち上がりエッジを比較してアップ信号またはダウン信号を生成する位相比較コア回路1と、RF信号と基準信号との周波数比をN+K/M(但し、N,K,Mは任意の自然数)とし、RF信号の周波数をfrfとしたとき、アップ信号の立ち上がりの直前のRF信号の立ち上がりに同期して立ち上がり、パルス幅は基準信号の1周期分とほぼ等しく、周期は(M×N+K)/frfとなるマスク制御信号MSK1を生成するマスク信号生成回路2と、位相比較コア回路1により生成されたアップ信号およびダウン信号を、マスク信号生成回路2により生成されたマスク制御信号MSK1に従いマスクする信号マスク回路3とを備えた。

(もっと読む)

位相ロックループ回路

【課題】電圧制御発振回路の入力部でのリークに起因する定常位相誤差を防止できる位相ロックループ回路を提供する。

【解決手段】リファレンスクロック信号とフィードバッククロック信号の位相差を検出する位相比較回路と、検出された位相差に応じた電流を第1の容量に出力するチャージポンプ回路と、第1の容量に蓄積されている電荷に基づく制御電圧に応じた発振周波数の出力クロック信号を生成する電圧制御発振回路とを有する位相ロックループ回路にて、チャージポンプ回路による第1の容量への電流の出力完了後の第1の時刻に第1の電圧を保持し、保持された第1の電圧に基づき電圧制御発振回路の入力部に流れるリーク電流に応じた電流を生成し、生成された電流に応じた補正電流をカレントミラー回路を介して第1の容量に出力するようにして、リーク電流による制御電圧の変動を抑制する。

(もっと読む)

電子回路及びそのタイミング調整方法

【課題】電子回路及びそのタイミング調整方法において、フリップフロップのホールドエラーを防止すること。

【解決手段】クロック信号CLKに同期してテストパターンTPを出力する送信側フリップフロップFFt1〜FFt3と、テストパターンTPを遅延させる遅延回路41〜43と、遅延回路41〜43から出力されたテストパターンTPをラッチすると共に、テストパターンTPを出力する受信側フリップフロップFFr1〜FFr3と、受信側フリップフロップFFr1〜FFr3から出力されたテストパターンTPと期待値とを比較して、それらが一致するか否かを示す比較信号Sp1〜Sp3を出力する比較器46と、比較信号Sp1〜Sp3によってテストパターンTPと期待値とが一致していないときに、遅延回路41〜43の遅延時間を調整するタイミング調整器45とを有する電子回路による。

(もっと読む)

パルス信号補正装置およびそれを用いた充填装置

【課題】流量計と充填を制御する制御装置の間でノイズなどによって流量を表すパルスが増加あるいは消失すると、制御装置が正確な流量を把握できないので、正確に充填することができない。本発明はこのような課題を解決することを目的にする。

【解決手段】パルス信号補正装置を経由して流量計の出力を制御装置に入力する。パルス信号補正装置は流量計の出力と制御装置が受信したパルス数の差分を計算し、この差分に基づいて、次の出力周期で出力パルス数を補正するようにする。制御装置が正確な流量を得ることができるので、正確に充填できる。

(もっと読む)

電圧検知回路および半導体装置

【課題】入力電圧範囲が上限基準電圧から下限基準電圧までの範囲であるか否かについては検知できるが、その範囲内において、どの電圧レベルであるかを検知することができない。

【解決手段】電圧検知回路は、上限値と下限値との間を周期的に変化する非方形波信号と、入力電圧とを比較し、前者が後者より大きいか後者が前者より大きいかを示す二値の電圧検知信号を出力するコンパレータ3と、前記電圧検知信号に含まれるパルスの幅を計測することにより前記入力電圧の電圧レベルを検出する検知部5とを備える。

(もっと読む)

デジタルPLL回路及びクロック生成方法

【課題】位相差検出値の範囲の制限により引き込み動作が影響されることのないデジタルPLL回路を提供する。

【解決手段】デジタルPLL回路は、マスタクロックとスレーブクロックとの位相差を検出し、長さが2πの範囲内の値をとる位相差検出値を出力するデジタル位相比較器10と、位相差検出値と閾値とを比較した結果に応じて、位相差検出値を範囲に限定されない位相値に補正する補正部11と、補正部の出力する位相値に応じてスレーブクロックを生成するスレーブクロック生成部15とを含む。

(もっと読む)

クロック生成回路

【課題】従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供する。

【解決手段】基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えた。

(もっと読む)

クロック生成装置及びDLL(DigitalLockedLoop)回路及びクロック生成方法

【課題】回路規模が小さく、また設計が容易な構成にて、高精度なクロックを生成するDLL回路を実現する。

【解決手段】DLL回路は、外部から入力される動作クロックclksと前記動作クロックと周波数が異なるもしくは等しい入力クロックと所望の周波数を表す設定値kから前記動作クロック周波数の前記設定値k分の一の周波数を有する生成クロックclkcを生成するクロック生成部100と、前記生成クロックclkcと外部から入力される参照クロックclkrの位相差を比較し、その位相差を出力する位相比較部200と、前記位相比較部200の出力である位相差から、前記位相差を“0”とするように前記設定値kへ補正をする補正値を生成し、前記設定値kへ補正値を加算する補正部300とを備える。

(もっと読む)

時間デジタル変換装置

【課題】時間デジタル変換装置のダイナミックレンジを広くする。

【解決手段】第1の信号に応答して、所定の周期で繰返される第1のパルスの生成を開始する第1のパルス列生成部と、前記第1の信号に応答して、前記第1のパルスのカウントを開始するカウンタ回路と、入力端子が互いに接続され更にクロック端子が互いに接続される複数の遅延フリップフロップを有するストキャスティック型時間デジタル変換装置とを含み、第2の信号が入力する時の前記カウンタ回路のカウント数に基づく第1の時間を、前記第1の信号と前記第2の信号の時間差として検出する。

(もっと読む)

1 - 20 / 259

[ Back to top ]