Fターム[5J039KK35]の内容

Fターム[5J039KK35]に分類される特許

1 - 20 / 24

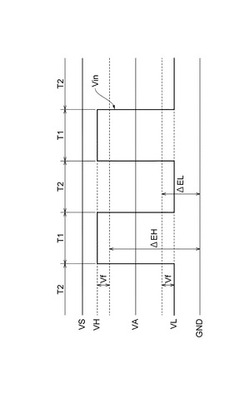

二値化回路

【課題】動作速度の低下を抑えつつ、ハイレベル及びローレベルの判定精度を高めることができる二値化回路を提供する。

【解決手段】二値化回路20は、ダイオード31及びコンデンサ32を有するピークホールド回路部30と、ダイオード41及びコンデンサ42を有するボトムホールド回路部40と、コンデンサ32とダイオード31との間のノードN1の電圧、及びコンデンサ42とダイオード41との間のノードN2の電圧の平均電圧VAと入力信号Vinの電圧とを比較して入力信号Vinを二値化する比較回路部70と、上記平均電圧VAに比例する電圧を出力する基準電圧生成回路部60とを備える。ボトムホールド回路部40は、基準電圧生成回路部60から出力された電圧を基準電位VSとして用いる。

(もっと読む)

ホールド回路

【課題】広い動作電圧範囲で精度よく動作するホールド回路の提供。

【解決手段】入力信号端子と、出力電圧出力端子と、非反転入力端子に入力信号端子が接続された増幅器と、入力端子に増幅器出力端子が接続された反転増幅器と、一端に増幅器反転入力端子が接続され他端に基準電位が接続されたキャパシタと、入力端子にキャパシタの一端が接続されたバッファ回路と、ゲートに増幅器出力端子が接続されソースにバッファ回路出力端子が接続されバルクに電圧源が接続された第1トランジスタと、ゲートに反転増幅器出力端子が接続されソースおよびバルクに電圧源が接続されドレインに第1トランジスタドレイン端子が接続された第2トランジスタと、ゲートに反転増幅器出力端子が接続されソースおよびバルクに第1トランジスタドレイン端子と第2トランジスタドレインとが接続されドレインにキャパシタの一端が接続された第3トランジスタと、を有するホールド回路。

(もっと読む)

ピークホールド回路のリセット装置

【課題】安価な構成で適切なタイミングにリセット信号を出力させる。

【解決手段】A/D変換回路3からデジタル信号として入力されるホールドコンデンサCのホールド電圧の電圧レベルの増加を検出したときに、増加前後の電圧レベルの差をコンパレータ5aによって求める。そして、求めた差が所定のしきい値以下である場合は、リセット信号を出力する。よって、入力信号Vinの入力に伴うホールドコンデンサCのホールド電圧の増加量が、ホールド電圧の飽和判断に適した所定のしきい値以下になった時点で、初めてホールドコンデンサCをリセットしてホールド電圧を放電させる。これにより、ホールドコンデンサCの1回目のチャージ時点におけるホールド電圧に比べてはるかに、入力信号Vinの反転信号の電圧レベルのピーク値に近い値にホールド電圧が達するまで、ホールドコンデンサCをチャージさせた時点で、リセット信号を確実に出力することができる。

(もっと読む)

ピークホールド回路及びボトムホールド回路

【課題】ピークホールド回路及びボトムホールド回路の検出精度を高め、高温動作における当該回路の検出精度の劣化を抑制すること。

【解決手段】各ゲートに入力端子1と出力端子2が接続される第1の差動入力回路7と、第1のカレントミラー回路10を備える第1の差動増幅回路12と、第1のカレントミラー回路10に流れる電流I1に比例する充電電流I2を生成する第5のトランジスタ13と、ゲートが第1の差動増幅回路12の出力ノード16に接続され、ソースとドレインがそれぞれ第5のトランジスタ13のドレインとキャパシタ17に接続される第6のトランジスタ14と、充電電流I2を充電するキャパシタ17を備え、出力電圧VOUTが入力信号VINのピーク値に近づくに従って充電電流I2を減少させることで、ピークホールド回路の過剰の行き過ぎを抑制し、検出精度を高めた。

(もっと読む)

局部発振器

【課題】デジタル制御発振器の出力と参照信号とが非同期であっても、安定したPLL動作を確立できる局部発振器を提供することを目的とする。

【解決手段】デジタル制御発振器の発振信号と前記参照信号との位相差を発振器分数位相として出力し、また、前記発振信号の位相が、前記参照信号の位相に対して、前記発振信号の半周期よりも位相が遅れている場合に「−1」、遅れていない場合に「+1」の補整情報を出力する時間デジタル変換器と、|前記補整情報−予測位相情報|>|前記補整情報+前記第1位相情報−前記予測位相情報|の場合に、前記第1位相情報に前記補整情報を加算したものを第2位相情報として出力し、|補整情報−発振器予測位相|>|補整情報+第1位相情報−発振器予測位相|でない場合に、前記第1位相情報を第2位相情報として出力する補正部と、を備えている。

(もっと読む)

ピークホールド回路

【課題】ピークホールド回路の構成を簡素化する。

【解決手段】ピークホールド回路10は、複数の入力信号(IN1,IN2,Vref)のうち最大レベルの入力信号に応じた大きさの出力信号Voutを出力する最大レベル検出手段20と、第1電極d1と、固定電位が供給される第2電極d2とを有する容量素子C1と、を備え、最大レベル検出手段20は、複数の入力信号(IN1,IN2,Vref)のうち最大レベルの入力信号のレベルに応じた電位を生成する電位生成部50と、オープンドレイン形式のトランジスタであって、電位生成部50で生成された電位がゲートに供給され、電源電位VDDがソースに供給され、容量素子C1の第1電極d1にドレインが接続される出力トランジスタToと、を具備する。

(もっと読む)

信号レベル検出回路

【課題】増幅回路の動作に必要な電流値を増加させることなく、ヒステリシスを用いて耐ノイズ特性を向上させることができる信号レベル検出回路を提供すること。

【解決手段】増幅回路6aの電圧利得は、増幅回路6bの電圧利得より大きく、切替装置6cは、ピークホールド回路7aに増幅回路6aの出力信号が入力している場合に比較回路9からアラーム信号を受信すると、ピークホールド回路7aに出力する信号を増幅回路6aの出力信号から増幅回路6bの出力信号に切り替え、ピークホールド回路7aに増幅回路6bの出力信号が入力している場合に比較回路9からアラーム信号を受信すると、ピークホールド回路7aに出力する信号を増幅回路6bの出力信号から増幅回路6aの出力信号に切り替える。

(もっと読む)

パルスディテクタ

【課題】プラズマを発生させるようなQ値の高い負荷が接続され、パルス幅変調において高周波信号が出力される場合、信号レベルの減衰が遅くとも、サンプルホールド信号を発生させ、高周波信号の信号レベルをホールドするパルスディテクタを提供する。

【解決手段】本発明は、高周波信号の電圧の包絡波形の電圧レベル信号を出力する電圧レベル検出部と、電流の包絡波形の電流レベル信号を出力する電流レベル検出部と、電圧と電流の位相差を求める位相差検出部と、包絡波形が一端途切れ、その後出力される包絡波形の立上りを、包絡波形の信号レベルと設定された閾値とを比較して検出し、立上り信号を出力する入力検出部と、立上り信号の入力後にサンプルホールド信号を出力する制御部と、電圧レベル信号、電流レベル信号及び位相差信号の信号レベルをホールドするサンプルホールド回路を有し、閾値は、直前の包絡波形の信号レベルの設定された割合の数値である。

(もっと読む)

2値化回路

【課題】 入力信号を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と基本クロック端子22と判定クロック端子23とリセット端子24と温度補償クロック端子25と2値化出力端子26と遅れ出力端子28とピークホールド回路30とボトムホールド回路40と2値化判定回路120と入力信号検出回路130と停止判定回路140を備えている。2値化回路10では、停止判定信号が入力信号の停止期間を検出し、この停止期間にピークホールド回路30とボトムホールド回路40が、各々の記憶値を入力信号に追従して変化させる。これによって、停止期間に、入力信号がピークホールド回路30とボトムホールド回路40の記憶値から算出される閾値を越えて変化することが抑制され、停止期間に2値化出力が反転することが抑制される。

(もっと読む)

2値化回路

【課題】 入力信号を2値化する2値化回路を提供する。

【解決方法】 2値化回路10は、入力端子20と基本クロック端子22とリセット端子24と第1出力端子26と第2出力端子28と判定クロック端子27とピークホールド回路30とボトムホールド回路40と出力信号生成回路120と補償信号生成回路130を備えている。出力信号生成回路120は、入力端子20に入力される入力信号が短周期で変化する稼動期間に、ピークホールド値減少信号をピークホールド回路30に出力し、ボトムホールド値増加信号をボトムホールド回路40に出力する。補償信号生成回路130は、入力信号が短周期で変化しない停止期間に、補償信号をピークホールド回路30とボトムホールド回路40に出力する。これによって、入力信号の状態に関わらず入力信号を適切に2値化することができる。

(もっと読む)

ホールド回路

【課題】 低消費電力化が可能なホールド回路を提供する。

【解決方法】 ピークホールド回路2では、信号保持用のコンデンサ10の一方の電極と入力端子20の間に、スイッチ回路4が形成されている。スイッチ回路4は絶縁ゲート型トランジスタ5を備えており、ゲート電極5cが切換回路15に接続されている。絶縁ゲート型トランジスタ5は切換回路15によって制御され、出力電圧Voutのピーク電圧を保持する際に絶縁ゲート型トランジスタ5を遮断する。コンデンサ10に蓄えられた電荷が変動することなく、出力電圧Voutのピーク電圧が保持される。また、切換回路15はリセット端子19に接続されており、出力電圧Voutをリセットする際に、絶縁ゲート型トランジスタ5を遮断する。入力端子20からGNDへと貫通電流が流れることがない。消費電力が抑制される。

(もっと読む)

充放電回路および2値化回路

【課題】RSSIを使用したASK信号の復調時においても、2値化の閾値と比較される入力信号の振幅を一定に保つ。

【解決手段】RSSI検波器17にて復調されたASK信号はピークホールド回路23に入力され、ピークホールド回路23は、充放電部24に入力される入力信号のピーク値を検出し、クリップ回路22は、充放電部24に入力される入力信号のピーク値から一定値以下のレベルをクリップし、充放電部24は、クリップ回路22にてクリップされた信号を用いてコンデンサC2を急速充放電することで、コンパレータ27の閾値として用いられる基準電圧Vrefを発生させる。

(もっと読む)

ピークホールド回路、オペアンプ

【課題】ピークホールド回路を提供する。

【解決手段】入力端子102は、CMOSインバータ103の入力端子に接続されている。CMOSインバータ103の出力端子は、NMOS107のゲートに接続されている。NMOS107のソースは接地され、ドレインは抵抗106の一端、コンデンサ108の一端、CMOSインバータ105の入力端子、および出力端子109に接続されている。抵抗106の他端は、図示されていない駆動電源に接続されている。コンデンサ108の他端は、接地されている。NMOS107は、電圧Vinと電圧Voutに依存してオン、オフが制御される。本発明はピークホールド回路に適用できる。

(もっと読む)

メータ駆動回路

【課題】 ゲインリダクションメータとゲインメータに同じ構成のメータ駆動回路を使用しても、ゲインリダクションメータにおいて圧縮率の極小値を明確に認識できること。

【解決手段】 メータ駆動回路40は、入力されたエンベロープ信号を反転してエンベロープフォロワ部40bに入力することのできる第1の選択部SWaと、エンベロープフォロワ部40bの出力を反転してゲインリダクションメータに供給することのできる第2の選択部SWbを備えている。

(もっと読む)

リミッタアンプ回路

【課題】良好な同相雑音耐性が得られ、入力信号に対する高速応答が可能なリミッタアンプ回路を提供する。

【解決手段】リミッタアンプ回路は、正相入力信号VIPと逆相入力信号VINとからなる差動形式の入力信号を増幅する差動増幅器2と、正相入力信号VIPの最大値と逆相入力信号VINの最大値との電圧差に応じた電流を、差動増幅器2の入力段に設けられた差動回路の1対の負荷抵抗24,25から引き抜くオフセット補償回路(AOC回路3)とを有する。

(もっと読む)

位相調整回路および位相調整方法

【課題】センサ信号の伝達用搬送波の周波数が変動する場合においても、位相シフト量が変動することを防止することが可能である位相調整回路および位相調整方法を提供すること。

【解決手段】三角波変換回路2Gは、パルス列信号VPSINを三角波VCに変換する。三角波振幅制御回路3Gは、三角波VCの振幅値と振幅基準値VPAJとの比較を行い、両者の差分に応じた調整信号ASを三角波変換回路2Gに対して出力する。三角波変換回路2Gは、調整信号ASに応じて三角波VCの傾きを変化させることにより、三角波VCの振幅値を調整する。これによりフィードバックループが構成され、三角波VCの振幅値が振幅基準値VPAJに応じた一定値に維持される。位相シフト回路4は、元のパルス列信号VPSINに対して位相がシフトされたパルス列信号である移相パルス列信号VPSOUTを出力する。

(もっと読む)

二値化回路及び二値化方法

【課題】入力信号を二値化するための二値化回路及び二値化方法に関し、ノイズに対して適切な二値化が行なえる二値化回路及び二値化方法を提供することを目的とする。

【解決手段】本発明は、入力信号を二値化する二値化回路であって、入力信号を微分し、全波整流した波形に整形する波形整形回路(111、112)と、波形整形回路(111、112)で整形された信号の最大値をホールドするホールド回路(113)と、ホールド回路(113)にホールドされた最大値に応じて閾値を生成する閾値生成回路(114)と、波形整形回路(111、112)で整形された信号と閾値生成回路(114)で生成された閾値とを比較する比較回路(115)と、比較回路(115)の比較結果に応じて入力信号を二値化した信号を生成する出力回路(116)とを有することを特徴とする。

(もっと読む)

波形整形回路及びそれを備えた半導体集積回路

【課題】 入力信号を二値波形に整形して出力する波形整形回路において、入力信号の中間電圧等を基準として上下対称にスレッショルド値を調節することができる波形整形回路を提供すること。

【解決手段】 前記入力信号と閾値との比較結果に応じて第1の電圧又は第2の電圧を出力する比較器と、前記閾値を生成する閾値生成部と、を備え、前記閾値生成部は、基準電圧を生成する基準電圧生成部を有し、前記比較器の出力が第1の電圧のときには前記閾値を基準電圧に対して所定値高い電圧に切り換え、前記比較器の出力が第2の電圧のときには前記閾値を前記基準電圧に対して前記所定値低い電圧に切り換える。

(もっと読む)

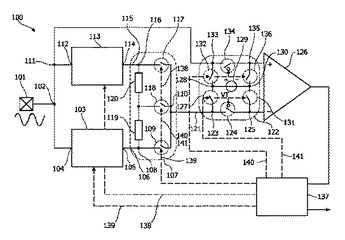

位相検出システム

位相検出システム(100)が、入力端子(101)、第1及び第2ピーク検出器(103,113)、平均化ユニット(107)、オフセットユニット(122)、及び比較器(126)を具えている。入力端子(101)は第1及び第2ピーク検出器(103,113)に結合され、入力信号を位相検出システム(100)に供給する。平均化ユニット(107)は、オフセットユニット(122)と、第1ピーク検出器及び第2ピーク検出器(103,113)の両方との間に結合され、中間信号を発生する。オフセットユニット(122)は入力端子(101)に結合され、信号強度の所定オフセット値を入力信号または中間信号に加えることによって2つの比較可能な信号を発生する。比較器(126)はオフセットユニット(122)に結合され、これら2つの比較可能な信号を比較することによって、入力信号の位相を示す出力信号を発生する。  (もっと読む)

(もっと読む)

データスライサ

【課題】入力信号を適切にスライス可能なデータスライサを実現する。

【解決手段】現在の入力電圧信号の最大値と最小値とだけではなく、入力電圧信号に含まれるヘッダパターンにおける平均電圧と、ヘッダパターン検出完了時のピーク電圧・ボトム電圧とにも基づいて、スライスレベルを算出する。具体的には、スライスレベルをS15、ヘッダパターンの平均電圧をS6、ヘッダパターン検出完了時のピーク電圧をS7、ヘッダパターン検出完了時のボトム電圧をS8、最大電圧検出・保持部に保持された最大電圧をS10、最小電圧検出・保持部に保持された最小電圧をS11として、スライスレベルの電圧値を、S15=S6+(S10+S11)/2−(S7+S8)/2と算出する。

(もっと読む)

1 - 20 / 24

[ Back to top ]