Fターム[5J039MM04]の内容

Fターム[5J039MM04]に分類される特許

1 - 20 / 218

パルス幅延長回路および方法

分周回路およびPLL回路

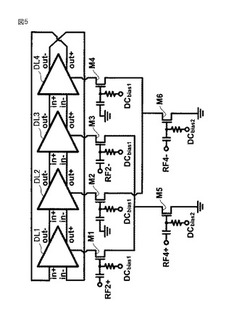

【課題】2分周、8分周、さらには8分周可能な回路規模の小さな低消費電力の注入同期型分周回路の実現。

【解決手段】偶数個Mの遅延要素DL1-DL4を有するリングオシレータ11と、入力発振信号から同期信号を生成して複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を有し、入力発振信号の分周信号を出力する分周回路であって、遅延要素のオン・オフする分周トランジスタの一方の被制御端子が注入ノードであり、同期信号注入回路は、M/2個離れた2つの遅延要素の注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対M1-M4と、入力発振信号RF4+,RF4-が制御端子に入力され、注入差動対の注入ノードとの接続ノードに、入力発振信号の差動信号を発生するように注入差動対に接続された信号注入トランジスタM5,M6と、を有する分周回路。

(もっと読む)

省面積及び省電力のスタンダードセル方法

【課題】省面積及び省電力のための半導体集積回路の設計方法を提供する。

【解決手段】主回路217と適応電圧用調整回路を含む半導体集積回路であって、適応電圧調整用回路は、クロック信号を受け取るように構成された整合回路211と、整合回路211の出力を受け取り、また、クロック信号を受け取るように構成された位相検出器213と、電源電圧を増加又は減少させるように構成された電圧レギュレータ215とを含み、主回路217は電圧レギュレータ215から電源電圧を受け取るように構成され、整合回路211は電源電圧を受け取って、電源電圧における増加又は減少に基づいて、信号伝搬における遅延を調整するように構成される。

(もっと読む)

半導体装置

【課題】分割抵抗回路で消費される消費電力を低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、抵抗分割回路で抵抗分割された分割電圧を受けるための入力端子と、入力端子から供給される分割電圧と、所定の基準電圧と、の電圧差を検出する検出回路と、外部から入力信号を受けるための信号入力端子と、分割電圧と入力信号の電圧を比較するカレントミラー回路と、を備え、カレントミラー回路は、検出回路が検出した電位差に応じて、カレントミラー回路に入力される分割電圧を実効的に補正する電位補正回路と、を含む。

(もっと読む)

チョッパ型コンパレータ

【課題】動作時の貫通電流を低減させ、かつ動作スピードをあまり損なわないチョッパ型コンパレータを得る。

【解決手段】インバータと接地電圧端子間にNチャネル型MOSトランジスタ8を接続し、そのゲート端子に可変電圧源9を接続する。インバータと電源電圧端子間にPチャネル型MOSトランジスタ7を接続し、そのゲート端子に可変電圧源10を接続する。

(もっと読む)

オーバーサンプリング回路及びそれを備えた通信装置

【課題】多相シリアルデータを多相クロックでサンプリングするオーバーサンプリング回路において、遅延量制御動作に伴う消費電流を低減する。

【解決手段】シリアルデータSDATAは、データ遅延部102により多相シリアルデータsdata0〜sdata3とされ、オーバーサンプリング部103において、多相クロックck0〜ck3により、オーバーサンプリングされる。データ遅延部102のデータ遅延素子107の遅延時間は、キャリブレーションデータ発生部101で生成されたデータのオーバーサンプリング出力の位相差をオーバーサンプリング位相検出部105により検出し、その位相差が所望の値となるように、遅延量制御デジタル信号dd_cntを調整する。遅延量制御デジタル信号dd_cntをデジタルアナログ変換部106によりアナログの遅延量発生信号d_cntに変換し、データ遅延素子107に供給する。

(もっと読む)

半導体装置

【課題】不揮発性メモリを備えた半導体装置において、高速動作の場合と低速動作の場合とに切替え可能にするとともに、低速動作時の消費電力を従来よりも削減する。

【解決手段】半導体装置1において、クロック生成回路40は、高周波モード時には低周波モード時よりも周波数の高いクロックを生成する。中央処理装置20は、データバス11を介して不揮発性メモリ10から読み出された読出データを取得する。クロック遅延部50Aは、縦続接続された複数段のバッファ55を介した第1の経路51と複数段のバッファ55を迂回した第2の経路52とを含む。クロック遅延部50Aは、高周波モード時には、クロック生成回路40からのクロックを第1の経路51を介して中央処理装置20に供給し、低周波モード時には、クロック生成回路40からのクロックを第2の経路52を介して中央処理装置20に供給する。

(もっと読む)

コンパレータおよびそれを用いたDC/DCコンバータの制御回路、電子機器

【課題】コンパレータを小型化、および/または、低消費電力化する。

【解決手段】第1電圧V1と第2電圧V2を比較するコンパレータ10が提供される。デプレッション型PチャンネルMOSFETの第1トランジスタM1のソースには、第1電圧V1が、そのゲートには、第2電圧V2が印加される。デプレッション型PチャンネルMOSFETの第2トランジスタM2のソースおよびゲートは、第1トランジスタM1のドレインと接続され、第2トランジスタM2のドレインの電位は固定される。コンパレータ10は、第1トランジスタM1と第2トランジスタM2の接続点N1の電位VN1に応じた出力信号OUTを生成する。

(もっと読む)

コンパレータ回路

【課題】コンパレータ回路において、従来技術に比較して高速で消費電力を低下させる。

【解決手段】入力される2つの入力電圧に応じて、第1及び第2のMOSトランジスタからなる入力差動対のいずれか1つのMOSトランジスタにおいて、当該1つのMOSトランジスタとスイッチトランジスタとを含むループにより適応バイアス電流を発生する入力差動対及び適応バイアス電流発生回路と、上記適応バイアス電流に対応する電流を検出してラッチ論理を変化させた後、上記スイッチトランジスタをオンからオフに切り換えることにより上記適応バイアス電流を遮断するラッチ回路とを備える。

(もっと読む)

電圧検出回路、それを用いた温度検出回路、電子機器

【課題】回路面積、消費電力を低減するとともに、正しい電圧比較が可能な電圧比較回路を提供する。

【解決手段】抵抗ストリング10は、直列に接続された複数の抵抗の接続点に設けられた各タップに電圧を発生する。セレクタ12は、複数のスイッチを含み、ひとつのスイッチがオンした状態において、当該スイッチが接続されるタップの電圧を出力する。コンパレータ14は、入力電圧VINをセレクタ12の出力電圧と比較する。メモリ16_iは、それぞれがしきい値電圧VTHiごとに設けられ、書き込み信号WRITEiに応答してコンパレータ14の出力SCMPを格納して検出信号Siを生成する。シーケンサ20は、N個のメモリ16_1〜16_Nからの検出信号S1〜SNを受け、セレクタ12の複数のスイッチを制御するとともに、書き込み信号を生成する。

(もっと読む)

集積回路

【課題】集積回路において電力消費量を容易に低減する。

【解決手段】集積回路は、クロック分配回路、同期動作回路、論理回路、および、電源供給部を備える。クロック分配回路は、所定のタイミングを指示するクロック信号を分配する。同期動作回路は、クロック信号に同期して動作する。論理回路は、同期動作回路の動作結果に基づいて所定の論理演算を実行する。電源供給部は、クロック分配回路を駆動させるクロック分配回路駆動電圧より低い電圧を論理回路に論理回路駆動電圧として供給する。

(もっと読む)

集積回路

【課題】電力消費量の増大を抑制しつつ、タイミング信号のスキューを低減する。

【解決手段】第1のクロック分配回路は、タイミング信号を複数の第1の分配点に分配する。第2のクロック分配回路は、タイミング信号を複数の第2の分配点に分配する。最小遅延クロック信号出力部は、複数の第1の分配点のいずれかに分配されたタイミング信号と複数の第2の分配点のいずれかに分配されたタイミング信号とのうち遅延が小さい方の信号を最小遅延タイミング信号として出力する。同期動作回路は、最小遅延タイミング信号に同期して動作する。

(もっと読む)

クロック生成回路、及びクロック生成方法

【課題】一種類の多相クロックより多くの周波数の種類の単相クロックを得ることができるクロック生成回路及びその方法を提供する。

【解決手段】少なくともn個の位相補間器を有し、周波数がfで位相差が1/(f×m)づつ異なるm相クロックを、周波数がfで位相差が1/(f×n)づつ異なるn相クロックに変換するクロック変換回路1と、前記n相クロック信号の一部又は全部を用いて、周波数(f×n)/Aの単相クロック信号を生成する単相クロック生成回路2と、前記位相補間器に設定する内分比を制御する制御回路とを有し、前記各位相補間器は、前記m相の内の異なる二つのクロックを入力し、それらのタイミング差を、制御回路により設定した内分比で分割した遅延時間のクロックを生成して出力し、前記制御回路は、基準クロックと、回路の末端で分配されたクロックとのタイミングとが一致するように内分比を制御する。

(もっと読む)

PLL回路

【課題】低消費電力のPLL回路を提供する。

【解決手段】位相比較回路11は、基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号(UP信号とDN信号)をチャージポンプ12に供給し、バイアス回路16は、チャージポンプ12にバイアス電流を供給し、制御回路17は、2種の位相差信号のうち一方または両方が活性化状態のときにバイアス回路16の動作を行わせ、2種の位相差信号の両方が非活性化状態のときに、バイアス回路16を停止させる。

(もっと読む)

インターフェイス回路

【課題】ホスト機器とサブ機器との間の双方向データ伝送を行うインターフェイス回路において、待機時の消費電流をゼロにする機能を実現し、かつ安定した起動シーケンスを実現する。

【解決手段】ホスト機器1側で、差動信号の電位は、アイドル/スタンバイ状態においてプルアップ素子4によって電源電位にプルアップされている。ノーマル状態に移行するとき、差動信号が出力されるにつれて、コモンモード電位が電源電位から徐々に低下していく。サブ機器2側では、レベル検知回路10によってコモンモード電位が所定レベルよりも下がったことを検知したとき、ノーマル状態になったと判断し、起動する。レベル検知回路10は、通常状態で消費電流が生じないバッファタイプの回路構成で実現される。

(もっと読む)

位相周波数比較回路

【課題】雑音特性及び高速動作を維持しながら、消費電力を削減することができる位相周波数比較回路を得ることを目的とする。

【解決手段】出力バッファ回路3が、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力する。

(もっと読む)

遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法

【課題】簡易な処理によって遅延素子の遅延情報を出力する遅延検出回路、電源電圧設定回路、及び、遅延検出回路の制御方法を提供すること。

【解決手段】本発明にかかる遅延検出回路10は、基準信号生成部11と、遅延チェーン12と、保持部13と、を備える。基準信号生成部11は、クロック信号に同期して第1のレベルから第2のレベルに変化し、少なくともクロック信号の一周期の間は第2のレベルが維持される基準信号を生成する。遅延チェーン12は、多段接続された複数の遅延ゲート12−1〜12−nを有し、基準信号が入力される。保持部13は、クロック信号に同期して複数の遅延ゲート12−1〜12−nの出力信号を保持し、前記遅延手段の遅延情報を出力する。

(もっと読む)

半導体集積回路

【課題】電源が遮断されてもデータが保持される新規な論理回路を提供する。また、消費電力を低減できる新規な論理回路を提供する。

【解決手段】2つの出力ノードを比較する比較器と、電荷保持部と、出力ノード電位確定部とを電気的に接続することにより、論理回路を構成する。それにより、電源が遮断されてもデータが保持される論理回路を得ることができる。また、論理回路を構成するトランジスタの総個数を低減させることができる。更に、酸化物半導体を用いたトランジスタとシリコンを用いたトランジスタを積層させることで、論理回路の面積の削減が可能になる。

(もっと読む)

同期信号処理装置

【課題】回路の小面積化、低消費電力化を図ることが可能であり、しかも温度依存性の影響を受けない安定した位相比較が可能な同期信号処理装置を提供する。

【解決手段】水平同期信号を同期クロックで同期させ、当該同期クロックのタイミングでデジタルデータとして出力する時間デジタル変換器(TDC)と、同期クロックをカウントして参照クロックを生成する参照クロック生成部と、TDCによるデジタルデータと参照クロックの位相比較を行うことにより位相差情報を得るデジタル位相比較器と、デジタル位相比較器の位相差情報に応じて上記参照クロックとTDCによる水平同期信号のデジタルデータの位相が一致するように周波数が制御される同期クロックを生成する同期クロック生成装置と、を有する。

(もっと読む)

比較回路及びアナログデジタル変換回路

【課題】動作電圧に対して入力電圧範囲を拡大し、低消費電力化を図ること。

【解決手段】比較回路10の電圧制御部12は、キャパシタC11の第1端子に、クロック信号CKに応答して高電位電圧AVDと低電位電圧(グランドGND)を供給する。キャパシタC11の第2端子に接続されたトランジスタT23は、反転クロック信号XCKに応答してオンオフする。入力トランジスタT11,T12のしきい値電圧と等しく設定されたトランジスタT23は、グランドGNDの電圧とノードN21の電圧に応じて反転状態となり、比較部11に供給する制御電圧VCM(ノードN21の電圧)をグランドGNDからトランジスタT23のしきい値電圧低い電圧に安定させる。

(もっと読む)

1 - 20 / 218

[ Back to top ]