Fターム[5J042CA16]の内容

Fターム[5J042CA16]に分類される特許

1 - 20 / 45

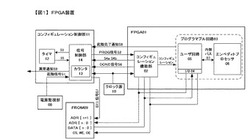

FPGAのコンフィギュレーション制御回路、FPGA装置及び方法、並びに、コンフィギュレーションデータ更新方法

【課題】メモリ領域に格納されているコンフィギュレーションデータを直接読み出してコンフィギュレーションを実施するFPGAのコンフィギュレーションを高い信頼性をもって確実に行えるコンフィギュレーション制御回路、FPGA装置及び方法を提供する。

【解決手段】FROM12には、同じ内容のコンフィギュレーションデータが複数個格納されている。信号制御部08が、FPGA01にコンフィギュレーションのトリガを与えると、FPGA01は、FPGA01がデータの読み出し先として指定するFROM12の指定領域に格納されているデータを読み出して、コンフィギュレーションを行う。コンフィギュレーションが失敗した場合には、信号制御部08は、FROM12の指定領域を切り替え、FPGA01がFROM12の切り替え後の指定領域から別のデータを読み出してコンフィギュレーションするためのトリガをFPGA01に与える。

(もっと読む)

プログラマブルロジック集積回路デバイスの相互接続ならびに入力/出力リソース

【課題】プログラマブルロジックデバイスに適用してプログラマブルロジックアレー集積回路デバイスの動作速度を増加するための相互接続リソースの提供。

【解決手段】プログラマブルロジック集積回路(10)は、交差する複数の領域の行および列からなる配列をもって、デバイス上に配置された複数のプログラマブルロジック領域(20)を有する。領域から領域へおよび/または領域間におけるプログラム可能な相互接続を形成するための相互接続リソース(例えば、相互接続コンダクタ等)が設けられ、これらのうちの少なくともいくつかは、構造的には類似であるが著しく異なる信号伝送速度特性を有する2つの形式で構成される。例えば、これらの双対形式相互接続リソースのうちの主要なまたは大きな部分(200a,210a,230a)はノーマル速度と呼ばれるものであり、少ないほうの部分(200b,210b,230b)は大幅に高速な信号速度を有する。

(もっと読む)

リコンフィギュラブル回路及びリコンフィギュラブル回路の駆動方法

【課題】単純な回路構成により演算実行のレイテンシを吸収できるリコンフィギュラブル回路を提供する。

【解決手段】リコンフィギュラブル回路は、複数のデータが全て同時に有効状態になると複数のデータに対して演算を実行し、複数のデータが全て同時に有効状態である間、演算により得られた演算結果を示す有効状態のデータを出力し続ける演算器を、複数個含むデータ演算部と、演算器間を再構成可能に接続するデータ選択部と、一連の演算を実行するようにデータ選択部により接続された一連の演算器に入力されるデータを入力データして保持するデータ入力部とを含み、データの有効及び無効状態は該データに対として付随する有効及び無効を示す信号により示され、一連の演算を実行する間はデータ入力部からデータ演算部に供給されている入力データを有効状態の同一データに固定しておく。

(もっと読む)

コンフィグレーション方法及びコンフィグレーション制御回路

【課題】コンフィグレーション方法及びコンフィグレーション制御回路において、FPGA回路のクロック周波数やスルーレート等のコンフィグレーションデータを自動調整可能にすることを目的とする。

【解決手段】FPGA回路のコンフィグレーションを行うコンフィグレーション方法において、コンフィグレーション回路からFPGA回路にコンフィグレーションデータを設定するコンフィグレーションが失敗した回数をFPGA回路内でカウントし、前記回数が上限値以下であると前記コンフィグレーションが失敗した時の前記コンフィグレーションデータを予め設定されているルールに従ってFPGA回路内で調整してコンフィグレーションを再実行し、前記コンフィグレーションが成功すると、成功した時点のコンフィグレーションデータをFPGA回路からコンフィグレーション回路に設定するように構成する。

(もっと読む)

プログラマブルロジックデバイス回路に結合されるクロックデータリカバリ回路

【課題】プログラマブルロジックデバイス上またはこれと結合して設けられるクロックデータリカバリ回路の提供

【解決手段】プログラマブルロジックデバイス(“PLD”)が多数のCDRシグナリングプロトコルのうちの任意のものによって交信することを可能にするため、このPLDにプログラマブルクロックデータ復元(“CDR”)回路を装備する。CDR回路は、PLD内に内蔵するか、完全あるいは部分的に独立した集積回路とすることができる。この回路は、CDR入力、CDR出力、またはそれらの両方を行うことができる。CDR機能は、例えば非CDR低電圧作動シグナリング(“LVDS”)等のその他の非CDRシグナリング機能と組合わせて提供することができる。この回路は、大規模なシステムの一部とすることができる。

(もっと読む)

FPGAの異常診断方法及び装置

【課題】充分に高い診断精度を確保することが可能なFPGAの異常診断方法及び装置を提供すること。

【解決手段】FPGA1を構成する全ての回路ブロックCIRa〜CIRdにはそれぞれカウンタCOUa〜COUdが設けられており、これらはカウンタCOUa,COUb,COUd,COUcの順に順次直列接続されてカウンタ直列接続体を形成している。発振器2からの発振信号は、I/OブロックIOaの入力ピンを介してカウンタCOUaに入力され、また、カウンタCOUcからは、I/OブロックIOcの出力ピンを介して、順次分周された発振信号がカウンタクリア信号としてウォッチドッグタイマ3に出力される。ウォッチドッグタイマ3の動作に基づき正常と診断した場合には、全ての回路ブロックが必ず正常であることが保証される。

(もっと読む)

半導体装置

【課題】回路構成を再構成可能であるとともに、同時に複数のアプリケーションを実行することを可能にする半導体装置を提供する。

【解決手段】コンフィグレーションデータの保持用及び演算処理の結果の保持用に同じバンク数のレジスタバンクを設け、バンク切り替え信号によりレジスタバンクのバンクを同期して切り替えるようにして、アプリケーションの切り替えに応じて、コンフィグレーションデータ及び処理に用いるデータを同期して切り替えて処理を実行可能にし、同時に複数のアプリケーションを実行できるようにする。

(もっと読む)

リコンフィギュラブル回路及びリコンフィギュラブル回路システム

【課題】内部動作が停止した場合に外部バッファと適切にデータのやり取りが可能なリコンフィギュラブル回路を提供する。

【解決手段】リコンフィギュラブル回路は、複数の演算器と該演算器間を再構成可能に接続するネットワーク回路とを含むリコンフィギュラブル演算器アレイと、リコンフィギュラブル演算器アレイの動作の実行及び停止を制御する停止制御回路と、リコンフィギュラブル演算器アレイの動作の停止時に外部から供給されるデータを一時的に格納し、リコンフィギュラブル演算器アレイの動作の再開時に格納されたデータをリコンフィギュラブル演算器アレイに供給するバッファ回路とを含むことを特徴とする。

(もっと読む)

パルス遅延回路の構成方法

【課題】プログラマブルロジックデバイス上に、遅延ユニット毎の遅延時間のばらつきの少ないパルス遅延回路を構成する。

【解決手段】FPGAには、1列に配置された複数のロジックセルからなるセル列が多数設けられており、同一のセル列に属する二つのロジックセル間の伝送(以下「同セル列内伝送」という)と、異なるセル列に属する二つのロジックセル間の伝送(以下「異セル列間伝送」という)とでは、遅延が異なったものとなる。ストレートディレイラインを構成する遅延ユニットR1〜RnをFPGAに実装する際にマニュアルで配置する。具体的には、遅延ユニットR1〜Rnを隣接するn個のセル列CC1〜CCnに一つずつ割り当て、しかも、遅延ユニットR1〜Rnが、その接続順に並ぶように、セル列CCi(i=1,2,…,n)に遅延ユニットRiを割り当る。

(もっと読む)

FPGAのコンフィギュレーション回路

【課題】 FPGAをコンフィギュレーションする際に、コンフィギュレーション専用フラッシュROMを用いていたが、このフラッシュROMの起動時間が長いのでコンフィギュレーションに時間がかかり、FPGAが起動するまでの時間が長くなってしまうという課題を解決する。

【解決手段】 2バイト以上のデータバス幅を有する汎用メモリにコンフィギュレーションデータを書き込み、このメモリの出力を一括してラッチ回路に取り込み、バイト単位でFPGAに出力するようにした。FPGAのコンフィギュレーション準備時間待つだけでコンフィギュレーションを開始することができるので、FPGAの起動時間を短くすることができる。また、複数バイトのデータを一括してラッチ回路に取り込み、このラッチ回路からバイト単位でFPGAにコンフィギュレーションデータを出力するようにしたので、フラッシュROMのようなアクセス時間が長くかつ安価なメモリを使用することができる。

(もっと読む)

半導体集積回路

【課題】エラー検出のためのハードウエア上のオーバーヘッド及び時間的オーバーヘッドを小さくでき、且つエラーを発生した論理素子を特定できる半導体集積回路を提供することを第1目的とする。また、ダイナミック回路のリセット時間による時間的オーバーヘッドを隠蔽でき、実効的な演算スループットを向上させる半導体集積回路を提供することを第2目的とする。

【解決手段】本発明に係る半導体集積回路は、論理素子単位でのハンドシェークを実施し、論理素子単位でのエラー発生の検出を行うことで後段の論理素子にエラー伝搬を行わないこととした。さらに、本発明に係る半導体集積回路は、各論理素子内で同一の論理回路を並列に接続し、2相で動作させることとした。

(もっと読む)

カウント装置

【課題】 カウント入力回路への被カウント信号配線は変更することなく、その被カウント信号をカウントするカウンタを変更したり、あるいは1のカウンタ入力回路へ供給される被カウント信号を、複数のカウンタへ並列に供給することを可能とする。

【解決手段】 入力回路(11−1〜4)の各出力端とカウンタ(13−1〜4)の各入力端との間には分配切替回路(12)が介在され、分配切替回路は、入力回路の各出力端のそれぞれに接続される入力側端子(IN0〜IN1)と、カウンタの各入力端のそれぞれに接続される出力側端子(OUT1〜OUT4)とを有し、かつ入力側端子のそれぞれと出力側端子のそれぞれとの間における導通又は非導通は、任意に設定可能とされる。

(もっと読む)

半導体集積回路及びその制御方法

【課題】外部から故障原因を特定可能な半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路100は、電源投入を検出する検出信号Sdに基づいて、リセット信号Srを出力するパワーオンリセット回路11と、リセット信号Srに基づいて、初期設定が行われる初期化対象回路12と、パワーオンリセット回路12から出力されたリセット信号Sr及び初期値が設定された初期化対象回路11の出力信号Soに基づいて、リセット信号Srをモニタするパワーオンリセットモニタ信号Smを生成して出力するパワーオンリセットモニタ回路13と、を備えている。

(もっと読む)

動的再構成回路およびデータ送信制御方法

【課題】コンテキストの切り換え内容に応じた最適なクラスタ間のデータ送信を実現する。

【解決手段】リコンフィグ回路100は、再構成可能なPE(プロセッシングエレメント)の集合からなるクラスタ110を複数備え、PEの処理内容とPE間の接続内容が記述されたコンテキストに応じて、クラスタ110の構成を動的に切り換え可能である。そして、各クラスタ110は、コンテキストの切り換え指示を受け付けると、当該切り換え指示をあらわす報知信号であるインヒビット信号を生成するインヒビット信号生成回路340と、クラスタ110から他のクラスタ110へ送信する出力データに生成された報知信号を付加するインヒビット信号付加回路350と、他のクラスタ110によって生成された報知信号が付加された出力データが送信されてきた場合に、この出力データのクリア処理をおこなう入力データクリア回路360とを備えている。

(もっと読む)

デューティ補正回路

【課題】伝送速度が異なる複数のマンチェスタ符号化信号のデューティ比を補正可能なデューティ補正回路を得ること。

【解決手段】本発明にかかるデューティ補正回路は、マンチェスタ符号化された受信信号の連続する2つの立上りエッジの間隔または立下りエッジの間隔に基づいて受信信号の伝送速度を判定するシンボル周期判定回路7と、受信信号の“Hレベル”または“Lレベル”の継続時間を観測するエッジ検出回路2およびカウンタ3と、観測結果および判定結果に基づいて波形歪みを検出する波形歪み検出回路4と、波形歪みが検出された場合に波形歪み発生期間、受信信号を反転することにより波形の補正を行うセレクタ5と、を備えることとした。

(もっと読む)

半導体回路およびトリミング方法

【課題】チップサイズをほとんど変えずに仮トリミングを可能とする半導体回路を実現する。

【解決手段】n個のトリミング回路1A〜1Cと、n個のトリミング回路1A〜1Cが接続される被調整回路4とを有する半導体回路において、セレクタ回路2と、n個のフリップフロップ回路3A〜3Cとを備え、セレクタ回路2を第1のモードに設定することで、n個のトリミング回路1A〜1Cがそれぞれn個のフリップフロップ回路3A〜3Cを経由して被調整回路4に接続され、セレクタ回路2を第2のモードに設定することで、n個のフリップフロップ回路3A〜3Cnビットのカウンタ回路3を構成し、カウンタ回路の3出力が被調整回路4に接続されるようにする。

(もっと読む)

信号処理回路およびインターフェイス回路

【課題】SSPDをアレー化した場合のSSPDピクセルの信号処理による熱負荷増大に対して適切に対応できる信号処理回路およびインターフェイス回路を提供する。

【解決手段】本発明の信号処理回路20Aにおいては、複数の超伝導ナノワイヤ型単一光子検出器100Aから出力される信号の処理に用いられ、単一磁束素子により構成された論理回路(21、22)が組み込まれている。

(もっと読む)

半導体集積回路装置及びアイ開口マージン評価方法

【課題】 高速シリアルデータ受信回路のアイ開口マージン評価として、クロック相を固定せず、クロックデータリカバリー回路の動作を含んだアイ開口マージン評価回路を提供する。また、位相情報にオフセットを与えることでジッタ成分を付加し、受信データエラー加速試験を可能にする。

【解決手段】 シリアルデータを受信するシリアライザ・デシリアライザ回路201(SerDes)と、並走クロック信号を受信する参照シリアライザ・デシリアライザ回路202(Ref_SerDes)とを有し、シリアライザ・デシリアライザ回路201(SerDes)は、参照シリアライザ・デシリアライザ回路202(SerDes)の生成した位相制御信号P_CSを用いて位相制御された再生クロックにより受信したシリアルデータの直列並列変換を行う。位相制御信号P_CSに、パルス生成回路602からのオフセット調整パルスOffset_Pulseを印加することで、アイ開口マージン評価を行う。

(もっと読む)

データ処理装置

【課題】再構成可能な論理回路の再構成時間を短縮し、データ処理の高速化は図ることができるようにしたデータ処理装置を提供する。

【解決手段】回路情報源15に論理回路Bの論理回路Aとの差分回路情報W(A→B)を保持させる。論理再構成制御部16は、再構成可能な論理回路12に論理回路Aを再構成して論理回路Aに任されている処理を実行させた後、再構成化可能な論理回路12に論理回路Bを構成する場合、回路情報源15から論理回路Bの論理回路Aとの差分回路情報W(A→B)を読み出し、再構成可能な論理回路12内の再構成を必要とする番地の情報と、再構成する番地の回路情報とを回路情報保持レジスタ19に転送する。

(もっと読む)

カウンタ回路、動的再構成回路およびループ処理制御方法

【課題】高級言語によって記述されたループ処理を実装可能とするとともに、コンテキストの切り替えを適切におこなえるカウンタ回路を含んだ動的再構成回路およびループ制御処理方法を実現する。

【解決手段】再構成可能なPE(プロセッシングエレメント)111の処理内容と接続内容をコンテキストに応じて動的に切り替えることにより任意の処理を実行させる動的再構成回路100は、コンテキストに基づいて、再構成されたPEの集合からの出力信号の出力元、出力信号の出力先、および出力信号を出力先に出力する条件からなるループ処理の内容を設定するコンフィグレーションデジスタ部と、設定されたループ処理を実行するとともに、ループ制御部によって実行されたループ処理の実行回数をカウントし、カウントされた実行回数および条件に基づいて、出力信号を出力先に出力するループ制御部および出力レジスタ部からなるカウンタ回路112を備えている。

(もっと読む)

1 - 20 / 45

[ Back to top ]