Fターム[5J043BB01]の内容

Fターム[5J043BB01]の下位に属するFターム

デジタル発振器 (41)

Fターム[5J043BB01]に分類される特許

1 - 20 / 42

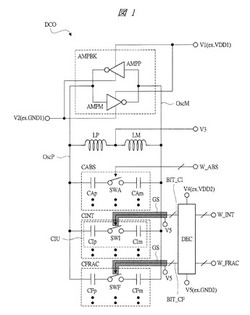

ディジタル制御発振装置および高周波信号処理装置

【課題】DNLの低減を実現可能なディジタル制御発振装置を提供する。

【解決手段】例えば、発振出力ノードOscP,OscM間に並列に結合されるアンプ回路ブロックAMPBK、コイル素子LP,LM、複数の単位容量ユニットCIU等を備え、各CIUは、容量素子CIp,CImと、当該CIp,CImを発振周波数の設定パラメータとして寄与させるか否かを選択するスイッチSWIを備える。ここで、SWIは、デコーダ回路DECからのオン・オフ制御線BIT_CIによって駆動され、当該BIT_CIは、シールド部GSによってOscP,OscMとの間でシールドされる。

(もっと読む)

発振回路、発振装置およびクロックジェネレータ

【課題】消費電力を低減することができる発振回路を提供する。

【解決手段】入力信号が含むアナログ成分をデジタル信号に変換するアナログ/デジタル変換回路100と、アナログ/デジタル変換回路100で変換されたデジタル信号D1について、予め設定された周波数帯域成分のみを基準信号として通過させるバンドパスフィルタ101と、バンドパスフィルタ101を通過した基準信号D2と、PLLループ内に設けられる電圧制御発振器203からの出力信号D3との位相差が一定となるように電圧制御発振器203にフィードバック制御を行って発振させるPLL回路200とを備え、バンドパスフィルタ101は、所定の条件に基づいて、アナログ/デジタル変換回路100で変換されたデジタル信号D1の所定ビット幅について、「0」に固定するマスク処理を実行するマスク処理部102を備える。

(もっと読む)

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

発振周波数補正装置

【課題】同期信号の検出が困難なときにも正確な発振周波数のクロック信号を生成できるようにした発振周波数補正装置を提供する。

【解決手段】電源投入時の劣化検出タイミングにおいて、定電流源23から抵抗器22に通電して得られたA/D変換器6のAD変換値(抵抗器22の端子電圧VR)に基づいて、CPU2が逓倍数設定値FMULRを補正する。この場合、定電流源20を用いることなく定電流源23が作動して抵抗器22に通電する。CPU2は、抵抗器22の端子電圧を測定することでCR発振器14内の抵抗器R1の抵抗値の経年変化を反映し、この変化に基づいてCR発振回路8のクロック信号CLKの逓倍数設定値FMULRを補正する。

(もっと読む)

電子回路

【課題】発振回路部の信号反転素子及びインターフェース回路部のインターフェース回路部のインターフェース集積回路素子で消費される電流を抑えて消費電力が少ない電子回路を提供する。

【解決手段】発振回路部とインターフェース回路部と被駆動回路部と備えた電子回路であって、発振回路部用電源電圧印加端子と発振回路部の間に発振回路部用電流制限抵抗が設けられ、インターフェース回路部用電源電圧印加端子とインターフェース回路部との間にインターフェース回路部用電流制限抵抗が設けられ、発振回路部用電流制限抵抗の両端部からグランドに接続されている第一のコンデンサが設けられ、インターフェース回路部用電流制限抵抗の両端部からグランドに接続されている第二のコンデンサが設けられ、インターフェース回路部から出力され被駆動回路部に入力される信号電圧が被駆動回路部が動作するために必要な電圧より大きいことを特徴とする。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

大きな温度変動に対する発信周波数の安定化方法

【課題】

超高温から極低温までの温度変動が極めて大きい環境に設置される無線機器に適用できる発信周波数の安定化方法を提供する。

【解決手段】

複数の発信回路を備え、筐体内の温度を測定する筐体内温度測定ステップと、測定した筐体内温度Tと予め定められた温度T0、T1、・、Tk、・Tnとの大小関係から測定した温度範囲を判定する温度範囲判定ステップと、 温度範囲判定ステップが判定した温度範囲に応じて複数の発信回路のいずれかを選択する回路選択ステップとを有し、筐体内温度TがTk−1≦T<Tkの範囲であった場合に、回路選択ステップは当該温度範囲において、発信器の発信周波数が希望の範囲に納まるように予め調整されている発信回路等を選択する。

(もっと読む)

半導体装置

【課題】クロック周波数の設定を変えた場合でも電源や温度などに変動があっても、高精度なクロック信号を生成する。

【解決手段】周波数電圧変換回路13は、スイッチSW1,SW2から構成されるスイッチ部、静電容量素子C,C10〜C13、およびスイッチCSW0〜CSW3から構成されている。静電容量素子C10〜C13は、容量の絶対値が異なるもので構成され、設計者が意図する周波数範囲をカバーするよう設ける。静電容量値は、たとえば、2の重み付けがされている静電容量素子C11〜C13は、たとえば、4ビットの周波数調整制御信号SELC0〜SELC3に基づいて、スイッチCSW0〜CSW3が選択し、周波数の切り替えを行う。

(もっと読む)

発振回路

【課題】発振周波数の精度を改善することが可能な発振回路を提供すること。

【解決手段】PTAT出力とCTAT出力とを加算して出力する基準電圧発生回路と、加算割合を切り替え温度に依存した基準電圧発生回路の出力の変動を最小化する第1切替手段と、基準電圧発生回路の出力に基づいて定電流を発生させる電流源と、基準電圧発生回路の出力に基づいて定電圧を発生させるレギュレータ回路と、一端が電流源に接続され電流源の定電流によって充放電される第1容量及び第2容量と、レギュレータ回路から供給される定電圧を電源として第2容量の他端を駆動するインバータと、電流源の定電流の値を切り替え発振周波数を調整する第2切替手段と、第1容量の容量値を切り替え第1容量及び第2容量の一端における発振振幅を調整する第3切替手段と、を備え、第1切替手段、第2切替手段、第3切替手段のトリミングによって所望の大きさの一定周波数を生成する。

(もっと読む)

タイマ

【課題】タイマにおいて、簡易な構成を実現しつつ、実時間の計測精度をより向上させることにある。

【解決手段】次回の停止時間T11は、記憶部36に記憶される周波数(前回の周波数)と、周波数演算部31により演算された周波数(今回の周波数)との差分及び前回の停止時間に基づき算出される。従って、前回の周波数と、今回の周波数との差分が大きい場合、例えば、温度変化が大きい場合には、次回の停止時間が短く設定される。このため、周波数の差分が大きい場合には周波数の補正の頻度が上がる。

(もっと読む)

半導体装置

【課題】周囲温度や外部電源電圧の変化による高速OCOに与える参照電圧および参照電流の変動を防止し、電源モジュールの回路面積が小さい半導体装置を提供する。

【解決手段】高速OCO10は、参照電流および参照電圧で定まる大きさの高速クロックを出力する。温度センサ5は、高速OCO10の周囲温度を検出し、電圧センサ4は、高速OCO10の動作電圧を検出する。電源モジュール12は、BGRを含み、BGRが出力する基準電圧に基づいて、参照電圧、参照電流、高速OCOの動作電圧を生成する。フラッシュメモリ8は、高速OCO10の周囲温度および動作電圧に対応する、参照電圧および参照電流のトリミングコードを定めたテーブルを記憶する。ロジック部13は、検出された周囲温度および動作電圧に対応する参照電圧および参照電流のトリミングコードに基づいて、参照電流および参照電圧の値を調整する。

(もっと読む)

高周波信号出力装置、該高周波信号出力装置に用いられる信号出力方法及び信号出力制御プログラム

【課題】出力タイミングの1ヒット目から安定した規定値の高周波信号を出力する高周波信号発生装置を提供する。

【解決手段】高周波信号発生部11で高周波信号shが発生し、同高周波信号shでは、制御部13により設定された周波数、パルス幅及び出力レベルを有するバースト状のパルスが発生するバースト期間と同パルスが発生しない非バースト期間とが、パルス発生部12により設定されたパルス繰返し周波数で交互に繰り返される。制御部13により、高周波信号発生部11に動作開始制御信号caが与えられると共に、高周波出力制御部14により、所定時間が経過するまで高周波信号発生部11の出力側が終端される一方、同所定時間が経過した後、高周波信号発生部11から出力されている高周波信号shのパルスが1ヒット目から外部へ送出される。

(もっと読む)

スピン素子を使用した弛緩発振器

【課題】スピン素子を使用した弛緩発振器を提供する。

【解決手段】弛緩発振器は、電源を印加する電源部と、該電源部から印加される電源によって駆動されるスピン素子と、該スピン素子に並列に連結されるキャパシタとを含む。スピン素子は、磁場の強さによって可変な可変電圧値を有する。キャパシタは、前記スピン素子が臨界電圧範囲の最小電圧値を有すると放電し、スピン素子が前記臨界電圧範囲の最大電圧値を有すると充電する。従って弛緩発振器は、製作に必要な部品の個数が少なくて回路が単純化され、製造費用と消費電力が少ない。よって弛緩発振器は、広範囲な周波数帯域の調節が可能で活動範囲が広く、磁化反転を使用することによって高出力が可能であるという効果がある。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

発振器

【課題】発振周波数が一定なパルス信号を出力可能な発振器を提供する。

【解決手段】コンデンサCの一方の電極に接続される第1スイッチ素子Q1の開閉状態と、コンデンサCの他方の電極に接続される第2スイッチ素子Q2の開閉状態とを、コンデンサCの充放電に応じて変化する端子間電圧に基づいて交互に切り替えて所定の周期を有するパルス信号を出力する発振器100は、第1スイッチ素子Q1の開閉状態を制御する制御信号を出力する制御信号出力部10と、第1スイッチ素子Q1の閉状態への移行に応じて、第1スイッチ素子Q1を閉状態にする制御信号の信号レベルを保持する閉信号レベル保持部11と、第2スイッチ素子Q2の閉状態への移行に応じて、第1スイッチ素子Q1を開状態にする制御信号の信号レベルを保持する開信号レベル保持部12と、を備える。

(もっと読む)

発振回路

【課題】振動子の安定発振を早める発振回路に関する技術を提供するとともに、それを用いた超音波流量計を提供する。

【解決手段】共振周波数を有する振動子1と、前記振動子に接続されるアンプ2と、付勢パルス発生手段3と、前記付勢パルス発生手段3と前記振動子1およびアンプ2との接続・非接続とを切替える切替え手段4とを備え、前記振動子1の駆動初期は前記切替え手段4により、前記振動子1と前記付勢パルス発生手段3とを接続するようにした発振回路。

(もっと読む)

半導体集積回路、温度変化検出方法

【課題】少量の追加回路で温度変化を検出する温度変化検出回路を提供する。

【解決手段】半導体集積回路010は、温度に依存する出力電圧Vregを発生する電圧発生回路400と、Vregが印加されるVCOを含むPLL500と、VCOの発振を制御するVCO発振制御電圧Vcntのレベル変化を基に検出信号Cupを出力するVcnt検出回路200とを含む。PLL500のVCO560に、電圧発生回路400からのVregが印加される。Vregの大きさにより、VCO560の発振周波数が変化する。すなわち、温度によりVCO560の発振周波数が変化する。PLL500のループのフィードバック動作により、VCO560に入力するVCO発振制御電圧であるVcntの電圧レベルが変化する。そして、Vcnt検出回路200が、Vcntのレベル変化を検出することにより温度変化を検出する。

(もっと読む)

基準クロック補正回路、基準クロック補正方法およびプログラム

【課題】基準信号を切り替えても発振器を自走状態にさせることの少ない基準クロック補正回路を提供する。

【解決手段】本発明に係る基準クロック補正回路1は、複数の基準信号の各々の安定度が良好であるか否かを判断する複数のクロック安定度検出部21a〜cと、複数の基準信号の中で安定度が良好である基準信号を選択基準信号102とする基準信号設定部22と、選択基準信号と基準クロック信号101を用いて制御値105を算出する発振器制御部12と、制御値に基づいて基準クロック信号を発振する発振器13とを有する。

(もっと読む)

発振回路

【課題】温度補償回路に発振部の出力がノイズとして入力しない発振回路を提供する。

【課題の解決手段】周囲温度に応じた制御信号によって出力周波数が制御される発振部1と、この発振部1に制御信号を供給する温度補償回路2と、発振部1の発振出力と温度補償回路2の温度センサ出力のいずれかを出力するようオンオフ制御される出力バッファ4と温度センサ出力スイッチ3からなる切換スイッチ回路とを備え、温度センサ出力スイッチ3は、トランスファーゲートスイッチ301,302を2段直列に接続し、この接続点に固定電位に接続した第3のスイッチ303を介在させてなり、発振出力を出力する時はトランスファーゲートスイッチ301,302をオフとして、第3のスイッチ303をオンとし、温度センサ出力を出力する時はトランスファーゲートスイッチ301,302をオンとして、第3のスイッチ303をオフとする。

(もっと読む)

1 - 20 / 42

[ Back to top ]