Fターム[5J055AX21]の内容

Fターム[5J055AX21]の下位に属するFターム

ノイズ対策 (690)

Fターム[5J055AX21]に分類される特許

1 - 20 / 87

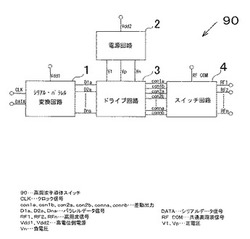

高周波半導体スイッチ、端末装置

【課題】スイッチ回路の誤動作の発生を防止する。

【解決手段】一つの実施形態によれば、シリアル・パラレル変換回路は、第一の高電位側電源が供給され、シリアルデータ信号が入力され、パラレルデータ信号を生成する。電源回路は、第二の高電位側電源が供給され、第二の高電位側電源に基づいて第一の正電圧、第二の正電圧、及び負電圧を生成する。ドライブ回路は、第一の正電圧が電源として供給され、パラレルデータ信号が入力されるインバータと、第二の正電圧及び負電圧が電源として供給され、パラレルデータ信号及びインバータの出力信号が入力される差動型レベルシフタを含むレベルシフト回路が設けられ、第二の正電圧をハイレベルの信号としてスイッチ回路に出力し、負電圧をローレベルの信号としてスイッチ回路に出力する。

(もっと読む)

リセット信号生成回路及びそれを備えた半導体集積回路

【課題】電源投入後から外部リセット信号が最初にアクティブになるまでの期間にリセット信号をアクティブにすることが可能なリセット信号生成回路を提供すること。

【解決手段】本発明にかかるリセット信号生成回路101は、外部リセット信号が最初にアクティブになったことを検出する外部リセット検出回路102と、外部リセット検出回路102の検出結果が、外部リセット信号が最初にアクティブになる前であることを示す場合、外部リセット信号に関わらずリセット信号をアクティブにする制御回路と、を備える。

(もっと読む)

入力装置

【課題】主に自動車内の各種電子機器の操作に用いられる入力装置に関し、誤検出がなく、確実な操作が可能なものを提供することを目的とする。

【解決手段】第一の端子17と第二の端子18の間に複数のダイオード13〜16を直列に接続すると共に、第一の端子17とダイオード13〜16に複数のスイッチ5〜8を接続し、制御手段19がスイッチ5〜8の操作に応じた第一の端子17と第二の端子18からの電圧を減算して、操作されたスイッチを検出することによって、接続された電子機器30が異なる抵抗値の抵抗31や32が設けられた機器に取替えられた場合でも、制御手段19がどのスイッチが操作されたかを、値が一定のダイオードの電圧降下によって検出しているため、誤検出がなく、確実な操作が可能な入力装置を得ることができる。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路を提供する。

【解決手段】ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるように制御を行なう。ハイサイドスイッチング素子5のゲート・ソース間にNchノーマリーオン型補助スイッチング素子13のドレイン・ソースを接続し、トランス15の1次側をゲート駆動回路1の出力に接続し、2次側をNchノーマリーオン型スイッチング素子13のゲート・ソース間に接続し、ローサイドスイッチング素子6側もトランス及びNchノーマリーオン型スイッチング素子をハイサイドと同様に接続して電力変換回路を構成する。

(もっと読む)

誘導性負荷駆動装置

【課題】電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現可能な誘導性負荷駆動装置を提供する。

【解決手段】第1のスイッチング素子と、第2のスイッチング素子と、還流回路と、逆起電流回生回路と、第2のスイッチング素子とアースとの間に介挿されたシャント抵抗とを備えた誘導性負荷駆動回路から誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、シャント抵抗の両端に接続された差動増幅器と、第1及び第2のスイッチング素子を制御するプロセッサと差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、プロセッサから第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチをオンにさせる遅延回路とを備える。

(もっと読む)

半導体装置

【課題】簡単な回路構成により誤動作を防止できる半導体装置を得る。

【解決手段】パワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。駆動回路1は、電源に接続された高圧端子と、低圧端子とを有する。抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。スイッチング素子Q3は入力信号INに応じてオン・オフする。入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。入力信号INがオフ信号の場合に、スイッチング素子Q3はオンする。

(もっと読む)

半導体装置

【課題】スタンバイ状態時にSRAMにデータを保持できる電圧が与えられている場合に、パワーオンリセットがかからないようにすることができる半導体装置を提供する。

【解決手段】CPU5は、スタンバイ状態に遷移することを通知する。電源制御回路11は、スタンバイ状態時に、SRAM4における電力消費を低減させる。POR回路2は、外部電源電圧の値と、現在の状態がスタンバイ状態であるかに応じて、パワーオンリセット信号の活性化を制御する。

(もっと読む)

バンドギャップ基準電圧回路及びこれを用いたパワーオンリセット回路

【課題】バンドギャップ基準電圧回路100を確実に起動させることができる。

【解決手段】電源電圧がpMOSトランジスタP1のゲート電圧の閾値に到達する前には、pMOSトランジスタP6により電源VddとpMOSトランジスタP4のソース端子との間を開放させている。このため、電源電圧がpMOSトランジスタP1のゲート電圧の閾値に到達する前に、抵抗素子R3aによってコンデンサC1から電荷を放出させて、コンデンサC1のプラス電極の電位をpMOSトランジスタP4のゲート端子の電位の閾値よりも低くすることができる。電源電圧が上昇してpMOSトランジスタP6が電源VddとpMOSトランジスタP4のソース端子との間を接続すると、pMOSトランジスタP4がオンして、電源VddからpMOSトランジスタP6、P4を通してスタートアップ電流をnMOSトランジスタN1、N2のゲート端子に流すことができる。

(もっと読む)

ゲートドライブ回路

【課題】オンデューティが50%以上のパルス信号でもスイッチング素子のゲートをドライブできる安価なゲートドライブ回路。

【解決手段】直流電源Vcc1の両端にトーテムポール接続され且つ各ベースにパルス信号が入力されるトランジスタQ2,Q3と、直流電源Vcc2の両端にトーテムポール接続され且つ各エミッタがスイッチング素子Q1のゲートに接続されるトランジスタQ4,Q5と、一次巻線P1がトランジスタQ2,Q3の各エミッタとトランジスタQ2,Q3の一方のコレクタとにコンデンサC1を介して接続され、二次巻線S1がトランジスタQ4,Q5の各ベースとトランジスタQ4,Q5の各エミッタとに接続されたトランスT1とを有し、パルス信号Vinの最大オンデューティは、トランスT1の一次巻線電圧VpとトランジスタQ4,Q5のベース−エミッタ間順方向電圧とに基づいて決定される。

(もっと読む)

半導体装置

【課題】ハーフブリッジ回路のメインスイッチング素子が同時オンになることを確実に防止する。

【解決手段】ローサイド側の入力信号を遅延させてローサイド側遅延信号として出力する遅延回路20と、ハイサイド側の入力信号からハイサイド側セット出力信号と予備リセット信号とを生成して出力するパルス発生回路12と、ローサイド側の入力信号がアクティブになってからローサイド側遅延信号がアクティブになるまでの期間、又は予備リセット信号がアクティブである期間にハイサイド側リセット出力信号をアクティブにするリセット信号生成回路30と、を備えるハーフブリッジドライバとする。

(もっと読む)

リセット回路

【課題】減電検出を利用して確実にリセットを掛ける。

【解決手段】整流電圧V+をレギュレータ24にてレギュレートした定電圧3.3Vを駆動電圧とされるマイコン30のリセット端子に接続される端子2と抵抗R1を介して定電圧3.3Vを入力される端子4とを備え、端子4の入力電圧が第1閾値を下回るとマイコン30にリセット信号を出力するリセットIC12と、抵抗R2を介して端子4にコレクタを接続され、エミッタをグランドに接続され、スイッチングトランス21の出力が所定レベルを下回るとオンするように構成されたトランジスタQ1と、を備え、トランジスタQ1がオンすると端子4に第1閾値を下回る電圧を入力する。

(もっと読む)

リセット回路

【課題】複数の電源電圧を駆動電圧とするSoC IC(System on a Chip Integrated Circuit)に対し、負荷変動やノイズに影響されること無く、複数の電源電圧の供給とリセット解除タイミングとのシーケンスを守ってリセットを行う。

【解決手段】供給ラインL1とリセット端子16との間においてエミッタを供給ラインL1に向けつつコレクタをリセット端子16に向けて介挿されたトランジスタTr1と、トランジスタTr1のベースとグランドとの間においてコレクタをトランジスタTr1のベースに向けつつエミッタをグランドに向けて介挿されたトランジスタTr2と、トランジスタTr1のコレクタとグランドとの間においてコレクタをトランジスタTr2のコレクタに向けつつエミッタをグランドに向けて介挿されたトランジスタTr3とを備える。

(もっと読む)

リセット回路およびシステム

【課題】 パワーオンまたはパワーダウンを検出するリセット回路を誤動作することなく動作させ、パワーオン時にリセット信号を正常に出力する。

【解決手段】 電源検出回路は、電源電圧が第1電圧を超えたときにパワーオン状態を示すパワーオン信号を活性化するとともに、初期化信号の活性化中に初期化される。スタータ回路は、電源電圧線と接地線の間に直列に配置された抵抗素子、遮断スイッチおよびキャパシタを有し、抵抗素子と遮断スイッチとを接続する第1接続ノードから初期化信号を出力する。遮断スイッチは、パワーオン信号の活性化中にオフする。このため、パワーオン状態中に、抵抗素子を介してキャパシタが充電されることを防止できる。この結果、キャパシタのTDDBの劣化を確実に防止でき、リセット回路を搭載する半導体装置およびシステムの誤動作を防止できる。

(もっと読む)

リセット回路

【課題】マイクロコンピュータとCPUを安全かつ確実にリセットして正常起動させる。

【解決手段】第1制御回路41は第2電圧が動作電圧に達したときにリセット信号が入力されていれば初期化後に起動し、レギュレータIC20は第1電圧をレギュレートして生成した第2電圧を第1制御回路41に供給し、第2制御回路42は第3電圧が動作電圧に達したときにリセット信号が入力されていれば初期化後に起動し、レギュレータIC30は、第3電圧をレギュレートして生成した第4電圧を第2制御回路42に供給する機器において、リセット回路100は、第1電圧が第5電圧を超えて150msが経過するまでリセット信号の出力を継続させ、第1電圧が第5電圧を超えてから150msが経過するとリセット信号の出力を停止する。(第1電圧≧第2電圧、第3電圧≧第4電圧、第1電圧>第3電圧、第5電圧>第2電圧)

(もっと読む)

電子回路

【課題】

内部電源電圧を遮断するパワーダウンモードへの移行を誤動作無く確実に実行するパワーダウンモードの移行シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧から降圧してシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する第1の内部回路30と、電源電圧を供給されて動作する入出力回路24と、第1の内部回路30からの信号を入力し、電源電圧の電圧レベルに変換するレベルシフタ23と、システム電圧発生回路10を制御する制御回路40とを備え、制御回路40は起動信号P4を入力し、この起動信号に所定の遅延時間を与えた短絡制御信号P5を出力する遅延回路100を有し、起動信号はレベルシフタ23を非活性又は活性として制御し、短絡制御信号はシステム電圧発生回路10を停止状態又は動作状態として制御する構成とした。

(もっと読む)

パルス信号出力回路およびシフトレジスタ

【課題】安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、出力端子と接続するノードを構成するトランジスタのチャネル長を、出力端子として機能するトランジスタのチャネル長よりも大きくする。これによって、該ノードからの電流のリークを抑制して、長期間にわたって安定して電位を保持することが可能となり、パルス信号出力回路の誤作動を防止することができる。

(もっと読む)

パルス信号出力回路およびシフトレジスタ

【課題】安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】第1の出力端子に接続されるトランジスタの一にはクロック信号を与え、第2の出力端子に接続されるトランジスタの一には電源電位を与える。これにより、第2の出力端子を構成するトランジスタの充放電による消費電力を抑制することが可能である。また、第2の出力端子には電源からの電位が供給されることになるため、十分な充電能力を確保することができる。

(もっと読む)

半導体集積回路およびそれを内蔵した高周波モジュール

【課題】RF送信出力信号の高調波成分を低減する。

【解決手段】半導体集積回路110のアンテナスイッチ100の送信スイッチ104は送信端子102と入出力端子101の間にS・D電流経路が接続されゲート端子Gが送信制御端子108に接続された送信電界効果トランジスタを含み、受信スイッチ105は入出力端子101と受信端子103の間にS・D電流経路が接続されゲート端子Gが受信制御端子109に接続された受信電界効果トランジスタを含む。送信と受信とのnチャネル型MOS電界効果トランジスタは、シリコンオンインシュレータ(SOI)構造で形成される。アンテナスイッチの高調波成分を低減する値に設定された電圧発生回路10の基板電圧は、SOI構造の支持シリコン基板に接続された端子108、109に供給される。

(もっと読む)

レベルシフト回路、および電力変換装置

【課題】電源電圧の変動の際に、半導体装置の製造ばらつきがあったとしても、容易に誤動作しない低電圧側回路から高電圧側回路に制御信号を伝達するレベルシフト回路を提供する。

【解決手段】レベルシフト回路において、高電圧側の電源電圧変動dV/dtが回路のロジックレベルに影響を与える程度に発生した時において、この変動はセット側にもリセット側にも起こることを利用し、時定数生成回路、もしくは電源電圧変動が先に起こる個所からの信号によって、第1、第2の論理回路において、誤動作の信号が通過するのをマスクして防止する。このマスクするタイミングに充分、余裕をとることにより、半導体プロセスにおける製造ばらつきが個々の素子にあったとしても、高電圧側の電源電圧変動dV/dtが発生時の誤信号がフリップフロップに伝わるのを防止でき、誤動作しない低電圧側回路から高電圧側回路に制御信号を伝達する。

(もっと読む)

パワーオンリセット回路

【課題】誤動作を起こす可能性があった。

【解決手段】電源投入初期もしくは電源電圧降下時にリセット信号を発生し初期化するパワーオンリセット回路であって、電源電圧に応じた電圧を分圧した第1の比較電圧を生成する第1の比較電圧生成部と、電源電圧に応じた第1の電圧を出力する基準電圧生成部と、電源電圧端子と第1のノードとの間に接続され、制御端子に前記第1の電圧を入力するデプレッション型の第1のトランジスタと、前記第1のノードと接地端子との間に接続され、制御端子が前記第1のノードに接続されるエンハンスメント型の第2のトランジスタと、を備え、前記第1のノードの電位に応じた電圧を第2の比較電圧として生成する第2の比較電圧生成部と、前記第1、第2の比較電圧との比較結果に応じてリセット信号を出力する比較器と、を有するパワーオンリセット回路。

(もっと読む)

1 - 20 / 87

[ Back to top ]