Fターム[5J055AX37]の内容

Fターム[5J055AX37]の下位に属するFターム

フェイルセーフ構成 (60)

Fターム[5J055AX37]に分類される特許

1 - 20 / 158

故障検知機能付デジタル出力回路

電子機器装置

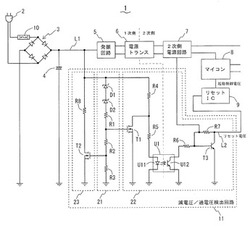

【課題】電子機器装置において、減電圧状態になった場合及び過電圧状態になった場合に、より確実に回路を保護する。

【解決手段】電子機器装置1は、第1の規定電圧値以下の電圧が電子機器装置1に供給される減電圧状態になった場合に、マイコン8をリセットさせ、第2の規定電圧値以上の電圧が電子機器装置1に供給される過電圧状態になった場合に、ヒューズ10を溶断させる減電圧/過電圧検出回路11を備える。減電圧/過電圧検出回路11は、平滑用のコンデンサ4により平滑化された電圧(1次側電圧出力ラインL1から出力された電圧)を監視し、平滑用のコンデンサ4により平滑化された電圧に基いて、減電圧状態、及び過電圧状態を検出する。そして、減電圧/過電圧検出回路11は、過電圧状態を検出した場合には、マイコン8をリセットさせ、過電圧状態を検出した場合には、ヒューズ10を溶断させる。

(もっと読む)

半導体装置

【課題】フォトカプラの一次側に流れる電流を制限するため抵抗を回路基板上に実装することなく、フォトカプラの一次側に流れる電流を制限できるようにする。

【解決手段】制御IC11a〜11cには、フォトカプラ21a〜21cの一次側に流れる電流を制限する抵抗17a〜17cをそれぞれ内蔵し、トランジスタ16a〜16cがそれぞれ導通した時に流れる電流を抵抗17a〜17cをそれぞれ介して発光素子22a〜22cに導くことにより、フォトカプラ21a〜21cの一次側に流れる電流を制限する。

(もっと読む)

自動補正機能付き周期タイマ

【課題】 衛星搭載コンポーネントのうち、衛星内部に配信される基準タイミングに同期して周期動作を行うようなコンポーネントでは、オシレータが有するクロック精度誤差のため、周期タイミングにずれが生じることがあり、これを回避する自動補正機能付き周期タイマを得る。

【解決手段】 基準タイミングの間隔を内部クロックによりカウントし、カウント値に従ってコンポーネントの周期タイミングを生成する。ユーザは予め周期タイミングの設定を「基準タイミングに対する分割数」として2の冪乗の値で与えて与えておき、基準タイミングの間隔のカウント値を分割数に従いビットシフトすることで周期タイマのカウント値を算出し、周期タイミングを生成する。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

半導体装置

【課題】周辺の回路構成を複雑にすることなく、繰り返しのデータの書き込みの際の劣化を低減することが可能な、不揮発性スイッチとして用いる半導体装置を提供する。

【解決手段】電源電圧が停止しても導通状態に関するデータの保持を、チャネル形成領域に酸化物半導体層を有する薄膜トランジスタに接続されたデータ保持部で行う構成とする。そしてデータ保持部は、ダーリントン接続された電界効果トランジスタ及びバイポーラトランジスタを有する電流増幅回路における、電界効果トランジスタのゲートに接続することでデータ保持部の電荷をリークすることなく、導通状態を制御する。

(もっと読む)

負荷駆動装置

【課題】クランプ回路が未使用状態なのか断線状態なのかを判別する。

【解決手段】温度センサ1hの出力が入力される温度検出端子14a〜14cを利用し、クランプ回路5a〜5cや温度検出回路7a〜7cの一部がパワーモジュール1に接続されないときには温度検出端子14a〜14cの電位に基づいて温度センサ1hが接続されていない断線無効状態を検出する。例えば、温度検出端子14a〜14cのうち温度センサ1hに接続されない端子に断線検出無効化閾値Vth3以上の電圧を印加することで、温度検出端子14a〜14cが温度センサ1hに接続されていないことを検出する。これにより、クランプ回路5a〜5cに接続されるクランプ端子11a〜11cの電位に基づいて断線検出を行う際に、断線状態なのか断線無効状態なのかを温度検出端子14a〜14cの電位に応じて判定できる。

(もっと読む)

電子デバイス、およびオーディオデバイスを制御する複数の受動スイッチを有するオーディオアクセサリ

【課題】電子デバイスと、オーディオデバイスを制御するための複数の受動Spスイッチを有するオーディオアクセサリとを提供すること。

【解決手段】電子デバイスを制御するように適合されているシステムであって、システムは、電子デバイスに結合されているオーディオアクセサリを含み、オーディオアクセサリは、複数の抵抗型スイッチを有し、電子デバイスは、バイアス抵抗器とグラウンド接続とを介して抵抗型スイッチに電力を提供するように適合されているバイアス電圧供給源と、測定モジュールとを含み、測定モジュールは、バイアス電圧供給源と抵抗型スイッチとの間の接続上のバイアスポイントを監視することと、オーディオ出力によって引き起こされるグラウンドオフセット電圧を決定することと、グラウンドオフセット電圧を補償することと、スイッチのどれが係合しているかを決定することとを行うように適合されている。

(もっと読む)

電力用半導体素子の駆動保護回路

【課題】電力用半導体素子の制御電極の短絡動作時の電圧を通常動作時の電圧と同じ値に制限し、安全で確実な遮断を行うことが可能な電力用半導体素子の駆動保護回路の提供を目的とする。

【解決手段】本発明の電力用半導体素子の駆動保護回路は、電力用半導体素子F1と、その制御電極を駆動する駆動回路と、電力用半導体素子F1の制御電極の電圧Vgeが一定値を超えないよう制限する電圧保護回路とを備える。電圧保護回路は、電力用半導体素子F1の制御電極にエミッタが接続されたゲート放電用トランジスタTr1と、ゲート放電用トランジスタTr1にベース電位を与える電圧発生回路B1とを備え、電圧発生回路B1は、電力用半導体素子F1の駆動正電源電圧VDDから、前記駆動回路における電圧降下ΔV1を超える電圧が電力用半導体素子F1の制御電極に印加されたときに、ゲート放電用トランジスタTr1がオンできる電圧を出力する。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

電気負荷駆動装置

【課題】電気負荷に電流を流す複数の各トランジスタが設けられている並列な通電用配線の断線を、各トランジスタに大きな電流負担をかけることなく、また電気負荷への通電を中断してしまうことなく検出する。

【解決手段】トランジスタTr1,Tr2によりリレーのコイル13aに通電する装置11では、コイル13aへの通電期間中に、電圧変動制御部31が、トランジスタTr1,Tr2へのゲート電圧VG1,VG2の両方を定期的に所定時間だけ低下させることにより、両トランジスタTr1,Tr2の通電能力が落ちてドレイン・ソース間電圧が所定値以上になる検査用期間を発生させ、該検査用期間中に、故障判定部32が、各トランジスタTr1,Tr2のドレイン・ソース間電圧を監視し、ドレイン・ソース間電圧が判定値未満のトランジスタがあれば、該トランジスタが設けられている通電用配線の反負荷側部分(LD1又はLD2)が断線していると判定する。

(もっと読む)

電気負荷駆動装置

【課題】電気負荷に電流を流す複数の各トランジスタが設けられている並列な通電用配線の断線を、各トランジスタに大きな電流負担をかけることなく、また電気負荷への通電を中断してしまうことなく検出する。

【解決手段】2つのトランジスタTr1,Tr2によりリレーのコイル13aに通電するECU11では、コイル13aへの通電期間中に、電圧変動制御部31が、トランジスタTr1,Tr2へのゲート電圧VG1,VG2の各々を定期的に且つ互いに時間をずらして所定時間だけ低下させることにより、一方のトランジスタの通電能力が落ちてドレイン・ソース間電圧が所定値以上になる期間を発生させる。そして、故障判定部32は、各トランジスタのソース電圧VS1,VS2の差が所定の閾値以上になったことを検知すると、トランジスタTr1,Tr2が設けられている通電用配線L1,L2の負荷側部分LS1,LS2の何れかが断線していると判断する。

(もっと読む)

半導体装置

【課題】大きな外付け容量素子による時定数に依存することなく遅延時間を設定でき、ユーザが実装システム上でリセット解除に代表されるパルス変化の遅延時間を容易に変更する事ができ、電源瞬停時にリセット解除に代表されるパルス変化までの遅延時間が短くなる虞を抑制する。

【解決手段】発振回路(3)の発振動作で生成されるパルス信号をカウントし、カウント値が所定値に達したところでリセット解除に代表されるパルス変化のタイミングを生成する技術において、半導体装置の外部端(P1)子に接続される抵抗素子(R8)の抵抗値によって発振回路の発振周波数を可変にする。外付け抵抗素子によってリセット解除に代表されるパルス変化のタイミングを可変に設定することができ、それは、大きな外付け容量素子を用いる時定数に依存する遅延時間を必要とせず、故に、電源瞬停時にリセット解除に代表されるパルス変化までの遅延時間は短くならない。

(もっと読む)

ゲート駆動回路

【課題】MOSFETで発生するホットキャリア量を抑制して高信頼性のゲート駆動回路を提供する。

【解決手段】NOEMI回路を有するゲート駆動回路10において、ゲートチャージアップ用の回路12を構成するpチャネルMOSFET(QP1)とゲートディスチャージ用の回路13を構成するnチャネルMOSFET(QN1)に同型NOEMI回路14,15を直列接続することで、QP1,QN1で発生するホットキャリア量を抑制することができる。

(もっと読む)

出力回路及び出力装置

【課題】出力端子をシンク型又はソース型に切換える場合に、基板を交換する必要がなく、また出力端子に誤って電源を接続してもスイッチング素子の破損を防止することができる出力回路及び該出力回路を備える出力装置を提供する。

【解決手段】ディップスイッチ81にてソース型出力対応モードを選択した場合に、第2スイッチング素子32を常時オンにし、第1スイッチング素子31のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。ディップスイッチ81にてシンク型出力対応モードを選択した場合に、第1スイッチング素子31を常時オンにし、第2スイッチング素子32のオン/オフ制御によって、外部機器への出力をオン/オフ制御する。またソース型出力対応モードを選択した状態で、第2出力端子32に誤って外部電源を接続した場合、第2スイッチング素子32に大電流が流れるが、直ちにヒューズ35が切断される。

(もっと読む)

保護回路

【課題】

本発明は、FET1の劣化ないし破壊を防止するための保護回路を提供することを目的とする。

【解決手段】

主スイッチ2をONすると+電源3および−電源4に電圧が供給されコンデンサC3およびC4により+電源と−電源は徐々に立ち上がる。この時電子スイッチ21はOFFに設定されている。−電源4が規定値まで立ち上がると電子スイッチ21はONとなりFET1のドレインに+電源3が印加される。主スイッチ2をOFFとすると+電源3と−電源4はコンデンサC3およびC4により徐々に電圧は下がり始める。−電源が下がり始めると電子スイッチ21はOFFとなりFET1のドレイン電圧7はOFFとなる。

(もっと読む)

電源検知回路

【課題】電源検知回路において、BT劣化によって比較回路のミスマッチが増大することに起因する電源検知信号の精度の劣化を抑制する。

【解決手段】検知用比較回路104は、入力切替信号生成回路112によって、その出力の活性状態と非活性状態との切替時付近では、入力信号102と基準電圧103とを入力して、その両者の比較を行う。一方、前記切替時付近以外では、比較回路非使用時入力電圧110が検知用比較回路104に入力されて、その差動入力が同電位に固定される。従って、BT劣化による電源検知精度の経年劣化が有効に抑制される。

(もっと読む)

長期間タイマー

【課題】 低価格で誤差が少ない長期間タイマーを提供する。

【解決手段】 一次電池10を所定時間高放電させる高放電回路20と、一次電池10を長期間連続して低放電させる低放電回路30と、高放電回路20による放電が終了した後に一次電池の初期出力電圧を検出する電圧検出部40と、一次電池の出力電圧が前記初期出力電圧に基づいて設定された基準電圧以下になったことを検知して報知する手段とを備えることを特徴。

(もっと読む)

電力増幅器の過電流検出回路及びその方法

【課題】 しきい値を的確に可変して過電流検出の誤作動を防止する。

【解決手段】 過電流検出回路6Bは、Q2のエミッタと出力端子Oの間の電流検出抵抗R11の両端間に抵抗R21、R31が接続されている。R31の両端が過電流検出トランジスタQ5のベース−エミッタ間に接続されており、出力端子Oと−VB の間にダイオードD21、抵抗R61が接続されており、D21のカソードがQ5のエミッタと接続されている。R21とR31の接続点とグランド間には抵抗R51とD11が接続されており、R51とD11の接続点とQ2のエミッタの間にコンデンサC21が接続されている。R51、D11、C21のしきい値可変回路9Aは出力電圧の大きさが大きくなるとしきい値を大きくし、出力電圧の大きさが小さくなるとしきい値を小さくするが、C21とD11により、出力電圧の大きさが増加するときはしきい値を早く増大変化させ、減少するときはしきい値をゆっくり減少変化させる。

(もっと読む)

容量性負荷駆動回路

【課題】容量性負荷の静電容量と回路抵抗値とから決定される回路時定数が変化することによって生じる容量性負荷の充電速度または放電速度の変化を防止し、所望の駆動波形を得ることが可能な容量性負荷駆動回路を提供する。

【解決手段】容量性負荷駆動回路は、容量性負荷である複数の駆動素子と、複数のコンデンサーと、前記複数のコンデンサーに電力を供給する電源と、前記複数のコンデンサーと前記複数の駆動素子間の接続を切替える切替え手段と、前記切替え手段を制御する制御手段と、を有し、前記制御手段は、前記複数の駆動素子に対して印加される電荷容量の予測値に基づいて、前記切替え手段の接続状態を維持することを特徴とする。

(もっと読む)

1 - 20 / 158

[ Back to top ]