Fターム[5J055BX31]の内容

電子的スイッチ (55,123) | スイッチの種類、機能 (3,337) | 時限スイッチ、タイマ (69) | デジタル型タイマ (16)

Fターム[5J055BX31]の下位に属するFターム

複数のレジスタ、カウンタを使用するもの (6)

メモリ、レジスタの値を更新するもの (3)

分周比が変化するもの (1)

発振周波数が変化するもの

商用電源をカウントするもの

Fターム[5J055BX31]に分類される特許

1 - 6 / 6

半導体装置

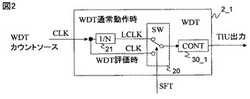

【課題】プログラムの変更を行わずに、ウォッチドッグタイマの動作を検証する。また、ウォッチドッグタイマのタイムアウトを外部で確認する。

【解決手段】本発明の半導体装置(1)は、ウォッチドッグタイマ(2)と中央処理装置(3)とモード端子(4)とを有する。前記中央処理装置は、前記ウォッチドッグタイマのタイムアウト制御を制御する。前記ウォッチドッグタイマは、前記モード端子を介して、前記ウォッチドッグタイマのタイマ周期を前記中央処理装置のタイムアウト制御による周期よりも短くする指示を外部から与えられる。前記ウォッチドッグタイマは、前記指示に応答して、前記中央処理装置によるタイムアウト制御よりも先に、タイムアウトを検出する。

(もっと読む)

家電用制御回路

【課題】点検時期を定刻以内に報知させ得る家電用制御回路を提供する。

【解決手段】家電用制御回路100は、電池12の電力を伝達させるバッテリラインLaと、電池12から供給された電力によって駆動され且つ電池12による電力の供給開始時点から起算して電力供給の経過時間を計数する時間カウント回路11とを備え、バッテリラインLaは、時間カウント回路11と、電池12の電圧値を検出するAD変換回路A/Dとに接続されることとする。これにより、マイコンCOMでは、電池12の電圧値が認識され、当該電池の消耗状態の判定を行うことが可能となる。

(もっと読む)

タイマ回路及び警報装置

【課題】 電源電圧に応じて発振周波数が変動する発振部を用いながらも正確な計時が可能なタイマ回路及び該タイマ回路を用いた警報装置を提供する。

【解決手段】 制御部14は、発振回路14aがパルスを単位カウント数だけ出力する毎に単位時間の経過を判定する。また、制御部14は、電源である一次電池BTの出力電圧を検出する電圧検出部15の出力に基づいて電圧補正係数を得るとともに、温度検出部16の出力に基づいて温度補正係数を得、得られた各係数をそれぞれ所定の基準状態での単位カウント数である基準カウント数に乗じることにより、新たな単位カウント数を得る。この単位カウント数の変更は、一次電池BTの出力電圧の変動や温度の変動による発振周波数の変動による単位時間への影響を相殺するものであって、新たな単位カウント数を用いて得られた単位時間は、発振周波数の変動に関わらず略一定となる。

(もっと読む)

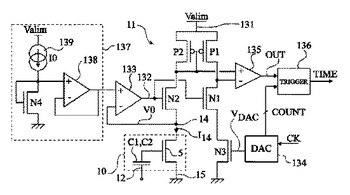

時間測定のための電荷保持要素を読み取る回路

【解決手段】本発明は、その誘電体がリークを示す少なくとも1つの容量性素子(C1,C2) と、残留電荷を読み取るための絶縁された制御ターミナル(5) を含むトランジスタとを備えたタイプの時間測定のための電荷保持電子要素(10)を読み取るための方法及び回路に関し、前記読み取り回路は、第1タイプの少なくとも1つのトランジスタ(P1,P2) と、第2タイプの1つのトランジスタ(N3,5)とを夫々含む、2つの供給ターミナル間の2つの平行な分岐を備えており、前記分岐の一方の第2タイプのトランジスタは、読み取られるべき前記要素のトランジスタから構成されており、前記分岐の他方の第2タイプのトランジスタは、該トランジスタの制御ターミナルでステップ信号(VDAC)を受けており、第1タイプのトランジスタの夫々のドレインは、比較器(135) の夫々の入力に接続されており、比較器の出力(OUT) が、電荷保持要素における残留電圧の表示を与える。  (もっと読む)

(もっと読む)

非同期デジタル回路用スリープ・ウォッチドッグ回路

本発明の非同期回路用スリープウォッチドッグ回路は、クロック手段、多数のトリガ入力機能有するカウント手段、およびデジタル供給手段を備える。回路が通常モードにある場合は、周期的なリセットまたはウォッチドッグカウンタをリセットするアクティビティ信号が存在する。その結果、クロック手段が動作し続け、デジタル供給手段が“通常”モードで駆動する。回路が“スリープ/スタンバイ”状態に入った場合は、“アクティビティ”信号が非アクティブとなり、カウンタが終了する前にウェイクアップイベントが発生しなかった場合は、クロック手段が停止され、デジタル供給手段が低電力モードへと変化する。  (もっと読む)

(もっと読む)

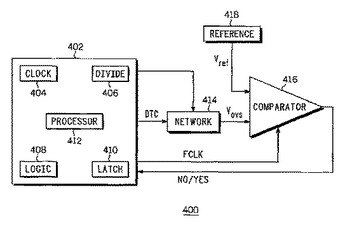

デジタル時定数トラッキング技術及び装置

プロセス、電圧及び温度の変動に起因して回路網(414)の時定数偏差を調整して雑音を無くす方法及び装置を提供する。当該装置(400)は、デジタル時定数が回路網(414)の公称時定数に対して相関されるクロック基準手段(404)を備える。相関されたデジタル時定数は、回路網(414)に印加され、そして出力充電/放電波形スイングが、所定の基準電圧と比較される。当該充電/放電波形スイングが基準電圧と一致しない場合、オフセット信号を発生する。オフセット信号が、制御回路(402)に印加され、当該制御回路(402)は、対応の同調信号を発生する。同調信号は、回路網(414)に印加されて、一致が達成されるまで内部部品を増分的又は減分的に調整する。当該装置(400)は、内蔵型で自己試験型のデジタル時定数トラッキング回路として構成されることでき、且つICチップ上に回路網(414)と一緒に統合化されることができる。  (もっと読む)

(もっと読む)

1 - 6 / 6

[ Back to top ]