Fターム[5J055EY10]の内容

Fターム[5J055EY10]の下位に属するFターム

可変容量 (14)

Fターム[5J055EY10]に分類される特許

1 - 20 / 1,236

負荷駆動装置

故障検知機能付デジタル出力回路

発振回路、およびDC−DCコンバータ

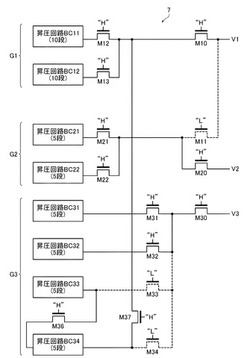

電圧生成回路

【課題】回路面積を低減させることのできる電圧生成回路を提供する。

【解決手段】一の実施の形態に係る電圧生成回路は、第1の電圧値の第1電圧を発生させる第1の昇圧回路と、第2の電圧値の第2電圧を発生させる複数の第2の昇圧回路を含む第2昇圧回路群とを有する。複数の第2の昇圧回路は、第1の状態から第2の状態に移行する際に互いに直列に接続され第1昇圧回路とともに第1電圧を発生可能に構成されている。

(もっと読む)

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子に接続されている逆相信号処理回路と、アノードが接続されている端子に接続されている第1及び第2の電圧制御電流源回路を備える。第1の電圧制御電流源回路には、正相信号Vinpに対応する電圧及び逆相信号Vinnの逆相に対応する電圧が入力され、第2の電圧制御電流源回路には、逆相信号Vinnに対応する電圧及び正相信号Vinpの逆相に対応する電圧が入力される。

(もっと読む)

昇降圧回路、スイッチ回路

【課題】駆動用のMOSトランジスタのオン抵抗が小さく、リーク電流の発生を防ぎ、しかも小型化、低消費電力化に適した昇降圧回路を提供する。

【解決手段】入力電圧IN2が入力される入力端子104、入力電圧IN2に基づいてVCCまたはGNDを出力するMOSトランジスタ201、203、入力電圧IN2に基づいて2VCCまたはGNDを出力するMOSトランジスタ202、204、MOSトランジスタ201、202に一端が接続され、他端がMOSトランジスタ202、204に接続される容量素子206、ソース・ドレイン端子の一方に2VCCが供給され、ソース・ドレイン端子の他方にVCCが供給され、2VCCまたはGNDがゲート端子に供給され、2VCCまたはGNDによってオン、オフされるMOSトランジスタ205と、によって昇圧回路を構成する。

(もっと読む)

スイッチング素子の駆動回路

【課題】固定が容易で且つ設置スペースを削減できるようにしたスイッチング素子の駆動回路を提供する。

【解決手段】多層配線板8の下面が主電流経路6上に搭載する搭載面とされているため、その多層配線板8の搭載面を平坦面にすることができる。したがって、主電流配線6は、その上面が平坦な設置面として形成されていれば、単に多層配線板8の搭載面を主電流配線6の上面に配置することで設置できる。これにより、コイルLを容易に固定でき設置スペースを削減できる。

(もっと読む)

エレベーターかご内照明装置およびエレベーターかご内照明方法

【課題】エレベーターが停止してから自動消灯するまでの時間を短くして省エネルギー効果を高めることができるエレベーターかご内照明装置を得る。

【解決手段】交流電源1からの交流電流を整流する全波ブリッジ整流回路21と、全波ブリッジ整流回路21の出力端子間に接続される電解コンデンサ23と、全波ブリッジ整流回路21から直流電流が供給されかご内を照明するLED3と、LED3に供給される直流電流が流れる回路を開閉するMOSFET41と、MOSFET41のオンオフを制御するドライバIC42と、エレベーターが所定の時間連続して停止していることを検出する自動消灯制御リレー51と備え、ドライバIC42は、自動消灯制御リレー51の検出結果に基づいてMOSFET41をオフにしてLED3への直流電流の供給を停止させる。

(もっと読む)

高周波スイッチ

【課題】通過損失を低減するためにオン状態時の抵抗を小さくしても、十分なアイソレーション量を確保する高周波スイッチを得る。

【解決手段】トランジスタ5a,5bのオフ容量Coffと同一の容量Ccを有するクロスカップルキャパシタ8a,8bを設ける。

クロスカップルキャパシタ8a,8bにより、トランジスタ5a,5bのオフ容量Coffをキャンセルすることができるので、アイソレーションを大きく改善することができる。したがって、通過損失を低減するためにトランジスタ5a,5bのオン抵抗Ronを小さくしても、十分なアイソレーション量を確保することができる。

(もっと読む)

駆動信号出力回路

【課題】負荷、電源などの動作条件が変化しても、電磁妨害等を引き起こす周波数帯域の成分が除去された駆動信号を出力する。

【解決手段】負荷5に与えられる駆動信号をハイパスフィルタまたはバンドパスフィルタからなる検出用フィルタ17を介して検出し、その検出駆動信号をバンドギャップ回路18に入力する。バンドギャップ回路18は、固有の周波数特性を有し、検出駆動信号に固有の周波数帯域内の周波数成分が含まれていると出力電圧が低下する特性を持つ。制御回路28は、バンドギャップ回路18の出力電圧を基準電圧と比較し、検出駆動信号に固有の周波数帯域内の信号成分が含まれるか否かを判定する。含まれる場合には、ローパスフィルタ13により駆動信号から当該周波数帯域内の信号成分を除去する。

(もっと読む)

制御装置

【課題】電源ユニットの出力ラインにおける地絡などの故障に対し、電源の保護及び故障の検知を行う。

【解決手段】サブ電源供給ラインLSに、サブ電源101側をソースとして第1MOSFET102を直列に接続し、第1MOSFET102のドレインにドレインを接続させて第2MOSFET103を直列に接続する。制御ユニット200内のサブ電源供給ラインLSにも、サブ電源101側をソースとして第3MOSFET202を直列に接続し、第3MOSFET202のドレインにドレインを接続させて第4MOSFET203を直列に接続し、第1〜第4MOSFETを制御することで、サブ電源101の電力を負荷201に対して供給する。各MOSFETのドレイン電圧、及び、第2MOSFET103と第3MOSFET202との間の電圧をモニタし、MOSFETの故障及びサブ電源供給ラインLSの故障を診断する。

(もっと読む)

電源切換装置

【課題】電圧変動の少ない電源切り換えを確実に行うことができる電源切換装置を提供する。

【解決手段】第2電源が接続される第2電源接続部、第2電源の電圧よりも高い電圧の第1電源が接続される第1電源接続部、負荷回路が接続される電源出力部、定電圧回路の出力端子と電源出力部とを接続するダイオード、第1電源接続部とダイオードとの間に挿入され第1電源の電圧を第2電源の電圧よりもダイオードの順方向電圧降下分高い電圧まで降圧する定電圧回路、第2電源接続部と電源出力部との接続をオン/オフするMOSスイッチと、第1電源接続部から電源が供給され、第2電源接続部または電源出力部の電圧と定電圧回路の出力電圧とを比較し、定電圧回路の出力電圧が第2電源接続部または電源出力部の電圧よりも高いとき、第1電源の電圧をMOSスイッチに導通することによってMOSスイッチをオフする比較回路と、を備える。

(もっと読む)

スタック電圧耐性を高めるためのキャパシタンス調整

【課題】 印加されるRF電圧Vswに制御可能に耐えるRFスイッチ、又はこのようなスイッチの製造方法を提供する。

【解決手段】 スイッチは直列接続された構成FETのストリングを有し、このストリングのノードは隣接するFETの各対の間にある。方法は、各構成FETにわたって分布するRFスイッチ電圧の不一致を減らすよう、容量的にストリングを有効に調整すべくストリングの異なるノードの間のキャパシタンスを制御し、それによって、スイッチ・ブレイクダウン電圧を高める。キャパシタンスは、例えば、ストリングのノードの間に容量特性配置することによって、及び/又は異なる構成FETの設計パラメータを変化させることによって、制御される。各ノードについて、ノードに現れるVswの比率による各有意なキャパシタの積の和は、おおよそ零になるよう制御され得る。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路を提供する。

【解決手段】ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるように制御を行なう。ハイサイドスイッチング素子5のゲート・ソース間にNchノーマリーオン型補助スイッチング素子13のドレイン・ソースを接続し、トランス15の1次側をゲート駆動回路1の出力に接続し、2次側をNchノーマリーオン型スイッチング素子13のゲート・ソース間に接続し、ローサイドスイッチング素子6側もトランス及びNchノーマリーオン型スイッチング素子をハイサイドと同様に接続して電力変換回路を構成する。

(もっと読む)

スイッチ

【課題】高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することが可能なスイッチを提供する。

【解決手段】高周波信号が入力される入力端子と、高周波信号が出力される第1出力端子との間に接続され、入力される高周波信号を第1出力端子から選択的に出力させる第1スイッチング部と、入力端子と、入力された高周波信号が出力される第2出力端子との間に接続され、入力端子に入力される高周波信号を第2出力端子から選択的に出力させる第2スイッチング部とを備え、第1スイッチング部、第2スイッチング部それぞれは、信号線上に設けられるインピーダンス変成器と、エミッタが接地され、コレクタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタと、コレクタが接地され、エミッタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタとを備えるスイッチが提供される。

(もっと読む)

スイッチング電源装置

【課題】大型化することなく、アーム短絡および損失増大の問題を解消したスイッチング電源装置を構成する。

【解決手段】ローサイドスイッチング制御部81は、ローサイドスイッチング素子(Q1)へ駆動電圧信号を出力している期間にトランスの巻線電圧の極性反転を検出したときに、遅延時間(td1)の後にローサイドスイッチング素子(Q1)をターンオフさせるローサイドターンオフ回路を備え、ハイサイドスイッチング制御部61は、トランスの巻線電圧の極性が反転してからハイサイドスイッチング素子(Q2)をターンオンさせるまでの時間(td2)を遅延させる。そして、ローサイドターンオフ遅延回路の遅延時間(td1)はハイサイドターンオン遅延回路の遅延時間(td2)よりも短く設定されている。

(もっと読む)

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

駆動回路

【課題】駆動電圧を調整可能な駆動回路を提供すること。

【解決手段】駆動回路10は、チャージポンプ回路部14を備えている。チャージポンプ回路部14は、メインスイッチング素子SW10がターンオンする遷移期間の初期段階において、キャパシタC1に充電された充電電圧に基づいて駆動電源18の電圧Vsを昇圧して駆動電圧Vgprを生成する。チャージポンプ回路部14では、指示信号S1に基づいてキャパシタC1に充電される充電電圧が調整可能に構成されている。

(もっと読む)

誘導性負荷駆動装置

【課題】電流回生ルートから電流還流ルートへの切替時におけるホールドコンデンサの電荷抜けを抑制して電流検出精度の向上を実現可能な誘導性負荷駆動装置を提供する。

【解決手段】第1のスイッチング素子と、第2のスイッチング素子と、還流回路と、逆起電流回生回路と、第2のスイッチング素子とアースとの間に介挿されたシャント抵抗とを備えた誘導性負荷駆動回路から誘導性負荷に供給される駆動電流を検出する誘導性負荷駆動装置であって、シャント抵抗の両端に接続された差動増幅器と、第1及び第2のスイッチング素子を制御するプロセッサと差動増幅器の出力端子とを結ぶ配線に介挿されたサンプルスイッチと、プロセッサから第2のスイッチング素子に出力される制御信号がオンレベルに遷移してから所定の遅延時間の経過後にサンプルスイッチをオンにさせる遅延回路とを備える。

(もっと読む)

電界効果トランジスタのゲート電位制御回路

【課題】FETのゲートドライブ回路に正負の電源を必要とせず、簡単な受動素子のみの回路で、ゲート電位に正極/負極電位を印加しFETの高速スイッチングドライブを可能とする。

【解決手段】電流路が導通する電位を超える電位1を、電流路の一端を基準電位として、制御端に容量素子を介して断続的に印加されるべく構成され、電位1が印加されたとき、電位1が前記定電圧素子1に対して、電流路が導通に要す定電圧素子1の有する降伏電圧1を発生すべく、かつ電位1が定電圧素子2に対して順方向に、電位1が印加された後、電位1が低下されたとき、電位1により容量素子に充電された電位2が電流路の一端を基準電位とし定電圧素子2に対して、電位1と逆極性の、定電圧素子2の有する降伏電圧2を発生すべく、かつ電位2が定電圧素子1に対して順方向に、定電圧素子1と定電圧素子2の直列接続回路を、制御端と電流路の一端との間に介在させた。

(もっと読む)

1 - 20 / 1,236

[ Back to top ]