Fターム[5J055EZ05]の内容

Fターム[5J055EZ05]の下位に属するFターム

ボルテージホロア (10)

プッシュプル(INVを含む) (687)

差動型 (207)

Fターム[5J055EZ05]に分類される特許

1 - 20 / 56

発振回路、およびDC−DCコンバータ

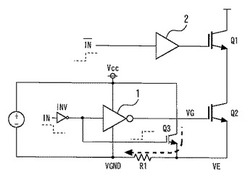

半導体装置

【課題】簡単な回路構成により誤動作を防止できる半導体装置を得る。

【解決手段】パワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。駆動回路1は、電源に接続された高圧端子と、低圧端子とを有する。抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。スイッチング素子Q3は入力信号INに応じてオン・オフする。入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。入力信号INがオフ信号の場合に、スイッチング素子Q3はオンする。

(もっと読む)

電力変換回路、多相ボルテージレギュレータ、及び電力変換方法

【課題】電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制する。

【解決手段】本発明による電力変換回路は、相互に直列接続されハーフブリッジ回路を構成するハイサイドトランジスタ11及びローサイドトランジスタ12と、ハイサイドトランジスタ11及びローサイドトランジスタ12のゲートを相補に駆動する2つの駆動回路21、22とを具備する。ハイサイドトランジスタ11はノーマリオフ型トランジスタであり、ローサイドトランジスタ12は、ノーマリオン型トランジスタである。

(もっと読む)

通信システム

【課題】通信線に現れるリンギング現象を効果的に抑制することができる通信システムを得る。

【解決手段】NPNバイポーラトランジスタT11のエミッタは抵抗R11の一端に接続されるとともに接地レベルに接続され、コレクタは抵抗R12の一端及びコンデンサC12の一方電極に接続され、ベースは抵抗R11の他端及びコンデンサC11の一方電極に接続される。コンデンサC11の他方電極はLライン通信線10Lに接続される。PNPバイポーラトランジスタT12のエミッタは電源電圧V11を受け、コレクタはNMOSトランジスタQ11のゲートに接続される。NMOSトランジスタQ11のドレインはHライン通信線10Hに接続され、ソースがLライン通信線10Lに接続され、ゲートは抵抗R14を介して接地される。

(もっと読む)

電子デバイス、およびオーディオデバイスを制御する複数の受動スイッチを有するオーディオアクセサリ

【課題】電子デバイスと、オーディオデバイスを制御するための複数の受動Spスイッチを有するオーディオアクセサリとを提供すること。

【解決手段】電子デバイスを制御するように適合されているシステムであって、システムは、電子デバイスに結合されているオーディオアクセサリを含み、オーディオアクセサリは、複数の抵抗型スイッチを有し、電子デバイスは、バイアス抵抗器とグラウンド接続とを介して抵抗型スイッチに電力を提供するように適合されているバイアス電圧供給源と、測定モジュールとを含み、測定モジュールは、バイアス電圧供給源と抵抗型スイッチとの間の接続上のバイアスポイントを監視することと、オーディオ出力によって引き起こされるグラウンドオフセット電圧を決定することと、グラウンドオフセット電圧を補償することと、スイッチのどれが係合しているかを決定することとを行うように適合されている。

(もっと読む)

ゲート駆動回路及び半導体装置

【課題】応答性を損なうことなく能動クランプ素子の損失電力を低減できる能動クランプ回路を用いたゲート駆動回路及び半導体装置を提供する。

【解決手段】スイッチ素子Tr7のゲートを駆動するゲート駆動回路であって、制御信号に基づいてスイッチ素子Tr7を駆動する駆動部(トランジスタTr1,Tr2,Tr4,Tr5)と、スイッチ素子Tr7の第1主端子(ドレイン)と第2主端子(ソース)との間に印加される電圧が所定電圧以上の場合に、駆動部によるスイッチ素子Tr7に対する駆動動作を強制的に遮断して、スイッチ素子Tr7の第1主端子と第2主端子との間の電圧がクランプされるようにスイッチ素子Tr7を駆動するアクティブクランプ回路(ダイオードD1、ツェナーダイオードZD1、抵抗R1、トランジスタTr3,Tr6)とを備える。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力期間の切替時における出力信号の遅延発生を抑制する出力回路、データドライバと表示装置の提供。

【解決手段】出力回路は差動増幅回路110、105,出力増幅回路120と第1の制御回路160、入力端子101、出力端子104、第1乃至第3の電源端子VDD、VSS、VMLを備える。差動増幅回路は前記入力端子の入力信号と前記出力端子の出力信号を入力する差動入力段110と第1及び第2のカレントミラー130、140を備える。出力増幅回路120は第1の電源端子VDDと出力端子104との間に接続された第1導電型の第1のトランジスタ121と出力端子104と第3の電源端子VMLとの間に接続された第2導電型の第2のトランジスタ122とを備える。第1の制御回路160は、第1導電型の第3のトランジスタ161と第1のスイッチ162を備える。

(もっと読む)

故障または異常検出機能を有するパルス増幅装置およびパルス増幅器故障検出方法

【課題】小型化が可能な故障または異常検出機能を有するパルス増幅装置を提供すること。

【解決手段】本実施形態に係る故障または異常検出機能を有するパルス増幅装置は、入力されるパルスを増幅して出力するパルス増幅器11と、パルス増幅器11の入力端子に接続され、パルス増幅器11に入力されるパルスに同期したパルス増幅器11を動作させる制御信号を形成して、この制御信号を入力端子に入力するパルス増幅器制御回路12と、パルス増幅器制御回路12に接続され、制御信号を連続波に変換する平均化回路17と、平均化回路17に接続され、平均化回路17から出力された連続波の電圧Vgaveとしきい値電圧Vsとを比較する比較回路18と、比較回路18に接続され、比較回路18から出力される差分電圧(Vgave−Vs)に基づいて、パルス増幅器11の故障、あるいはパルス増幅器制御回路12の異常を検出する警報装置23と、を具備する。

(もっと読む)

プログラマブルロジックデバイス集積回路上の高速シリアルデータレシーバ用のデシリアライザ回路網

【課題】多数の異なるプロトコルに対して、および広範囲のデーターレートに対して、シリアル形式のデータをパラレル形式のデータに変換することが可能な、デシリアライザ回路網を提供する。

【解決手段】プログラマブルロジックデバイス(「PLD」)などの高速シリアルデータレシーバ回路網用のデシリアライザ回路網(10)は、シリアルデータを任意の複数のデータ幅を有するパラレルデータに変換するための回路網を含む。該回路網(10)はまた、広範囲の周波数の中の任意の周波数で動作可能である。該回路網(10)は様々な観点において構成可能/再構成可能であり、その構成/再構成の少なくとも1部分はダイナミックに(すなわち、PLDのユーザーモードオペレ−ションの間に)制御され得る。

(もっと読む)

スイッチ回路、半導体装置及び携帯無線機

【課題】負バイアス発生回路を用いずにマージン電圧を改善することができる手段をスイッチ回路に提供する。

【解決手段】N型MOSFETを用いて構成されるスイッチM1を、信号をアンテナに同通するスイッチに、P型MOSFETを用いて構成されるスイッチM2を、信号を接地するシャント用にそれぞれ用いる。各スイッチを構成するMOSFETのゲート端子に共通の制御信号を入力する。この制御信号の反転信号をスイッチM2の接地端に接続することで、各MOSFETのゲート端子の電位を接地電圧に設定できる。

(もっと読む)

表示パネルドライバ及びそれを用いた表示装置

【課題】駆動電圧の極性切替(極性反転)が可能な表示パネルドライバの消費電力を低減する表示パネルドライバを提供する。

【解決手段】本発明による表示パネルドライバは、表示パネルの画素に接続された第1データ線及び第2データ線を駆動する出力段として、第1電源範囲で駆動する第1出力段24A及び第4出力段24Bを利用する第1モードと、第1電源範囲よりも広い第2電源範囲で駆動する第2出力段73A及び第3出力段73Bを利用する第2モードとを切替える第1スイッチ回路50と、第2モードの間に、正極性駆動電圧と負極性駆動電圧の出力先となるデータ線6を切替える第2スイッチ回路30とを備える。又、第1出力段24Aは、ウェルが他のNMOSトランジスタから分離され、バックゲートがソースに接続された第1プルダウン出力トランジスタMN18を備える。

(もっと読む)

半導体素子の駆動装置及び方法

【課題】半導体素子のスイッチング時において、スイッチング損失の増加を抑制しつつ、サージ電圧を低減すること。

【解決手段】di/dt帰還部23は、IGBT11Uがターンオフするときに、IGBT11のコレクタ電流Icの時間変化に基づいて、帰還電圧VFBを生成する。また、di/dt帰還部23は、IGBT11がターンオンするときに、図示せぬFWDの転流電流IFWDに基づいて、帰還電圧VFBを生成する。このようなdi/dt帰還部23は、帰還電圧VFBを駆動信号の電圧の一部として印加するタイミングを遅延させる遅延フィルタとして、LPF回路201を備えている。LPF201の遅延量、即ちインダクタンスLdを適度に調整することで、還流ダイオードの電圧におけるサージ電圧を低減させることができる。

(もっと読む)

信号発生器の保護回路

【課題】出力信号経路に過電流が流れた場合でも信号出力回路の破壊または劣化を防ぎ、信号出力回路を保護することが可能な信号発生器の保護回路を実現する。

【解決手段】クロック信号またはデジタル信号である信号出力回路からの出力信号をリレーを介して出力する信号発生器の保護回路において、電源と信号出力回路の電源端子の間に接続された電流検出用抵抗と、電流検出用抵抗の両端電圧を増幅して出力する増幅器と、増幅器からの電圧が予め定められた閾値を超えた場合に検出信号を出力する電圧検出判定回路と、電圧検出判定回路からの検出信号に応じてリレーを切断し、出力信号の経路を断つリレー制御回路とを備える。

(もっと読む)

アナログ入力装置

【課題】信号トランスの励磁エネルギーを速やかに消費させ、入力信号のバックスイングおよび各チャンネルの読み込み時間を短縮して、高速化可能なアナログ入力装置を得る。

【解決手段】外部から入力されたアナログ信号を絶縁する信号トランス23と、信号トランス23の1次側に接続され、オンオフ制御されることでアナログ信号をパルス形状に変化させる第1スイッチ素子21と、信号トランス23の1次側に、信号トランス23の巻線端子と並列に接続され、互いに直列に接続された抵抗素子31および第2スイッチ素子32からなるリセット回路22と、第1スイッチ素子21に対して、オンオフ制御のための第1制御パルス信号を出力するとともに、第1制御パルス信号を出力した後に、第2スイッチ素子32に対して、信号トランス23の巻線に励磁されたエネルギーを消費するための第2制御パルス信号を出力する第1、第2シーケンス手段41、42とを備える。

(もっと読む)

送受信モジュール

【課題】大きなパルス幅を有する大電力の高周波信号が入力された場合であっても、リミタ回路および受信回路の増幅器が破壊されることを抑制することができる送受信モジュールを提供する。

【解決手段】アンテナ11と、リミタ回路16および受信系電力増幅器17を備えた受信回路14と、送信系電力増幅器20を備えた送信回路15とが、送受信切替スイッチ13により接続され、アンテナ11と送受信切替スイッチ13の間に設けられた検波回路12により、送受信切替スイッチ13を制御する制御信号を生成する。送受信切替スイッチ13は、制御信号が入力されない状態ではアンテナ11と受信回路14とを導通させ、制御信号が入力されるとアンテナ11と送信回路15とを導通させる。制御信号は、送受信切替スイッチ13に信号が入力された時から、リミタ回路16の熱時定数よりも短い時間までの間に送受信切替スイッチ13に入力される。

(もっと読む)

電子回路

【課題】増幅回路の雑音指数の劣化を抑制すること。

【解決手段】送信端子Txから入力された送信信号を前記共通端子ANTに接続する送信スイッチSW1と、前記共通端子から入力された受信信号を増幅し、受信端子Rxに出力する増幅回路90と、前記共通端子から他のスイッチを介さず入力された前記受信信号を前記増幅回路に接続する第1受信スイッチSW2と、前記共通端子と前記受信端子との間で前記第1受信スイッチとは並列に接続され、前記共通端子から入力された前記受信信号を前記増幅回路とは別の経路で前記受信端子に接続する第2受信スイッチSW3と、を具備する電子回路。

(もっと読む)

高耐圧スイッチ回路およびそれを用いた半導体集積回路装置

【課題】 双方向スイッチにおいて、ドレイン電圧またはドレイン-ソース間電圧に基づいて、上記スイッチのゲート-ソース間電圧を制御する手段と、上記制御手段を介して、上記スイッチのゲート端子に電圧を印加するスイッチドライバとを備えている双方向スイッチを提供する。

【解決手段】 双方向スイッチであるメインスイッチと、上記メインスイッチのゲート-ソース間電圧を、上記メインスイッチのドレイン電圧、ソース電圧に基づいて制御する手段と、上記制御手段を介して上記メインスイッチのゲート端子に電圧を印加するスイッチドライバとを備えている双方向スイッチを構成する。

(もっと読む)

半導体装置、及びその制御方法

【課題】発振回路と信号入出力回路とを切り替えて使用可能な半導体装置、及びその制御方法を提供することである。

【解決手段】本発明にかかる半導体装置は、発振素子1が接続可能な第1及び第2の外部接続端子2、3と、反転増幅器4と、反転増幅器の出力側と入力側との間に接続されたフィードバック抵抗5と、反転増幅器4の入力側に接続されたカップリング容量11に印加されるバイアスを安定化するバイアス安定化回路6と、第1の信号入出力部7と、第2の信号入出力部8と、を備える。半導体装置を発振回路として使用する場合は、反転増幅器4およびバイアス安定化回路6を動作状態とし、第1及び第2の信号入出力部7、8を停止状態とする。信号入出力回路として使用する場合は、反転増幅器4およびバイアス安定化回路6を停止状態とし、第1及び第2の信号入出力部7、8を動作状態とする。

(もっと読む)

半導体装置、高周波回路、および高周波電力増幅装置

【課題】マルチバンド又はマルチモードに適した半導体装置、高周波回路を提供する。

【解決手段】半導体基板301上に電界効果型トランジスタを形成してなる半導体装置であって、電界効果型トランジスタのソース電極およびドレイン電極としてのオーミック電極501a、501bと、前記オーミック電極501a、501bに挟まれた位置に設けられた、前記電界効果型トランジスタのゲート電極としてのショットキー電極601a、601cと、ショットキー電極601a、601cに挟まれた位置に設けられたショットキー電極601bとを備え、ショットキー電極601bが接地されている。

(もっと読む)

アンテナスイッチ回路及び通信端末

【課題】許容電力と挿入損出との特性を両立させるとともに、アンテナスイッチ回路の小型化を可能とし、且つスイッチング状態の更なる安定化を図ることができるようにする。

【解決手段】本発明によるアンテナスイッチ回路は、送信ポートとアンテナポートとの間に直列に接続された直列トランジスタ回路と、前記送信ポートと前記アンテナポートとの間に並列に接続された並列トランジスタ回路と、前記送信ポートと前記並列トランジスタ回路との間に設けられ、インピーダンス変換を行うことによって、前記送信ポートから入力された送信信号の電圧振幅を所定の変換比率で縮小するインピーダンス変換回路とを備え、前記インピーダンス変換回路は、前記並列トランジスタ回路に出力される端子間電圧が当該並列トランジスタ回路の閾値以下となるように前記所定の変換比率が設定されていることを特徴とする。

(もっと読む)

1 - 20 / 56

[ Back to top ]