Fターム[5J055FX05]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 帰還を行うもの (2,113) | 電気信号に変えられる現象、物理量 (2,102) | 電圧値 (1,457)

Fターム[5J055FX05]に分類される特許

1 - 20 / 1,457

故障検知機能付デジタル出力回路

発振回路、およびDC−DCコンバータ

負荷駆動装置

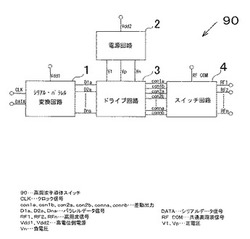

高周波半導体スイッチ、端末装置

【課題】スイッチ回路の誤動作の発生を防止する。

【解決手段】一つの実施形態によれば、シリアル・パラレル変換回路は、第一の高電位側電源が供給され、シリアルデータ信号が入力され、パラレルデータ信号を生成する。電源回路は、第二の高電位側電源が供給され、第二の高電位側電源に基づいて第一の正電圧、第二の正電圧、及び負電圧を生成する。ドライブ回路は、第一の正電圧が電源として供給され、パラレルデータ信号が入力されるインバータと、第二の正電圧及び負電圧が電源として供給され、パラレルデータ信号及びインバータの出力信号が入力される差動型レベルシフタを含むレベルシフト回路が設けられ、第二の正電圧をハイレベルの信号としてスイッチ回路に出力し、負電圧をローレベルの信号としてスイッチ回路に出力する。

(もっと読む)

電圧生成回路

【課題】回路面積を低減させることのできる電圧生成回路を提供する。

【解決手段】一の実施の形態に係る電圧生成回路は、第1の電圧値の第1電圧を発生させる第1の昇圧回路と、第2の電圧値の第2電圧を発生させる複数の第2の昇圧回路を含む第2昇圧回路群とを有する。複数の第2の昇圧回路は、第1の状態から第2の状態に移行する際に互いに直列に接続され第1昇圧回路とともに第1電圧を発生可能に構成されている。

(もっと読む)

電源回路

【課題】 広帯域無線通信を行う送信機に用いられ、電源変換効率を向上させると共に、電圧レベル切替の遷移時間の影響を低減し、出力信号の歪特性を改善することができる電源回路を提供する。

【解決手段】 入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力するスイッチ制御部83′と、入力信号を特定の時間遅延させるタイミング制御部121を備え、スイッチ制御部83′が、制御信号の立ち上げの場合に、タイミング制御部121での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、立ち下げの場合には遅延時間のタイミングで立ち下げる電源回路としている。

(もっと読む)

パワー半導体素子の駆動回路

【課題】高速スイッチング性能を低下させることなく、パワー半導体素子のサージ耐量向上と過電圧保護を図る。

【解決手段】ドレイン端子1bから所定距離離間した位置にゲート制御端子5を備え、サージ発生時にドレイン端子1bとゲート制御端子5との間に放電が起こるようにする。この放電現象に伴ってゲート制御端子5にサージ電圧が印加されることで、パワー半導体素子1のゲートを充電し、パワー半導体素子1をオンさせることでサージエネルギーを吸収する。これにより、ドレイン端子1bに印加されるサージ電圧を抑制することが可能となり、パワー半導体素子1が破壊に至ることを抑制することが可能となる。

(もっと読む)

バッファ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路の入力電圧の振幅を増大させることが可能なバッファ回路を提供する。

【解決手段】第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、且つ、各入力端同士及び各出力端同士がそれぞれ共通に接続されており、第1,第2トランジスタ回路の少なくとも一方のトランジスタ回路がダブルゲートトランジスタから成るバッファ回路において、第1,第2トランジスタ回路の一方のトランジスタ回路が動作状態のとき、他方のトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

駆動信号出力回路

【課題】負荷、電源などの動作条件が変化しても、電磁妨害等を引き起こす周波数帯域の成分が除去された駆動信号を出力する。

【解決手段】負荷5に与えられる駆動信号をハイパスフィルタまたはバンドパスフィルタからなる検出用フィルタ17を介して検出し、その検出駆動信号をバンドギャップ回路18に入力する。バンドギャップ回路18は、固有の周波数特性を有し、検出駆動信号に固有の周波数帯域内の周波数成分が含まれていると出力電圧が低下する特性を持つ。制御回路28は、バンドギャップ回路18の出力電圧を基準電圧と比較し、検出駆動信号に固有の周波数帯域内の信号成分が含まれるか否かを判定する。含まれる場合には、ローパスフィルタ13により駆動信号から当該周波数帯域内の信号成分を除去する。

(もっと読む)

半導体集積回路

【課題】従来の半導体集積回路のレギュレータ回路では、出力電圧の制御精度を十分に高めることができない問題があった。

【解決手段】本発明の半導体集積回路は、制御端子に与えられるインピーダンス制御信号で示される制御値PLに応じて負荷電流Iloadの大きさに対する出力電圧VDDMの大きさを制御する複数の出力トランジスタPMと、出力電圧VDDMの電圧値を示す出力電圧モニタ値VMを出力する電圧モニタ回路12と、出力電圧VDDMの目標値を示す参照電圧Vrefと、出力電圧モニタ値VMと、の間の誤差値の大きさに応じて制御値PLの大きさを制御し、当該制御値PLにより複数の出力トランジスタPMいずれを導通状態とするかを制御する制御回路10と、を有し、制御回路10が負荷電流Iloadの変更を事前に通知する事前通知信号PACCに応じて、誤差値に対する制御値の変化ステップを一定期間の間大きくする。

(もっと読む)

制御装置

【課題】電源ユニットの出力ラインにおける地絡などの故障に対し、電源の保護及び故障の検知を行う。

【解決手段】サブ電源供給ラインLSに、サブ電源101側をソースとして第1MOSFET102を直列に接続し、第1MOSFET102のドレインにドレインを接続させて第2MOSFET103を直列に接続する。制御ユニット200内のサブ電源供給ラインLSにも、サブ電源101側をソースとして第3MOSFET202を直列に接続し、第3MOSFET202のドレインにドレインを接続させて第4MOSFET203を直列に接続し、第1〜第4MOSFETを制御することで、サブ電源101の電力を負荷201に対して供給する。各MOSFETのドレイン電圧、及び、第2MOSFET103と第3MOSFET202との間の電圧をモニタし、MOSFETの故障及びサブ電源供給ラインLSの故障を診断する。

(もっと読む)

電源切換装置

【課題】電圧変動の少ない電源切り換えを確実に行うことができる電源切換装置を提供する。

【解決手段】第2電源が接続される第2電源接続部、第2電源の電圧よりも高い電圧の第1電源が接続される第1電源接続部、負荷回路が接続される電源出力部、定電圧回路の出力端子と電源出力部とを接続するダイオード、第1電源接続部とダイオードとの間に挿入され第1電源の電圧を第2電源の電圧よりもダイオードの順方向電圧降下分高い電圧まで降圧する定電圧回路、第2電源接続部と電源出力部との接続をオン/オフするMOSスイッチと、第1電源接続部から電源が供給され、第2電源接続部または電源出力部の電圧と定電圧回路の出力電圧とを比較し、定電圧回路の出力電圧が第2電源接続部または電源出力部の電圧よりも高いとき、第1電源の電圧をMOSスイッチに導通することによってMOSスイッチをオフする比較回路と、を備える。

(もっと読む)

ゲート駆動回路、およびパワー半導体モジュール

【課題】スイッチング素子を誤動作させずに高速低損失動作が可能なゲート駆動回路を部品点数の少ない簡易な回路を提供する。

【解決手段】ローサイドゲート駆動回路2から正極性の電圧が出力されるとハイサイドゲート駆動回路1は0Vを維持または負極性の電圧を出力し、ローサイドゲート駆動回路2からの出力が0Vまたは負極性の電圧を出力する時はハイサイドゲート駆動回路1から正極性の電圧が出力されるように制御を行なう。ハイサイドスイッチング素子5のゲート・ソース間にNchノーマリーオン型補助スイッチング素子13のドレイン・ソースを接続し、トランス15の1次側をゲート駆動回路1の出力に接続し、2次側をNchノーマリーオン型スイッチング素子13のゲート・ソース間に接続し、ローサイドスイッチング素子6側もトランス及びNchノーマリーオン型スイッチング素子をハイサイドと同様に接続して電力変換回路を構成する。

(もっと読む)

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

スイッチング電源装置

【課題】大型化することなく、アーム短絡および損失増大の問題を解消したスイッチング電源装置を構成する。

【解決手段】ローサイドスイッチング制御部81は、ローサイドスイッチング素子(Q1)へ駆動電圧信号を出力している期間にトランスの巻線電圧の極性反転を検出したときに、遅延時間(td1)の後にローサイドスイッチング素子(Q1)をターンオフさせるローサイドターンオフ回路を備え、ハイサイドスイッチング制御部61は、トランスの巻線電圧の極性が反転してからハイサイドスイッチング素子(Q2)をターンオンさせるまでの時間(td2)を遅延させる。そして、ローサイドターンオフ遅延回路の遅延時間(td1)はハイサイドターンオン遅延回路の遅延時間(td2)よりも短く設定されている。

(もっと読む)

電圧スイッチ回路

【課題】低濃度ドープのPMOSトランジスタを用いて、高電圧ストレスに耐える電圧スイッチ回路を提供する。

【解決手段】該電圧スイッチ回路は、出力回路210、第1の電圧降下制御回路220、第2の電圧降下制御回路230、第3の電圧降下制御回路240、および入力回路250を備えている。また、高電圧源HVの電圧振幅は、基準電圧源Vrefの電圧振幅よりも高く、基準電圧源Vrefの電圧振幅は、論理電圧源VDDの電圧振幅よりも高い。

(もっと読む)

サンプルアンドホールド回路

【課題】ハイパスフィルタ回路を急速充電できるようにして、その起動時間を短くする。

【解決手段】所定のタイミング毎に入力信号を保持する信号保持回路11と、信号保持回路11の出力側に接続された第1のトランジスタQ1の出力側の第1のノードN1に現れる信号から低域成分を除去するハイパスフィルタ回路12と、起動時にのみ動作してハイパスフィルタ回路12のコンデンサC2に対して急速充電を行う急速充電回路14と、ハイパスフィルタ回路12の出力側に接続された増幅回路13と、急速充電回路14による急速充電動作の終了から通常動作に移行する前後で前記第1のノードN1のバイアス電位をほぼ一定に保持するバイアス制御回路15とを備える。

(もっと読む)

アナログマルチプレクサ

【課題】アナログデータ出力にクロック信号が混入しないアナログマルチプレクサを提供する。

【解決手段】アナログマルチプレクサは、2つのアナログデータ信号D1,D2の非反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第1のセレクタ4と、2つのアナログデータ信号D1,D2の反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第2のセレクタ5と、第1のセレクタ4の出力信号と第2のセレクタ5の出力信号との差信号を出力する減算回路6とを備える。

(もっと読む)

負荷制御装置

【課題】高デューティ領域においてデューティ比が不正確になるのを防止することにより、デューティ比の精度を向上させた負荷制御装置を提供する。

【解決手段】三角波生成回路5が、負荷2に供給される電源電圧VIから三角波VC1を生成する。パルス駆動回路6が、三角波生成回路5により生成される三角波VC1と基準電圧Vkとの比較に応じたデューティ比の駆動パルスを負荷2に供給する。基準電圧生成回路7が、電源電圧VIが増加するに従って基準電圧Vkを増加または減少させて駆動パルスのデューティ比を減少させる。周波数調整回路8が、電源電圧VIが所定電圧以下のときに、三角波生成回路5により生成される三角波VC1の周波数を低くして駆動パルスの周波数を低くする。

(もっと読む)

半導体素子のゲート駆動方法

【課題】ターンオフスイッチング時に発生するノイズとスイッチング損失のトレードオフ特性を改善する。

【解決手段】半導体素子をターンオフさせるとき、半導体素子のコレクタ・エミッタ間電圧がコレクタ・エミッタ間に印加された直流電圧に達するまでは、前記コレクタ・エミッタ間電圧の変化率を大きくし、半導体素子のコレクタ・エミッタ間電圧が直流電圧に達した後は、前記コレクタ・エミッタ間電圧の変化率を小さくする。

(もっと読む)

1 - 20 / 1,457

[ Back to top ]