Fターム[5J055FX11]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 信号を得る箇所 (1,721)

Fターム[5J055FX11]の下位に属するFターム

制御端子 (1,433)

主端子 (272)

帰還をかけるSW以外のSWから (5)

Fターム[5J055FX11]に分類される特許

1 - 11 / 11

負荷駆動装置

電圧検出回路

低電圧検出回路

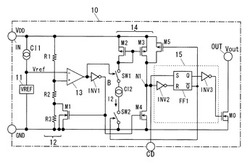

【課題】 電源電圧が所定の電位以上になって所定時間後に出力が解除状態になった後は定電流源の電流を流さないようにして消費電流を抑える遅延付き低電圧検出回路を実現する。

【解決手段】 電圧比較回路(13)により検出対象の電圧が所定の電圧値以下になったことを検出した場合には出力状態を直ちに変化させ、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には電流回路(14)により決まる遅延時間後に出力状態を変化させる低電圧検出回路において、電流回路は、電圧比較回路により検出対象の電圧が所定の電圧値以下になったことを検出した場合には、定電流源の電流を遮断する状態とし、電圧比較回路により検出対象の電圧が所定の電圧値以上になったことを検出した場合には、定電流源の電流を流す状態として電流回路によるコンデンサの充電を開始させ所定遅延時間後に定電流源に流れる電流を遮断するように構成した。

(もっと読む)

半導体装置

【課題】スタンバイ状態時にSRAMにデータを保持できる電圧が与えられている場合に、パワーオンリセットがかからないようにすることができる半導体装置を提供する。

【解決手段】CPU5は、スタンバイ状態に遷移することを通知する。電源制御回路11は、スタンバイ状態時に、SRAM4における電力消費を低減させる。POR回路2は、外部電源電圧の値と、現在の状態がスタンバイ状態であるかに応じて、パワーオンリセット信号の活性化を制御する。

(もっと読む)

駆動装置

【課題】低電圧駆動時の動作の信頼性を確保しながら動作速度を向上でき回路を保護できるようにする。

【解決手段】トランジスタQ7が動作するときには、当該トランジスタQ7による増幅回路がソース接地回路として動作する。MOSトランジスタQ7のゲート−ソース間にオン制御電圧が印加されたときには、当該トランジスタQ7のドレイン電位がソース電位に急速に近づき、急速にオン状態に遷移する。また、クランプ回路10がトランジスタQHのゲート−ソース間に設けられているため、当該ゲート−ソース間電圧が必要以上に上昇することがなくなる。この回路部分では、トランジスタQHの閾値電圧VT+トランジスタQ7のドレイン−ソース間電圧VDSのみで駆動できるため、低電圧駆動時でも動作の信頼性を確保できる。

(もっと読む)

駆動回路および表示装置

【課題】出力電圧の立ち上がるタイミングのばらつきを低減することの可能な駆動回路、およびこの駆動回路を備えた表示装置を提供する。

【解決手段】バッファ回路1は、互いに直列に接続されたインバータ回路10およびインバータ回路20を備えている。インバータ回路20は、3つのトランジスタTr21,Tr22,Tr23を有している。そのうちの2つのトランジスタTr21,Tr22は、デュアルゲート型のトランジスタである。これらトランジスタTr21,Tr22のバックゲートの電圧を調整することにより、トランジスタTr21,Tr22の閾値電圧を調整することができる。

(もっと読む)

高周波半導体スイッチ

【課題】トランジスタのドレインとバックゲート間およびソースとバックゲート間に生じる電流の漏洩を抑圧し、高周波信号の透過損失の増大を抑制できる高周波半導体スイッチを得る。

【解決手段】高周波半導体スイッチは、接地部を有するSi等の真性半導体基板と、この真性半導体基板に形成され、バックゲート端子を有するMOSトランジスタと、真性半導体基板の接地部およびMOSトランジスタのバックゲート端子間に設けられたインダクタとを備える。

(もっと読む)

半導体装置

【課題】電源回路等を追加することなく、第1の電源電圧が低下してもダイナミックVTによる高速化の効果の低減を抑制できる半導体装置を提供する。

【解決手段】第1の回路は、第1の電源電圧を供給する第1の電源ラインと第1の電源電圧よりも低い第2の電源電圧を供給する第2の電源ライン間に接続された、トランジスタを備える。制御回路は、第1の電源ラインと第2の電源ライン間に接続され、上記トランジスタのバックゲートに第1の電源電圧と第2の電源電圧の電位差よりも振幅が大きい制御信号を供給する。

(もっと読む)

DC−DCコンバータ

【課題】出力短絡保護機能を設ける場合に、短絡電流をバイパスするバイパス回路を外部に設けることなく、内部回路(内部素子)を保護できるDC−DCコンバータの提供。

【解決手段】この発明は、直流電圧を昇圧して出力電圧を生成し、当該出力電圧の生成のために入力端子1と出力端子2との間に複数のMOSトランジスタM1〜M4が直列接続されたDC−DCコンバータである。MOSトランジスタM4は、自己の基板電位制御用のMOSトランジスタM41、M42を有する。DC−DCコンバータの定常動作時にはMOSトランジスタM42がオンし、MOSトランジスタM4の基板端子に出力端子2の電位が印加される。一方、DC−DCコンバータの出力短絡時にはMOSトランジスタM41がオンし、MOSトランジスタM4の基板端子に出力端子2とは反対側の電位が印加される。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の制御方法

【課題】入力信号に必要な振幅を低減する。

【解決手段】電源線L1と出力部N2との間のトランジスタTA1のゲートG1は容量素子C1を介して入力部N1に結合する。電源線L2と出力部N2との間のトランジスタTA2のゲートG2は容量素子C2を介して入力部N1に結合する。トランジスタTB3は、電源線L1からみてゲートG1の方向を順方向として電源線L1とゲートG1との間にダイオード接続される。トランジスタTB4は、ゲートG1からみて電源線L1の方向を順方向として電源線L1とゲートG1との間にダイオード接続される。トランジスタTB3の閾値電圧VT3がトランジスタTA1の閾値電圧VT1を上回り、かつ、トランジスタTB3の閾値電圧VT3とトランジスタTB4の閾値電圧VT4との加算が減少するように、トランジスタTB3およびトランジスタTB4の各々のバックゲートBの電位VBが設定される。

(もっと読む)

電源スイッチ回路

【課題】LSIチップ上で分離された複数の機能ブロック毎の電源に電圧差が発生しても、電源間をつなぐスイッチのオフ状態において電流を確実に遮断することが出来る電源スイッチ回路を提供する。

【解決手段】1aは、コントロール信号端子INCNT及び第1の電源入力端子IG11及び第2の電源入力端子IG12とを入力とし、第1の出力端子OG11及び第2の出力端子OG12とを出力とするゲート制御回路である。P1は、ゲート制御回路の第1の出力端子OG11がゲートに接続された第1のP型トランジスタであり、P2は、ゲート制御回路の第2の出力端子OG12がゲートに接続された第2のP型トランジスタであり、第1のP型トランジスタP1及び第2のP型トランジスタP2は、第1の電源VDD1と第2の電源VDD2間に直列に接続されスイッチ部分を構成する。

(もっと読む)

1 - 11 / 11

[ Back to top ]