Fターム[5J055FX17]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 制御、帰還信号の特徴 (2,064) | 制御、帰還信号はデジタル値であるもの (1,286)

Fターム[5J055FX17]の下位に属するFターム

2値(Yes、NO)であるもの (795)

Fターム[5J055FX17]に分類される特許

1 - 20 / 491

故障検知機能付デジタル出力回路

電圧検出回路

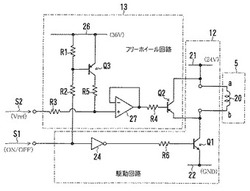

電磁機器駆動装置および電磁機器の駆動方法

【課題】電磁機器の累積使用量が多くなっても少ないと同じ一定時間で電磁機器を動作状態から停止状態に移行させる。

【解決手段】電磁機器駆動装置は、励磁用電源から電磁コイルへの通電が停止したときに逆起電力によって電磁コイルの両端間に生じる電圧をクランプするフリーホイール回路と、フリーホイール回路によってクランプされた電圧が、電磁機器の累積使用量が少ないときよりも多いときの方が高くなるように、フリーホイール回路の動作を制御するコントローラーと、を備える。

(もっと読む)

ドライバ及びその使用方法

【課題】 簡易な構成で、急激な電流変化を回避してノイズの発生や不要輻射の放出を抑えると共に、ユーザの使用態様の多様性に柔軟に対応できるようにする。

【解決手段】 デューティ比を変えることをもってして、パルスの立ち上がりのタイミングをずらす、すなわち、ドライバトランジスタのオンするタイミングをずらす。また、いくつかの出力端子を束ねる構成とする場合には、それらの出力端子に対応する各ドライバトランジスタについては、デューティ比を同じとすることをもってして、各ドライバトランジスタを同時オンさせて個々のオーバーロードを回避する。言い換えれば、出力端子を束ねない限りにおいては、デューティ比を変えてパルスの立ち上がりのタイミングをずらすことが得策となる。

(もっと読む)

スイッチング電源装置

【課題】大型化することなく、アーム短絡および損失増大の問題を解消したスイッチング電源装置を構成する。

【解決手段】ローサイドスイッチング制御部81は、ローサイドスイッチング素子(Q1)へ駆動電圧信号を出力している期間にトランスの巻線電圧の極性反転を検出したときに、遅延時間(td1)の後にローサイドスイッチング素子(Q1)をターンオフさせるローサイドターンオフ回路を備え、ハイサイドスイッチング制御部61は、トランスの巻線電圧の極性が反転してからハイサイドスイッチング素子(Q2)をターンオンさせるまでの時間(td2)を遅延させる。そして、ローサイドターンオフ遅延回路の遅延時間(td1)はハイサイドターンオン遅延回路の遅延時間(td2)よりも短く設定されている。

(もっと読む)

スイッチ

【課題】高周波信号の振幅に対する歪みを低減しつつ、スイッチングを実現することが可能なスイッチを提供する。

【解決手段】高周波信号が入力される入力端子と、高周波信号が出力される第1出力端子との間に接続され、入力される高周波信号を第1出力端子から選択的に出力させる第1スイッチング部と、入力端子と、入力された高周波信号が出力される第2出力端子との間に接続され、入力端子に入力される高周波信号を第2出力端子から選択的に出力させる第2スイッチング部とを備え、第1スイッチング部、第2スイッチング部それぞれは、信号線上に設けられるインピーダンス変成器と、エミッタが接地され、コレクタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタと、コレクタが接地され、エミッタが信号線に接続され、制御電圧に応じた電流がベースに印加されるバイポーラトランジスタとを備えるスイッチが提供される。

(もっと読む)

出力ドライバー回路

【課題】nMOSトランジスタM2のゲート−ソース間に加わる電圧を耐圧電圧未満に制限する際に消費電流の増加を抑制する。

【解決手段】pMOSトランジスタM1がオフし、かつnMOSトランジスタM2がオンしたとき、ツェナーダイオードZD2により、nMOSトランジスタM2のゲート端子とソース端子との間の電圧を一定電圧に制限する。nMOSトランジスタM2のゲート端子とソース端子との間に耐圧電圧よりも高い電圧が加わることを避けることが可能になる。このとき、定電流電源20bが電源からツェナーダイオードZD2を通してグランドに流れる電流を制限する。電源からトランジスタM3、M5b、M6bを通してnMOSトランジスタM2のゲート端子に流れる電流をnMOSトランジスタM6bが制限する。

(もっと読む)

アナログマルチプレクサ

【課題】アナログデータ出力にクロック信号が混入しないアナログマルチプレクサを提供する。

【解決手段】アナログマルチプレクサは、2つのアナログデータ信号D1,D2の非反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第1のセレクタ4と、2つのアナログデータ信号D1,D2の反転信号を入力とし、クロック信号CLKに応じて2つのアナログデータ信号D1,D2のうち何れか一方を選択的に出力する第2のセレクタ5と、第1のセレクタ4の出力信号と第2のセレクタ5の出力信号との差信号を出力する減算回路6とを備える。

(もっと読む)

半導体素子のゲート駆動方法

【課題】ターンオフスイッチング時に発生するノイズとスイッチング損失のトレードオフ特性を改善する。

【解決手段】半導体素子をターンオフさせるとき、半導体素子のコレクタ・エミッタ間電圧がコレクタ・エミッタ間に印加された直流電圧に達するまでは、前記コレクタ・エミッタ間電圧の変化率を大きくし、半導体素子のコレクタ・エミッタ間電圧が直流電圧に達した後は、前記コレクタ・エミッタ間電圧の変化率を小さくする。

(もっと読む)

半導体装置

【課題】PVT変動に応じて動作駆動力を変更することが可能な、プリエンファシス動作をサポートするデータ出力回路を備える半導体装置を提供する。

【解決手段】インピーダンスコードPCODE<0:2>,NCODE<0:2>の変動に応じて値が調節されるプリエンファシスコードEM_PCODE<0:1>,EM_NCODE<0:1>を生成するコード生成部360と、出力データP_DATA,N_DATAを受信してデータ出力パッドDQに駆動し、インピーダンスコードに応じて駆動力が調節されるメイン駆動部311〜313,321〜323と、出力データを受信してデータ出力パッドに駆動し、プリエンファシスコードに応じて駆動力が調節される補助駆動部314〜315,324〜325とを備える。

(もっと読む)

スイッチ素子駆動回路

【課題】グランド端子からグランド電位の供給を受けることなく、スイッチ素子をオン状態に維持することを可能とするスイッチ素子駆動回路を提供する。

【解決手段】本発明によるスイッチ素子駆動回路(100)は、電源と負荷との間に接続されたスイッチ素子を駆動するためのスイッチ素子駆動回路であって、前記電源と前記負荷との間に設けられた電圧降下素子(10)と、前記電圧降下素子の端子間に発生する電圧を動作電源として該電圧を昇圧し、該昇圧により得られた電圧から前記スイッチ素子を制御するための制御信号を生成する信号生成部(20)とを備える。

(もっと読む)

電力変換回路、多相ボルテージレギュレータ、及び電力変換方法

【課題】電力変換回路において、ノーマリオン型トランジスタを利用したスイッチング素子への貫通電流を抑制する。

【解決手段】本発明による電力変換回路は、相互に直列接続されハーフブリッジ回路を構成するハイサイドトランジスタ11及びローサイドトランジスタ12と、ハイサイドトランジスタ11及びローサイドトランジスタ12のゲートを相補に駆動する2つの駆動回路21、22とを具備する。ハイサイドトランジスタ11はノーマリオフ型トランジスタであり、ローサイドトランジスタ12は、ノーマリオン型トランジスタである。

(もっと読む)

過電流保護回路

【課題】過電流検出抵抗の温度特性の影響をキャンセルすることのできる過電流保護回路を提供する。

【解決手段】基準抵抗と第1定電流源との第1接続点には、該第1接続点の電位の温度特性が、過電流検出抵抗の電圧検出端子の電位の温度特性と等しくなるように、第1接続点に対して正の温度特性を有する第2定電流を供給する第2定電流源が接続されている。第2定電流源は、負の温度特性を有する第3定電流を供給する第3定電流源と、温度特性を有さない第4定電流を供給する第4定電流源と、第3定電流源に対して直列接続された第1トランジスタと、第4定電流源に対して直列接続された第2トランジスタと、により構成された第1カレントミラー回路と、第4定電流源と第2トランジスタとの接続点に接続され、第1接続点に第2定電流を供給するための電流経路と、を有する。第3定電流源は、過電流検出抵抗と同じ基板に形成されている。

(もっと読む)

半導体モジュール

【課題】半導体スイッチを小さい負担で駆動できるとともに、半導体スイッチに十分なゲート電流を流すことができ、しかも、ゲート配線のインピーダンスによる障害を回避できる半導体モジュール。

【解決手段】ゲートに印加される電圧に応じてオンオフする半導体スイッチQ1と、半導体スイッチのソース電位に対して正極性を有する正極コンデンサ110と、半導体スイッチのソース電位に対して負極性を有する負極コンデンサ111と、正極コンデンサを充電する機能を有し、半導体スイッチをターンオンさせる場合は正極コンデンサからの電流を半導体スイッチのゲートに流すターンオン制御部112と、負極コンデンサを充電する機能を有し、半導体スイッチをターンオフさせる場合は負極コンデンサからの電流を半導体スイッチのゲートに流すターンオフ制御部113を備える。

(もっと読む)

パルス信号出力回路およびシフトレジスタ

【課題】安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供する。

【解決手段】酸化物半導体を用いたトランジスタを複数用いて、パルス信号出力回路を構成する。また、パルス信号出力回路の動作に応じて、酸化物半導体を用いたトランジスタのしきい値電圧を変動させる。また、該パルス信号出力回路を含むシフトレジスタを構成する。これにより、安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

正負電圧論理出力回路およびこれを用いた高周波スイッチ回路

【課題】負電圧の変化に対して正常な論理回路動作を確保できる範囲である動作ウィンドウの幅の拡張を可能とし、回路動作の確実性、安定性の向上を図った正負電圧論理出力回路を提供する。

【解決手段】論理入力と負電圧との間に、ゲートに論理入力するエンハンスメント型P型電界効果トランジスタEPFET1とブレークダウン保護用素子13,14とが直列に接続され、ブレークダウン保護用素子14に並列に短絡する切替スイッチ8aが接続される。切替スイッチ8aをオン、オフ制御することで、VSSの変動に対して正常な回路動作を確保できる動作ウィンドウの拡張を可能とする。

(もっと読む)

半導体装置

【課題】パワーデバイスの誤動作を防ぐ。

【解決手段】直列に接続された2つのパワーデバイスのうち高電位側のパワーデバイスを駆動制御する半導体装置であって、高電位側のパワーデバイスの導通を示す第1状態及び高電位側のパワーデバイスの非導通を示す第2状態を有する入力信号の第1,第2状態へのレベル遷移に対応して、それぞれ第1,第2のパルス信号を発生させるパルス発生回路と、第1,第2のパルス信号を高電位側へレベルシフトして、それぞれ第1,第2のレベルシフト済みパルス信号を得るレベルシフト回路と、第1,第2のレベルシフト済みパルス信号を少なくとも第1,第2のパルス信号のパルス幅分遅延させて、それぞれ第1,第2の遅延済みパルス信号を得る遅延回路と、第1の遅延済みパルス信号をセット入力から入力し、第2の遅延済みパルス信号をリセット入力から入力するSR型フリップフロップとを備える。

(もっと読む)

接点入力回路

【課題】閾値電圧設定回路の抵抗器の開放故障に対するフェールセーフ性を確保し、且つ、検査信号がオフ制御されたときの消費電力を低減できる接点入力回路の実現。

【解決手段】接点入力回路10は、接点の開閉状態を示す入力信号が入力される正入力端子11と負入力端子12との間に、第1抵抗器R1、第3抵抗器R3及び第4抵抗器R4が直列接続されている。そして、直列接続された第3抵抗器R3及び第4抵抗器R4に対して、第2抵抗器R2、第1フォトカプラP1のフォトダイオードPd1及び第2フォトカプラP2のフォトトランジスタPt2が順方向に直列接続されてなる第2回路部16が並列接続されている。また、第4抵抗器R4に対して、第2フォトカプラP2のフォトダイオードPd2及び第3フォトカプラP3のフォトトランジスタPt3が順方向に直列接続されてなる第1回路部15が並列接続されている。

(もっと読む)

スイッチング素子の制御装置

【課題】実際に発生しているフライバックエネルギーを定量的に評価した上で保護動作を行うことができるスイッチング素子の制御装置を提供する。

【解決手段】NチャネルMOSFET2を介してコイル1に供給される電流をセンスMOSFET6及び検出用抵抗素子21により検出し、NチャネルMOSFET2をターンオフさせた際に発生し、ドレインに印加される逆起電圧をクランプ回路3によってクランプする。電流検出回路24は、クランプ回路3に発生するクランプ電圧によりNチャネルMOSFETがターンオンした際に、検出用抵抗素子21に流れる電流を複数の閾値と比較し、保護動作部26は、電流検出回路24の比較結果により、前記電流がNチャネルMOSFET2をターンオフさせた時点からの時間経過に対応する特定の閾値を超えていると判定されると、逆起電圧に基づくエネルギーを減少させるようにNチャネルMOSFET2の制御状態を変更する。

(もっと読む)

アナログスイッチ回路およびマルチプレクサ回路

【課題】 外部端子の雑音の影響を抑制しつつ、リーク電流を低減する。

【解決手段】 アナログスイッチ回路は、第1ノードと第2ノードとの間に配置された第1スイッチと、第2ノードと第3ノードとの間に配置された第2スイッチと、所定の電圧が供給される第4ノードと第2ノードとの間に配置された第3スイッチと、少なくとも2種類の制御信号を受け、第1スイッチおよび第2スイッチをオンし、かつ、第3スイッチをオフする第1制御と、第1スイッチ、第2スイッチおよび第3スイッチをオフする第2制御と、第1スイッチおよび第2スイッチをオフし、かつ、第3スイッチをオンする第3制御とのいずれかを、制御信号の組み合わせに基づいて実施する制御部とを有している。

(もっと読む)

1 - 20 / 491

[ Back to top ]