Fターム[5J055FX18]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 制御、帰還信号の特徴 (2,064) | 制御、帰還信号はデジタル値であるもの (1,286) | 2値(Yes、NO)であるもの (795)

Fターム[5J055FX18]に分類される特許

1 - 20 / 795

信号切替回路およびA/D変換装置

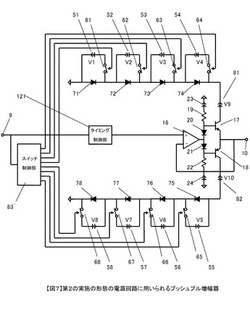

電源回路

【課題】 広帯域無線通信を行う送信機に用いられ、電源変換効率を向上させると共に、電圧レベル切替の遷移時間の影響を低減し、出力信号の歪特性を改善することができる電源回路を提供する。

【解決手段】 入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力するスイッチ制御部83′と、入力信号を特定の時間遅延させるタイミング制御部121を備え、スイッチ制御部83′が、制御信号の立ち上げの場合に、タイミング制御部121での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、立ち下げの場合には遅延時間のタイミングで立ち下げる電源回路としている。

(もっと読む)

電圧生成回路

【課題】回路面積を低減させることのできる電圧生成回路を提供する。

【解決手段】一の実施の形態に係る電圧生成回路は、第1の電圧値の第1電圧を発生させる第1の昇圧回路と、第2の電圧値の第2電圧を発生させる複数の第2の昇圧回路を含む第2昇圧回路群とを有する。複数の第2の昇圧回路は、第1の状態から第2の状態に移行する際に互いに直列に接続され第1昇圧回路とともに第1電圧を発生可能に構成されている。

(もっと読む)

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子に接続されている逆相信号処理回路と、アノードが接続されている端子に接続されている第1及び第2の電圧制御電流源回路を備える。第1の電圧制御電流源回路には、正相信号Vinpに対応する電圧及び逆相信号Vinnの逆相に対応する電圧が入力され、第2の電圧制御電流源回路には、逆相信号Vinnに対応する電圧及び正相信号Vinpの逆相に対応する電圧が入力される。

(もっと読む)

電源切換装置

【課題】電圧変動の少ない電源切り換えを確実に行うことができる電源切換装置を提供する。

【解決手段】第2電源が接続される第2電源接続部、第2電源の電圧よりも高い電圧の第1電源が接続される第1電源接続部、負荷回路が接続される電源出力部、定電圧回路の出力端子と電源出力部とを接続するダイオード、第1電源接続部とダイオードとの間に挿入され第1電源の電圧を第2電源の電圧よりもダイオードの順方向電圧降下分高い電圧まで降圧する定電圧回路、第2電源接続部と電源出力部との接続をオン/オフするMOSスイッチと、第1電源接続部から電源が供給され、第2電源接続部または電源出力部の電圧と定電圧回路の出力電圧とを比較し、定電圧回路の出力電圧が第2電源接続部または電源出力部の電圧よりも高いとき、第1電源の電圧をMOSスイッチに導通することによってMOSスイッチをオフする比較回路と、を備える。

(もっと読む)

制御装置

【課題】電源ユニットの出力ラインにおける地絡などの故障に対し、電源の保護及び故障の検知を行う。

【解決手段】サブ電源供給ラインLSに、サブ電源101側をソースとして第1MOSFET102を直列に接続し、第1MOSFET102のドレインにドレインを接続させて第2MOSFET103を直列に接続する。制御ユニット200内のサブ電源供給ラインLSにも、サブ電源101側をソースとして第3MOSFET202を直列に接続し、第3MOSFET202のドレインにドレインを接続させて第4MOSFET203を直列に接続し、第1〜第4MOSFETを制御することで、サブ電源101の電力を負荷201に対して供給する。各MOSFETのドレイン電圧、及び、第2MOSFET103と第3MOSFET202との間の電圧をモニタし、MOSFETの故障及びサブ電源供給ラインLSの故障を診断する。

(もっと読む)

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

電界効果トランジスタのゲート電位制御回路

【課題】FETのゲートドライブ回路に正負の電源を必要とせず、簡単な受動素子のみの回路で、ゲート電位に正極/負極電位を印加しFETの高速スイッチングドライブを可能とする。

【解決手段】電流路が導通する電位を超える電位1を、電流路の一端を基準電位として、制御端に容量素子を介して断続的に印加されるべく構成され、電位1が印加されたとき、電位1が前記定電圧素子1に対して、電流路が導通に要す定電圧素子1の有する降伏電圧1を発生すべく、かつ電位1が定電圧素子2に対して順方向に、電位1が印加された後、電位1が低下されたとき、電位1により容量素子に充電された電位2が電流路の一端を基準電位とし定電圧素子2に対して、電位1と逆極性の、定電圧素子2の有する降伏電圧2を発生すべく、かつ電位2が定電圧素子1に対して順方向に、定電圧素子1と定電圧素子2の直列接続回路を、制御端と電流路の一端との間に介在させた。

(もっと読む)

半導体集積回路

【課題】不具合の発生が抑制された半導体集積回路を提供する。

【解決手段】電圧レベルの高いHi信号、及び、該Hi信号よりも電圧レベルの低いLo信号が異なるタイミングで入力される第1入力端子と、Hi信号が常時入力される第2入力端子と、第1入力端子のHi信号によって第1動作状態、第1入力端子のLo信号によって第2動作状態に制御される素子と、を有する半導体集積回路であって、第2入力端子とグランドとの間にスイッチング素子が設けられており、該スイッチング素子は、第1入力端子にHi信号が入力されている時にOFF状態、第1入力端子にLo信号が入力されている時にON状態となる。

(もっと読む)

半導体装置

【課題】所定の動作の期間においてクロックを停止させ、消費電力を低減する半導体装置を提供すること。

【解決手段】発振器11からの第1クロックCLK_oriをN分周した第2クロックCLK_divを出力する分周回路120−1と、前記第1クロックと前記分周回路からの前記第2クロックとを選択し、選択したクロックを出力する選択回路120−2と、前記第1クロックまたは前記第2クロックをカウントするタイマ回路120−3と、前記タイマ回路のカウント結果をデコードし、第1結果を出力するデコーダ120−4と、前記デコーダからの前記第1結果に基づき、前記選択回路が前記第2クロックを選択するよう第1選択信号を出力するステートマシン120−9と、前記第1選択信号に基づき、前記ステートマシンの動作を停止する停止信号を出力する論理回路120−6とを具備する。

(もっと読む)

半導体装置

【課題】簡単な回路構成により誤動作を防止できる半導体装置を得る。

【解決手段】パワー素子Q1とパワー素子Q2がトーテムポール接続されている。駆動回路1が入力信号INに応じてパワー素子Q2を駆動し、駆動回路2が入力信号/INに応じてパワー素子Q1を駆動する。駆動回路1は、電源に接続された高圧端子と、低圧端子とを有する。抵抗R1の一端がパワー素子Q2のエミッタに接続され、抵抗R1の他端が駆動回路1の低圧端子に接続されている。スイッチング素子Q3が駆動回路1の高圧端子と抵抗R1の一端との間に接続されている。スイッチング素子Q3は入力信号INに応じてオン・オフする。入力信号INがオフ信号の場合に、駆動回路1は低圧端子の電圧VGNDをパワー素子Q2のゲートに供給してパワー素子Q2はオフする。入力信号INがオフ信号の場合に、スイッチング素子Q3はオンする。

(もっと読む)

ドライブ回路

【課題】トランスの補助巻線を用いることなく、制御回路の電源を確保して安価にできるドライブ回路を提供する。

【解決手段】ノーマリオン型のハイサイドスイッチQ1とノーマリオフ型のローサイドスイッチQ2との直列回路が直流電源に並列に接続され、ハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ回路であって、ハイサイドスイッチとローサイドスイッチとを制御信号によりオンオフさせる制御回路10と、ハイサイドスイッチとローサイドスイッチとの接続点に一端が接続された整流手段D2と、整流手段の他端と直流電源の一端とに接続され且つ制御回路に電源を供給するコンデンサC2と、制御回路からの制御信号とコンデンサからの電圧とに基づいてハイサイドスイッチとローサイドスイッチとをオンオフドライブするドライブ部A1,AND1,Q3,Q4とを備える。

(もっと読む)

電子式スイッチ

【課題】半導体スイッチング装置を制御する制御装置の動作用電力を負荷の形態にかかわらず安定に確保し、もって、負荷を安定に制御することが可能な電子式スイッチを提供する。

【解決手段】負荷8がLED電球のように負荷電流が小さく、第2の制御用電源装置15では制御装置9に十分な動作用電力を供給できない場合には、切換え装置16を操作して制御用電源装置10から制御装置9に給電可能にする。本体1の制御電力入力端子13、14に、外部の交流電源17からの給電線を接続する。

(もっと読む)

半導体装置

【課題】PVT変動に応じて動作駆動力を変更することが可能な、プリエンファシス動作をサポートするデータ出力回路を備える半導体装置を提供する。

【解決手段】インピーダンスコードPCODE<0:2>,NCODE<0:2>の変動に応じて値が調節されるプリエンファシスコードEM_PCODE<0:1>,EM_NCODE<0:1>を生成するコード生成部360と、出力データP_DATA,N_DATAを受信してデータ出力パッドDQに駆動し、インピーダンスコードに応じて駆動力が調節されるメイン駆動部311〜313,321〜323と、出力データを受信してデータ出力パッドに駆動し、プリエンファシスコードに応じて駆動力が調節される補助駆動部314〜315,324〜325とを備える。

(もっと読む)

受信回路、半導体装置、センサ装置

【課題】受信動作への切換時に発生するノイズを抑制する。

【解決手段】受信回路10は、圧電センサ2の受信信号SP及びSNを増幅するアンプ15と、圧電センサ2の一端とアンプ15の一端との間に並列接続されて受信動作への切換時に位相をずらしてオンされる複数のトランジスタ11a及び11b(ないしは12a及び12b)と、を有する。

(もっと読む)

電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法

【課題】電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法を提供する。

【解決手段】本発明の電力制御回路は、電源電圧とロジック回路との間に連結されてロジック回路への電源供給をスイッチングする回路であって、外部から並列的にモード転換信号を受信する複数の第1パワーゲーティングセルと、第1パワーゲーティングセルのうちの何れか1つと連結される少なくとも1つの第2パワーゲーティングセルと、第2パワーゲーティングセルと直列連結される複数の第3パワーゲーティングセルと、直列連結された複数の第3パワーゲーティングセルのうち、先端の第3パワーゲーティングセルと並列連結される複数の第4パワーゲーティングセルとを含み、モード転換信号は、第1パワーゲーティングセルのうちの何れか1つ、第2及び第3パワーゲーティングセルを経て第4パワーゲーティングセルに伝達され、第1ないし第4パワーゲーティングセルのそれぞれは、各自のセルに入力されるモード転換信号に応答して電源供給をスイッチングする。

(もっと読む)

パワーモジュール

【課題】制御電源電圧が低下した場合においても、半導体デバイスの熱破壊を防止することが可能なパワーモジュールを提供する。

【解決手段】パワーモジュール100は、半導体デバイス10のIGBT11を駆動する駆動回路20と、IGBT11のコレクタ電流がトリップレベルに達したときにIGBT11の保護動作を行う保護回路30と、駆動回路20に供給される制御電源電圧VDを検出する制御電源電圧検出回路40とを備える。保護回路30は、制御電源電圧VDが所定値よりも低くなると、センス抵抗を抵抗R1から抵抗R1,R2の直列回路に切り替えることで、トリップレベルを下げる。

(もっと読む)

液晶表示装置

【課題】動作を不安定にすることなく、各トランジスタの特性劣化を抑制することが可能

な半導体装置を提供することを課題とする。

【解決手段】非選択期間において、トランジスタが一定時間毎にオンすることで、シフト

レジスタ回路の出力端子に電源電位を供給する。そしてシフトレジスタ回路の出力端子は

、該トランジスタを介して電源電位が供給される。該トランジスタは非選択期間において

常時オンしていないので、該トランジスタのしきい値電位のシフトは、抑制される。また

、シフトレジスタ回路の出力端子は、該トランジスタを介して一定期間毎に電源電位が供

給される。そのため、シフトレジスタ回路は、ノイズが出力端子に発生することを抑制で

きる。

(もっと読む)

ゲート駆動回路および電力変換装置

【課題】P型電界効果トランジスタとN型電界効果トランジスタとが同時にオン状態になる期間内で発生する短絡電流に起因する消費電力の増大を抑制するともに、パワー素子を高速スイッチングさせることが可能なゲート駆動回路を提供する。

【解決手段】このゲート駆動回路11は、PchFET12と、NchFET13と、駆動信号が入力される入力側とPchFET12のゲート(G)およびNchFET13との間に設けられ、電源電位VCCに接続されているツェナーダイオード14およびツェナーダイオード15とを備え、ツェナーダイオード14および15は、PchFET12およびNchFET13のゲート(G)に印加される電圧を、PchFET12およびNchFET13のゲート(G)の閾値電圧側にシフトさせるように構成されている。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

1 - 20 / 795

[ Back to top ]