Fターム[5J056AA00]の内容

論理回路 (30,215) | 回路の種類 (3,583)

Fターム[5J056AA00]の下位に属するFターム

入力回路 (420)

論理演算回路 (504)

出力回路 (1,065)

インターフェース、レベルシフト、レベル変換 (1,016)

Fターム[5J056AA00]に分類される特許

1 - 20 / 578

半導体集積回路、半導体集積回路の制御方法

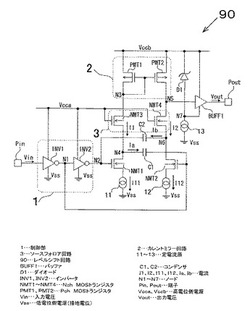

レベルシフト回路

【課題】レベルシフト回路を高速動作する。

【解決手段】一つの実施形態によれば、レベルシフト回路は、第一のトランジスタ、第二のトランジスタ、第一のコンデンサ、及び第二のコンデンサが設けられる。第一のトランジスタは、制御端子に入力電圧が入力される。第二のトランジスタは、制御端子に入力電圧の反転信号が入力される。第一のコンデンサは、一端が第一のトランジスタの第一の端子に接続され、他端に入力電圧の反転信号が入力され、入力電圧の立ち上りのときに電荷を蓄積して第一のトランジスタの第一の端子側から一端側へ第一の電流を発生する。第二のコンデンサは、一端が第二のトランジスタの第一の端子に接続され、他端に入力電圧が入力され、入力電圧の立ち下りのときに電荷を蓄積して第二のトランジスタの第一の端子側から一端側へ第二の電流を発生する。

(もっと読む)

半導体装置

【課題】半導体装置の回路ブロックへの電力供給復帰時に、無駄な充放電を削減すること。

【解決手段】半導体装置は、第1電源電圧を供給する第1電源線と、第1電源電圧よりも高い第2電源電圧を供給する第2電源線と、前段回路ブロックと、前段回路ブロックの出力信号に基づいて動作する後段回路ブロックと、前段回路ブロック及び後段回路ブロックに対する第1電源電圧及び第2電源電圧の供給を制御する電力供給制御回路と、を備える。電力供給制御回路は、後段回路ブロックへの第1電源電圧の供給開始タイミングを前段回路ブロックへの第1電源電圧の供給開始タイミングよりも遅延させる。更に、電力供給制御回路は、前段回路ブロック及び後段回路ブロックに第1電源電圧が供給された後に、第2電源電圧を前段回路ブロックと後段回路ブロックの両方に供給する。

(もっと読む)

省面積及び省電力のスタンダードセル方法

【課題】省面積及び省電力のための半導体集積回路の設計方法を提供する。

【解決手段】主回路217と適応電圧用調整回路を含む半導体集積回路であって、適応電圧調整用回路は、クロック信号を受け取るように構成された整合回路211と、整合回路211の出力を受け取り、また、クロック信号を受け取るように構成された位相検出器213と、電源電圧を増加又は減少させるように構成された電圧レギュレータ215とを含み、主回路217は電圧レギュレータ215から電源電圧を受け取るように構成され、整合回路211は電源電圧を受け取って、電源電圧における増加又は減少に基づいて、信号伝搬における遅延を調整するように構成される。

(もっと読む)

半導体装置

【課題】電源線と機能回路の間に電源スイッチとして接続されるMOSトランジスタのオン時のバックゲートの電圧を簡単な構造で調整することができる半導体装置を提供する。

【解決手段】一対の電源線2、3と、機能回路4a0〜4anと、一対の電源線2、3との少なくとも一方と機能回路4a0〜4anの間に接続されるスイッチング回路6a0〜6an、7a0〜7anとを有し、スイッチング回路6a0〜6an、7a0〜7anは、ソース/ドレインの一方が機能回路4a0〜4anに接続され、他方が前記一対の電源線2、3の一方に接続される第1のMOSトランジス11と、第1のMOSトランジスタ11のゲートとバックゲートを接続する抵抗素子12、21と、第1のMOSトランジスタ11のゲートに接続されるゲート電圧制御回路13と、を有する。

(もっと読む)

半導体装置及びその動作電源電圧制御方法

【課題】半導体装置及びその動作電源電圧制御方法を提供する。

【解決手段】動作電圧を可変とする複数の処理ユニットと、これら処理ユニットを制御するコントローラを有するLSIと、LSIからの処理ユニット毎に対応した電源供給の要求に応じて電源電圧を処理ユニットに供給する電源制御ユニットと、処理ユニット毎に電源制御ユニットに指示する電源電圧指示値を保持する書き換え可能な不揮発メモリと、を備え、コントローラは、処理ユニット毎に不揮発メモリに保持された電源電圧指示値を取得し、取得した電源電圧指示値を電源制御ユニットに転送する半導体装置。

(もっと読む)

電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法

【課題】電力制御回路、それを含む半導体装置及び該電力制御回路の動作方法を提供する。

【解決手段】本発明の電力制御回路は、電源電圧とロジック回路との間に連結されてロジック回路への電源供給をスイッチングする回路であって、外部から並列的にモード転換信号を受信する複数の第1パワーゲーティングセルと、第1パワーゲーティングセルのうちの何れか1つと連結される少なくとも1つの第2パワーゲーティングセルと、第2パワーゲーティングセルと直列連結される複数の第3パワーゲーティングセルと、直列連結された複数の第3パワーゲーティングセルのうち、先端の第3パワーゲーティングセルと並列連結される複数の第4パワーゲーティングセルとを含み、モード転換信号は、第1パワーゲーティングセルのうちの何れか1つ、第2及び第3パワーゲーティングセルを経て第4パワーゲーティングセルに伝達され、第1ないし第4パワーゲーティングセルのそれぞれは、各自のセルに入力されるモード転換信号に応答して電源供給をスイッチングする。

(もっと読む)

半導体集積回路

【課題】外部から印加された電圧のノイズを減少させて電圧を安定化させる半導体集積回路を提供する。

【解決手段】本発明は、電圧ノイズを減少させて電圧を安定化させる半導体集積回路において、第1電流が流れる第1内部回路と、第2電流が流れる第2内部回路と、前記第1電流のうちの一部と前記第2電流のうちの一部は第1接地パッドに流れ、残りの前記第1電流と残りの前記第2電流は第2接地パッドに流れるように構成された電圧安定化部とを含むことを特徴とする。

(もっと読む)

集積回路

【課題】集積回路において電力消費量を容易に低減する。

【解決手段】集積回路は、クロック分配回路、同期動作回路、論理回路、および、電源供給部を備える。クロック分配回路は、所定のタイミングを指示するクロック信号を分配する。同期動作回路は、クロック信号に同期して動作する。論理回路は、同期動作回路の動作結果に基づいて所定の論理演算を実行する。電源供給部は、クロック分配回路を駆動させるクロック分配回路駆動電圧より低い電圧を論理回路に論理回路駆動電圧として供給する。

(もっと読む)

半導体集積回路及びその電源制御方法

【課題】電源遮断状態からの復帰の際に、周辺回路の動作に影響を与えない半導体集積回路及び電源制御方法が、望まれる。

【解決手段】半導体集積回路は、第1及び第2の電源線と、サブ電源線と、第1の電源線とサブ電源線との間に配置される第1のスイッチ回路と、第2の電源線とサブ電源線との間に配置される論理回路と、第1の端子が第1の電源線と接続される容量素子と、容量素子の第1の端子の他方の第2の端子の接続を、第1の電源線、又は、サブ電源線、のいずれかに切り替える第2のスイッチ回路と、論理回路を非活性化状態から活性化状態に遷移させる場合に、第1のスイッチ回路により、第1の電源線及びサブ電源線の接続を遮断しつつ、第2のスイッチ回路により、第2の端子の接続を少なくても1回以上、サブ電源線に接続した後、第1の電源線に接続する制御回路と、を備えている。

(もっと読む)

集積回路装置

【課題】断熱動作を行う回路への電源電圧の供給を最適化することで好適な動作特性を実現する。

【解決手段】集積回路装置が、CPU10と電源生成回路40とを具備している。当該集積回路装置が高速モードに設定されると、電源生成回路40が直流の電源電圧をCPU10に供給する。この場合、CPU10は、通常のCMOS動作を行う。一方、当該集積回路装置が小電力モードに設定されると、電源生成回路40が交流の電源電圧をCPU10に供給する。CPU10は、複数の交流の電源電圧が供給されることで断熱動作を行う。該交流の電源電圧の少なくとも2つの電源電圧は、互いに、プルアップ及び/又はプルダウンのタイミングと、デューティ比とが異なっている。

(もっと読む)

補償装置および試験装置

【課題】消費電力を抑制する。

【解決手段】電源装置から印加された電源電圧により動作する対象回路の消費電流を補償する補償装置であって、電源装置から対象回路へと電源電圧を供給するための電源配線に接続され、電源配線に流れる電流を消費する電流消費部と、電流消費部に印加される電源電圧に応じて電流消費部により消費される電流を変化させる電流制御部と、電流消費部の基準電流量を変更する設定部と、を備え、設定部は、対象回路がスタンバイ状態において、基準電流量を低減する補償装置を提供する。

(もっと読む)

ディジタル信号処理回路及び車載用電子機器

【課題】ディジタル信号処理回路及び車載用電子機器において、消費電力を低減し、発熱量を低減する。

【解決手段】車載用電子機器に搭載されるディジタル信号処理回路は、クロック信号に同期して信号取込を行う入力段のフリップフロップ回路と、クロック信号に同期して信号取込を行う出力段のフリップフロップ回路と、順次処理を行う複数の組み合わせ回路が直列に接続されて構成されるとともに、クロック信号に同期して入力段のフリップフロップ回路から処理対象の信号が入力されて前記出力段のフリップフロップ回路に処理後の信号を出力する組み合わせ回路群と、クロック信号に同期して、組み合わせ回路毎に、クロック信号の1周期内において、駆動用電源の供給期間及び非供給期間を設けて駆動用電源の供給を行う電源供給回路と、を備える。

(もっと読む)

半導体装置

【課題】製造プロセスによる閾値電圧の変動に起因する歩留まりの悪化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、複数のトランジスタが並列に接続された所定並列回路と、複数のトランジスタのオンオフ状態を制御しつつ所定並列回路のインピーダンスが所定値になったかを検出し、該インピーダンスが所定値になったときの複数のトランジスタのオンオフ状態に応じた制御値を生成する制御値生成部と、電源電圧を生成する電圧発生部と、電源電圧で動作する動作トランジスタと、制御値に基づいて電源電圧を制御する制御部と、を含む。

(もっと読む)

ロジック回路及び携帯端末装置

【課題】DVDD系ロジック回路とRVDD系ロジック回路との間のアイソレートを実施しながら、小型化及び低コスト化を実現する。

【解決手段】第一のデジタル回路と第二のデジタル回路とを含むロジック回路であって、第一のデジタル回路の動作電圧である第一の電圧値を検出する第一の検出手段と、第二のデジタル回路の動作電圧である第二の電圧値を検出する第二の検出手段と、第一の電圧値と第二の電圧値とを比較する比較手段と、比較手段により得られた比較結果に応じて、第一のデジタル回路と第二のデジタル回路との間の分離結合を行う分離結合手段と、を含む。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを共振により出力する電圧出力回路100と、電圧出力回路100の発振を制御する発振制御回路210とを含む。発振制御回路210は、第1の電源電圧VPが出力されるノード及び第2の電源電圧VMが出力されるノードのいずれか一方のノードである第1のノードN1に接続される駆動回路220と、駆動回路220を制御する制御回路230とを含む。発振制御回路210は、制御信号SCに基づいて、第1、第2の電源電圧VP、VMの振幅を可変に制御する発振制御を行う。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを出力する電圧出力回路100と、制御信号SCに基づいて電圧出力回路100を制御する制御回路210と、第1の電源電圧VP及び第2の電源電圧VMに基づいて制御信号SCを生成して制御回路210に出力する制御信号生成回路240とを含み、制御回路210は、制御信号SCに基づいて、電圧出力回路100から出力される第1の電源電圧VP及び第2の電源電圧VMの振幅を可変に制御する。

(もっと読む)

レベルシフト回路

【課題】出力電圧の立ち上がりの遅延時間と立ち下がりの遅延時間との差異を低減することが可能なレベルシフト回路を提供する。

【解決手段】出力電圧の立ち上がりの遅延時間と出力電圧の立ち下がりの遅延時間とが互いに異なるレベルシフト部F1、F2が複数段接続されている。そして、前段のレベルシフト部F1の出力電圧の立ち下がりの遅延時間を後段のレベルシフト部F2の出力電圧の立ち上がりの遅延時間で補償し、前段のレベルシフト部F1の出力電圧の立ち上がりの遅延時間を後段のレベルシフト部F2の出力電圧の立ち下がりの遅延時間で補償する。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを出力する電圧出力回路100と、制御信号SCに基づいて電圧出力回路100を制御する制御回路210と、第1の電源電圧VP及び第2の電源電圧VMの少なくとも一方の振幅に応じて変化する制御信号SCを生成して制御回路210に出力する制御信号生成回路240とを含む。制御回路210は、制御信号SCに基づいて、電圧出力回路100から出力される第1の電源電圧VP及び第2の電源電圧VMの振幅を可変に制御する。

(もっと読む)

CMOS論理集積回路

【課題】異なる論理レベルの信号を高速に伝達可能なCMOS論理集積回路を提供する。

【解決手段】レベルシフト回路とCMOS論理回路とを備えたことを特徴とするCMOS論理集積回路が提供される。前記レベルシフト回路は、第1の低電位と前記第1の低電位よりも高い第1の高電位との間で変化する第1の論理レベルの信号を前記第1の低電位と前記第1の高電位よりも高い第2の高電位との間で変化する第2の論理レベルの信号に変換する。前記CMOS論理回路は、前記第1の論理レベルの第1の信号がゲートに入力される第1のNチャンネル形MOSFETと、前記第1のNチャンネル形MOSFETに直列に接続され前記第1の信号と反転関係にある前記第2の論理レベルの第2の信号がゲートに入力される第2のNチャンネル形MOSFETとを有する。

(もっと読む)

1 - 20 / 578

[ Back to top ]